Fターム[5J098AA16]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コイル、トランス (63)

Fターム[5J098AA16]の下位に属するFターム

可変コイル、可変トランス (4)

Fターム[5J098AA16]に分類される特許

1 - 20 / 59

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

分配回路、送信用フェーズドアレイアンテナ回路、合成回路及び受信用フェーズドアレイアンテナ回路

【課題】入力信号を複数の信号に低損失で分配することができる分配回路を提供することを課題とする。

【解決手段】分配回路は、信号入力ノードに直列接続される複数のインダクタ(401〜40n+1)と、入力容量を有する入力端子及び出力端子を有し、前記複数のインダクタのそれぞれの間に前記入力端子が接続され、前記入力端子に入力される信号を増幅して前記出力端子から出力する複数の増幅素子(421〜42n)と、前記複数の増幅素子の出力端子と複数の信号出力ノードとの間にそれぞれ接続される複数の整合回路(431〜43n)とを有する。

(もっと読む)

オーディオ用GIC回路

【課題】オーディオ用アクティブ型フィルター、特にGICフィルターにおいて遮断周波数以降で発生する特性劣化(遮断特性の跳ね返り)を2次LCフィルターの追加により補償する事、およびGICフィルターのピーキング特性を維持しながらGIC遮断限界以上で所定の遮断特性を実現する事。

【解決手段】2次LCフィルターの終端抵抗としてFDNR(Frequency Dependent Negative Resistors)を用いる事、およびLCフィルターと直列に制動抵抗(1)を接続する事で共振特性を備えた2次LCフィルターを実現しGIC遮断限界以上で所定の遮断特性を実現する。

(もっと読む)

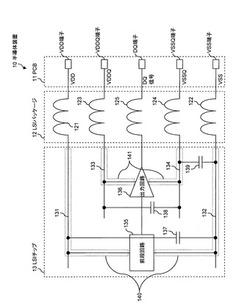

アイソレータ用回路基板、アイソレータおよびそれらの製造方法

【課題】コイルの設計の自由度の向上および小型化が可能でかつ容易に製造可能なアイソレータ用回路基板およびアイソレータならびにそれらの製造方法を提供することである。

【解決手段】回路基板10の上面にコイルCAが形成される。回路基板10の下面にコイルCBおよび配線パターンPBが形成される。回路基板20の上面にコイルCCが形成される。回路基板20の下面にコイルCDおよび配線パターンPDが形成される。複数のコイルCA,CB,CC、CDが互いに重なるように回路基板10,20が配置される。コイルCA,CB,CC,CDが送信チップ40および受信チップ50に重なるように回路基板10,20が送信チップ40上、受信チップ50上およびリードフレーム30上に配置される。

(もっと読む)

可変減衰器

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

磁気アイソレータ

【課題】 一様な外乱磁界の影響を除去しつつ、磁気アイソレータの小型化を図る。

【解決手段】 設置基板1上に設けられた第1の絶縁層2及び第2の絶縁層4と、第1の絶縁層2上に配置された第1の磁気抵抗効果素子3a、第2の磁気抵抗効果素子3b、第3の磁気抵抗効果素子3c及び第4の磁気抵抗効果素子3dと、第2の絶縁層2上に配置され、各磁気抵抗効果素子に対向して設けられた信号入力導体5aと、信号入力折返し導体5bとを信号入力接続線5cを介してミアンダライン状に接続されるよう構成された信号入力線5とを備え、信号入力線5に信号電流が通電されることにより第1の磁気抵抗効果素子3a及び第2の磁気抵抗効果素子3bに印加される磁界の方向と、第3の磁気抵抗効果素子3c及び第4の磁気抵抗効果素子3dに印加される磁界の方向とが、互いに逆方向となるように信号入力線5が構成されたことを特徴とする。

(もっと読む)

減衰器

【課題】減衰量の周波数依存性を改善することができる減衰器を提供すること。

【解決手段】減衰器10は、FET11〜13、インダクタ14及び15、抵抗16、入力端子17、出力端子18を備え、入力端子17には、FET11のドレイン電極と、FET12のドレイン電極と、インダクタ14の一方端とが接続され、出力端子18には、FET11のソース電極と、FET13のドレイン電極と、インダクタ15の一方端とが接続され、FET11のドレイン電極とソース電極との間にインダクタ14と、抵抗16と、インダクタ15とが直列に接続された構成を有する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路における信号のロスが生じても、通過すべき周波数の信号と他の周波数の信号との十分な強度比が得られるフィルタ回路を提供する。

【解決手段】信号線110に接続され、信号線110を伝搬する信号をフィルタリングするフィルタ回路を、信号線110ラインから信号を入力し、バッファリングするアンプ回路101と、アンプ回路101によってバッファリングされた信号をフィルタリングするノッチフィルタ108と、ノッチフィルタ108から出力された信号を入力し、入力された信号の周波数分布を反転させて信号線110に出力する−gm回路102と、によって構成する。

(もっと読む)

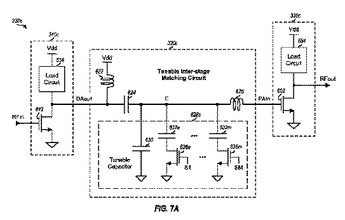

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

差動電流信号を単一終結信号に変換する回路

【課題】差動電流信号を単一終結信号に変換するミキサ回路を提供する。

【解決手段】多くの適用が差動電流信号の単一終結信号への変換を必要とする。存在しているアプローチで遭遇する欠点は、乏しい変換効率、制限された帯域幅、および大きなサイズを含む。開示された変換器は、小さなサイズおよび作動の広い帯域幅を有している高効率のユニットを得るために能動装置を使用する。

(もっと読む)

信号伝達装置

【課題】より簡素な構成でありながら、動作信頼性に優れる信号伝達装置を提供する。

【解決手段】入力信号電流が流れることにより入力信号磁場を生ずるプライマリコイル10と、バイアス電流が流れることによりバイアス磁場を生ずるバイアスコイル30と、センシング電流が流れることによりセルフバイアス磁場を生ずると共に、入力信号磁場、バイアス磁場およびセルフバイアス磁場に応じて抵抗変化を生ずるMR素子21A〜21Dを含む検出回路20とを備える。バイアス磁場およびセルフバイアス磁場は、MR素子21A〜21Dにおける磁化自由層に対して同じ方向に印加される。よって、セルフバイアス磁場がバイアス磁場と同様の機能を発揮する。これらのバイアス磁場およびセルフバイアス磁場により、検出回路20の動作安定性が向上する。

(もっと読む)

磁気結合型アイソレータ

【課題】 特に、磁気検出素子と平面コイル間の絶縁性の低下を抑制でき、また、1次側回路と2次側回路間の静電容量Cを従来よりも小さくすることで、より高速伝送できる磁気結合型アイソレータを提供することを目的としている。

【解決手段】 入力信号により外部磁界を発生させるための巻回された平面コイル2と、前記外部磁界を検出して電気信号に変換するための磁気検出素子R1〜R4と、前記平面コイル2と前記磁気検出素子R1〜R4の間に介在する絶縁層30と、を有する。前記磁気検出素子R1〜R4は、前記平面コイル2の側方に位置している。

(もっと読む)

電力分配回路

【課題】小面積及び/又は低損失の電力分配回路を提供する。

【解決手段】入力端子に交流信号を入力することにより磁束を生成する1次側コイル221と、第1の出力端子及び第2の出力端子間に接続され、前記1次側コイルにより生成された磁束により第1の交流信号を生成する第1の2次側コイル231と、第3の出力端子及び第4の出力端子間に接続され、前記1次側コイルにより生成された磁束により第2の交流信号を生成する第2の2次側コイル232とを有し、前記第1の2次側コイル231及び前記第2の2次側コイル232は、前記第1の出力端子、前記第2の出力端子、前記第3の出力端子及び前記第4の出力端子から2組の差動信号を出力する電力分配回路。

(もっと読む)

サーキュレータ

【課題】アイソレーション特性に優れたサーキュレータを実現すること

【解決手段】ポート2に接続されたアンテナ19とダミー負荷15はともに50Ωである。分配回路10の入力端であるポート1に入力された信号は、逆相で等振幅に分配され、一方は第1ベース接地増幅器11、第1整合回路16、第3ベース接地増幅器13を介して合成器18に入力され、他方は第2ベース接地増幅器12、第2整合回路17、第4ベース接地増幅器14を介して合成器に入力される。ここで、アンテナ19のインピーダンスの変動は、第2ベース接地増幅器12の電流源の電流量と、第2整合回路17の並列可変キャパシタ119のキャパシタンスとを制御することで補償することができる。そのため、合成器18において第3ベース接地増幅器13の出力と第4ベース接地増幅器14との出力は打ち消され、ポート3からは出力されない。

(もっと読む)

移相器

【課題】意図せずに信号線に付加される線路によって移相器の特性が劣化してしまうこと。

【解決手段】移相器50は、LPFとHPF間の切替に基づいて入力信号を移相する。移相器50は、入力端子1と出力端子2間に接続されたFET5と、FET5がオン状態のとき共振する共振回路と、FET5がオン状態のとき、入力端子1及び出力端子2間に形成される信号線路に含まれる節点と共振回路との間に接続される付加線路4a(4b)と、FET5がオン状態のとき、信号線路の一部に含まれ、少なくとも付加線路4a(4b)と共にローパスフィルタを形成するインダクタ3a(3b)と、を備える。FET5がオン状態のときに付加線路と共にLPFを形成するインダクタを信号線路に配置する。これによって、意図しない付加線路によって移相器の特性が劣化することを抑制することができる。

(もっと読む)

周波数特性調整回路、受信インタフェース回路および磁気記憶装置

【課題】伝送路との整合を保持しながら交流結合回路による低域側遮断域を変化させる。

【解決手段】周波数特性調整回路20の遮断域調整部21は、AC結合回路10の周波数特性における低域側遮断域が移動するように、AC結合回路10からの出力信号を通過させる。遮断域調整部21の零点周波数および極周波数は、制御信号に応じて設定される。この制御信号により、遮断域調整部21の伝達関数の分子多項式が、AC結合回路10の伝達関数の分母多項式と等しくされ、遮断域調整部21の零点周波数が、AC結合回路10による低域遮断周波数に合わせられる。このため、AC結合回路10から遮断域調整部21を通過した出力信号は、AC結合回路10により生じた低域遮断域が移動した周波数特性を有するようになる。そして、この周波数特性において、制御信号に応じて設定される遮断域調整部21の極周波数が、移動後の低域側遮断域の遮断周波数となる。

(もっと読む)

アイソレータ用回路基板、アイソレータおよびアイソレータの製造方法

【課題】製造工程が簡略化されたアイソレータ用回路基板、アイソレータおよびアイソレータの製造方法を提供する。

【解決手段】ベース絶縁層1の上面および下面に金属層M1,M2がそれぞれ形成されている。金属層M1は、コイル2、複数の接続パッド3および複数の接続パッド4を含む。金属層M2は、コイル5および接続パッド6,7を含む。ベース絶縁層1には、貫通孔1a,1bが形成される。接続パッド3上に実装される受信チップ11の端子部11aがワイヤW1を介してベース絶縁層1の貫通孔1a内で露出する接続パッド6の部分にボンディングされ、端子部11bがワイヤW2を介してベース絶縁層1の貫通孔1b内で露出する接続パッド7の部分にボンディングされる。

(もっと読む)

インピーダンス整合装置、およびインピーダンス整合方法

【課題】インピーダンス整合における制御不能を防ぐ。

【解決手段】インピーダンス整合装置は、高周波電源と負荷とのインピーダンスを整合するインピーダンス整合装置において、高周波電源と負荷との間にインピーダンス可変素子を設けたインピーダンス整合回路と、このインピーダンス整合回路のインピーダンス可変素子のインピーダンス値を変更することによって、インピーダンス整合回路の入力インピーダンスの絶対値と、電圧と電流の位相差とをそれぞれの目標値に制御することによってインピーダンス整合を行うインピーダンス制御部と備える。シーク制御とフォローイング制御とを組み合わせてインピーダンス整合することで、インピーダンス整合における制御不能を防ぐ。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

半導体集積回路

【課題】 内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】 半導体集積回路は校正回路200を具備して、内蔵容量70:151は、複数の容量およびスイッチを有する。V・I変換器20、30は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の充電または放電の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧とを比較する。校正動作の間に複数回の時間積分と複数回の電圧比較が順次に実行されて、順次に生成される複数回の電圧比較の結果はラッチ90に順次に格納される。校正動作の完了時点のラッチの格納結果に従って、内蔵容量70:151の複数のスイッチの各オン・オフ制御と内蔵フィルタ150の周波数特性とが決定される。V・I変換器は、スイッチ素子SW0を含む。内蔵容量70:151の複数のスイッチとV・I変換器のスイッチ素子は、MOSトランジスタである。

(もっと読む)

1 - 20 / 59

[ Back to top ]