Fターム[5J098AC22]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変要素 (423) | 可変電流源 (22)

Fターム[5J098AC22]に分類される特許

1 - 20 / 22

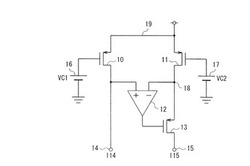

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

フィルタ回路

【課題】高速に動作することが可能であり、周波数特性制御するためのフィルタ制御信号生成回路が小規模でしかも設計に要する時間が短時間で済むようなフィルタ回路を提供する。

【解決手段】Gm−Cフィルタのフィルタ制御信号生成回路を、MOSトランジスタ32、MOSトランジスタ32とゲート同士が接続されるMOSトランジスタ33、MOSトランジスタ32とドレイン同士が接続されるMOSトランジスタ30、ドレインとゲートが接続され、MOSトランジスタ30とゲート同士が接続され、MOSトランジスタ33とドレイン同士が接続されるMOSトランジスタ31、MOSトランジスタ30〜33のうちの1つのソースに接続される抵抗素子34によって構成し、MOSトランジスタ33,30のドレインに接続される出力端子35または出力端子36からフィルタ制御信号を出力させる。

(もっと読む)

フィルタユニット及び移動体通信端末試験システム

【課題】移動体通信用の周波数帯域おいて、仕様の追加・変更に柔軟に対応可能な帯域阻止フィルタフィルタを提供する。

【解決手段】それぞれ互いに直列に接続され、かつそれぞれがYIG素子を有して同調周波数を可変可能にされ、それぞれの該同調周波数(f1,f2)を中心とした所定帯域幅(ΔBW1,ΔBW2)内にある所望の信号を減衰させるための、第1の可変フィルタ(102)及び第2の可変フィルタ(103)とを備え、前記所望の信号が低周波数帯域側にある場合、前記同調周波数(f1)と前記同調周波数(f2)とが互いに同一又は近傍に設定するように制御され、高周波数帯域側にある場合、前記所定帯域幅(ΔBW1)と前記所定帯域幅(ΔBW2)とを、いずれか一方の周波数帯域幅より広くなるように連結させかつ連結した帯域が前記所望の信号を包含するように前記同調周波数(f1)及び前記同調周波数(f2)が制御される。

(もっと読む)

抵抗増倍回路

【課題】チップ面積の増大を招くことなく、半導体材料に起因するhfeのばらつきなどに影響されることのない安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に抵抗器3の一端が接続され、抵抗器3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、抵抗器3の他端に接続されて、信号入力端子8から見た抵抗器3の見かけ上の抵抗値が1/(1+N)倍に見えるものとなっている。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

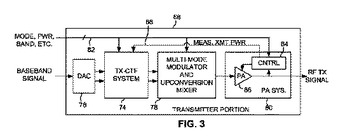

プログラム可能送信連続時間フィルタ

プログラム可能電流の送信連続時間フィルタ(TX−CTF)システムは無線周波数(RF)送信機に含まれ得る。TX−CTFの入力はベースバンド送信信号を受信することができ、TX−CTFの出力はアップコンバージョンミキサに供給されて、送信用のRFに変換され得る。TX−CTFは、フィルタパラメータをともに規定する増幅回路および受動回路を含む。TX−CTFはさらに、プログラム可能バイアス電流を増幅回路に供給するプログラム可能電流回路を含む。TX−CTFシステムはまた、1つ以上の送信機制御信号を受信し、これに応じて、TX−CTFに供給されるバイアス電流を制御する信号を生成する制御論理を含む。  (もっと読む)

(もっと読む)

フィルタ回路、連続時間フィルタ及び信号再生装置

【課題】周波数帯域を制限するフィルタ回路に関し、周波数とは、独立に利得を調整する。

【解決手段】第1の電圧/電流変換回路(12)に、係数設定回路(16)からの第1の制御信号と利得調整のための第2の制御信号とから作成した第3の信号を入力し、第2の電圧/電流変換回路(14)に、第1の制御信号を入力する。このため、周波数と、利得を独立に制御したフィルタを実現できる。

(もっと読む)

移相回路

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

プリエンファシス回路

【課題】 簡単な構成でプリエンファシス信号を生成することが可能なプリエンファシス回路を実現する。

【解決手段】 信号の変化点で振幅を大きくするプリエンファシス回路において、差動入力信号を差動電流出力に変換する第1のトランスコンダクタンスアンプと、ハイパスフィルタ回路と、このハイパスフィルタ回路を介した前記差動入力信号を差動電流出力に変換する第2のトランスコンダクタンスアンプと、2つの前記差動電流出力をそれぞれ加算して電圧変換する第1及び第2の抵抗とを設ける。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が小さく低消費電力の広帯域RF信号処理回路を提供すること。

【解決手段】半導体集積回路は、第1制御端子101の第1制御信号Vc1により制御可能なキャパシタンスCRを有する第1キャパシタ1と、第2制御端子102の第2制御信号Vc2により制御可能なキャパシタンスCLを有する第2キャパシタ3を含み等価的にインダクタLをエミュレートするジャイレータ2、5とからなる共振回路を半導体チップに具備する。キャパシタンスCRとインダクタLは、並列共振回路を構成する。並列共振周波数を変更する際に、第1と第2のキャパシタ1、3のキャパシタンスを協調的に変更する。並列共振回路は増幅素子Q1の出力電極に接続されるアクティブ負荷に好適である。

(もっと読む)

マルチバイブレータ型発振回路

【課題】2次以降の高調波を低減させた低歪の正弦波出力が得られ、また発振周波数を変えた場合でも、基本波を減衰させることなく、低歪の正弦波出力が得られるようにする。

【解決手段】マルチバイブレータ回路10を有するマルチバイブレータ型発振回路で、マルチバイブレータ回路10の出力側に、その出力電圧波形の高調波を低減する第1及び第2の電流可変(n次)フィルタ回路20,22を接続し、このフィルタ回路20,22により、高調波を減衰させた低歪の正弦波出力を得る。また、マルチバイブレータ回路10の発振周波数設定用のバイアス電流Ix2,Ix3と連動する連動電流をトランジスタQ17,Q18にて抽出し、この連動電流によって、上記フィルタ回路20,22のカットオフ周波数を変化させ、基本波の減衰をなくす。

(もっと読む)

遅延回路

【課題】消費電力を低減し、かつ生成する遅延時間の誤差を縮小し得る遅延回路を提供する。

【解決手段】単位遅延時間のほぼ2倍の遅延時間を生成する複数の第一の遅延ユニットY1〜Y16と、単位遅延時間を生成する第二の遅延ユニットX1と、第一の遅延ユニットを直列に接続し、終段の第一の遅延ユニットY16に第二の遅延ユニットX1を接続することと、初段の第一の遅延ユニットY1に外部入力信号Dinを入力するとともに、各第一の遅延ユニットと第二の遅延ユニットには外部入力信号Dinを入力することと、第一の遅延ユニット及び第二の遅延ユニットは、前段の遅延ユニットの出力信号と外部入力信号のいずれかを遅延させて出力するスイッチ回路を備えることと、終段の第一の遅延ユニットY16の出力信号と第二の遅延ユニットX1の出力信号のいずれかを選択するセレクタ2とを備えた。

(もっと読む)

全差動増幅器

【課題】低電源電圧で動作可能で、同相信号抑圧機能を備える全差動増幅器の実現。

【解決手段】1段構成の反転増幅器41-48,41'-48'で構成され、入力側の同相信号をフィードフォワード手段によって打ち消すように構成された第1の全差動増幅器200(100,101)と、1段構成の反転増幅器51-58で構成され、出力側の同相信号をフィードバック手段によって打ち消すように構成された第2の全差動増幅器201(102)と、を備え、第1の全差動増幅器200の出力が、第2の全差動増幅器201の入力に接続されている。

(もっと読む)

負荷回路及びこれを用いた同調回路

【課題】同調回路の同調周波数を大きく変化させても、同調周波数に対し負性抵抗の値を調整する回路が不要で、かつ常に帯域一定で利得一定の特性を持つ同調回路に用いる負荷回路を提供する。

【解決手段】同調回路に用いる本発明の負荷回路10は、インダクタ14と、上記インダクタ14に直列に接続され、上記インダクタ14の直列抵抗成分を打ち消し、インダクタのQを増大させるための負性抵抗回路12とを備える。上記構成の上記負荷回路10を用いて同調回路を構成すると、インダクタ14のもつQよりも、Qの高い同調回路が実現でき、かつ同調周波数を大きく変化させても、常に一定の帯域で利得一定の特性を持つ同調回路を構成できる。

(もっと読む)

段間フィルタとこれを用いた無線機

【課題】インダクタを削除して占有面積を減らし半導体集積回路を小型化し、かつインダクタの削除による相互変調歪を劣化させることなく確保する。

【解決手段】第1の電子回路1および第2の電子回路2の入出力端子を接続した端子間に容量5の一端を接続し、この容量5の他端をアクティブインダクタ回路10の入力端に接続し、また出力端をGNDに接続する。このアクティブインダクタ回路10は、容量5の他端にバイポーラトランジスタ6のエミッタ端子、ベース端子に抵抗7の一端を接続し、またコレクタ端子と抵抗7の他端を電源に接続して、さらにエミッタ端子には、他端をGNDに接続した電流源8の一端を接続し構成する。バイポーラトランジスタ6等の能動素子と容量5等の受動素子を組み合わせてインダクタ相当の特性を持つ構成として、相互変調歪を劣化させる高調波成分をバンドリジェクションすることで相互変調歪を確保する。

(もっと読む)

可変トランスコンダクタ

【課題】トランスコンダクタンスの可変域を拡大又は維持しつつ出力端子の寄生容量を低減する。

【解決手段】2つの入力回路10,60が平方根圧縮回路20と電圧電流変換回路30とを共有するように構成する。また、電圧電流変換回路30を構成する差動MOSトランジスタM5及びM6の出力部において、固定バイアス電流Ibiasを電流源41,42で引き抜き、同時にM5及びM6の可変駆動電流と同一の可変バイアス電流Ibを電流源51,52から供給することで、出力バイアス回路40の電流が固定バイアス電流Ibiasと常に等しくなるようにする。更に、電圧電流変換回路30と出力バイアス回路40との間に、カスコード接続のMOSトランジスタM9及びM10からなる電流バッファ50を挿入する。

(もっと読む)

電源補償電圧および電流源

【課題】電源補償電圧または電流を供給する装置および方法を提供する。

【解決手段】電源補償電流および電圧源は、バンドギャップ基準電圧およびスケールされた電源電圧に接続された差動増幅器106を利用する。電源が変動すると、差動増幅器が安定した補償出力を調整する。出力は補償電圧でも電流でもよい。さらに、差動増幅器から複数の電流および電圧が参照されてもよい。安定した補償出力は、外部回路のための基準バイアスとして供給されてもよい。さらに、補償出力は、電圧制御発振器に供給されてもよい。電源補償電圧および電流源は、電源電圧が第1および第2の抵抗器102に跨って分配される、基準ノード122で第2の抵抗器と直列に接続された第1の抵抗器と、電圧基準電源104と、第1および第2の電圧入力および補償出力を有し、前記第1の入力が前記基準ノードに接続され、前記第2の入力が前記電圧基準電源に接続される差動増幅器と、を備える。

(もっと読む)

広い周波数範囲にわたり安定した利得を有する電圧制御発振器

【課題】VCOにおいて広い周波数範囲にわたり安定した利得を与える装置及び方法を提供する。

【解決手段】VCOは、波形発生器を、周波数選択入力を有するバイアス発生器と共に用いる。周波数選択入力を用いて、バイアス発生器の出力電流及び/又は利得の量を調整する。バイアス発生器の出力電流は、波形発生器の出力の周波数を決定する。複数のバイアス及び波形の発生器を用いて、VCOの周波数範囲を拡大できる。PLLは、VCOの周波数選択入力を用いることにより様々な出力周波数のためにプログラムできる。

(もっと読む)

クロック信号発生回路

【課題】スイッチドキャパシタ回路の高速化の際に、スイッチドキャパシタ回路を動作させるために供給するクロックタイミングがばらつきや配線に付く寄生抵抗、容量によってはタイミング破綻を引き起こす。

【解決手段】スイッチドキャパシタ回路を動作させるために供給するクロック信号のボトムプレートサンプリング期間と、ノンオーバーラップ期間を制御手段により、タイミングを調整可能にする事により、タイミング破綻を回避する事が出来、且つ前記それぞれの期間を決定付ける論理素子の面積を増大させる事なく構成できる。

(もっと読む)

制御可能なフィルタ装置

【課題】入力信号をフィルタするためのフィルタ回路網と、トランジスタとを具備する制御可能なフィルタ装置を提供する。

【解決手段】上記トランジスタは制御可能なDCトランジスタ出力電流を提供するための制御可能な電流源を出力回路に有する電圧ホロワとして構成され、この電圧ホロワの出力端子は、フィルタ装置のカットオフ周波数が上記電流源によって供給されるDC電流の変動により制御できるように、フィルタ回路網に接続される。フィルタ回路網は単極のRC回路網でよく、現存のコンデンサと抵抗との接続点に結合されるこの回路網の追加のコンデンサ(又は抵抗)に電圧ホロワの出力を接続する。このフィルタ装置は、追加のコンデンサ(又は抵抗)が事実上電圧ホロワによって駆動されるか否かに依存して、2つの値のカットオフ周波数間で制御可能であり、或いは電流源によって提供される電流の値に依存して、ある範囲のカットオフ周波数にわたり連続的に制御することができる。

(もっと読む)

1 - 20 / 22

[ Back to top ]