Fターム[5J098AD05]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 特性の安定化、信頼性の向上 (78)

Fターム[5J098AD05]の下位に属するFターム

温度の影響軽減 (17)

電源電圧変動の影響軽減 (5)

経年変化の補償 (1)

過電圧、過電流に対する保護 (4)

誤動作の防止 (4)

Fターム[5J098AD05]に分類される特許

1 - 20 / 47

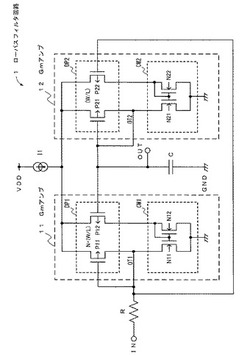

ローパスフィルタ回路

【課題】能動素子に発生するオフセット電圧の影響を少なくすることのできるローパスフィルタ回路を提供する。

【解決手段】実施形態のローパスフィルタ回路1は、抵抗Rと、一端が接地端子に接続されたキャパシタCと、Gmアンプ11と、Gmアンプ12とを備える。Gmアンプ11は、非反転入力端子にキャパシタCの他端が接続され反転入力端子に自身の出力端子OT1が接続された入力差動対DP1を有し、出力端子OT1に抵抗Rが接続される。Gmアンプ12は、非反転入力端子にGmアンプ11の出力端子OT1が接続され反転入力端子に自身の出力端子OT2が接続された入力差動対DP2を有し、出力端子OT2にキャパシタCの他端が接続される。

(もっと読む)

アクティブフィルタ

【課題】フィルタのQ値が変動することがないアクティブフィルタを提供する。

【解決手段】位相容量素子を含む演算増幅器、フィルタ用抵抗素子、フィルタ用容量素子、バイアス回路を含むアクティブフィルタにおいて、バイアス回路を、ゲート同士が接続されるMOSTr41、42、MOSTr41とドレイン同士が接続されるMOSTr43、MOSTr44とゲート同士が接続され、MOSTr42とドレイン同士が接続されるMOSTr44、MOSTr41またはMOSTr42のうちのいずれか1つのソースに接続される抵抗素子45、MOSTr41のドレインに接続される出力端子46またはMOSTr44のドレインに接続される出力端子47によって構成し、抵抗素子45を、フィルタ用抵抗素子と同じプロセス条件で製造し、位相補償容量素子をフィルタ用容量素子と同じプロセス条件で製造する。

(もっと読む)

適応ノッチフィルタ、及びノッチフィルタのパラメタ調整方法

【課題】制御帯域を広げたときに生じる振動周波数成分を抑制するよう自動的にノッチフィルタを調整する。

【解決手段】適応ノッチフィルタは、共振が生じ得る制御対象への制御入力を生成するための信号に含まれる当該制御対象の固有振動数成分を抑制するためのノッチフィルタと、ノッチフィルタの中心周波数及びノッチ幅を含むパラメタを調整するためのパラメタ調整部と、を備える。パラメタ調整部は、制御対象の制御帯域を広げたときに生じた振動周波数成分とノッチフィルタの中心周波数との関係に応じて、調整されるべきノッチフィルタのパラメタを選択する。

(もっと読む)

減衰器

【課題】減衰量の周波数依存性を改善することができる減衰器を提供すること。

【解決手段】減衰器10は、FET11〜13、インダクタ14及び15、抵抗16、入力端子17、出力端子18を備え、入力端子17には、FET11のドレイン電極と、FET12のドレイン電極と、インダクタ14の一方端とが接続され、出力端子18には、FET11のソース電極と、FET13のドレイン電極と、インダクタ15の一方端とが接続され、FET11のドレイン電極とソース電極との間にインダクタ14と、抵抗16と、インダクタ15とが直列に接続された構成を有する。

(もっと読む)

高インピーダンス回路、フィルタ回路及び増幅回路

【課題】従来技術の高インピーダンス回路は、温度変化等の影響を受けて、高いインピーダンスを維持することができないという問題があった。

【解決手段】本発明にかかる高インピーダンス回路は、ダイオード接続されたトランジスタ21,22を備え、トランジスタ21のバックゲートとトランジスタ22のソースとが接続され、トランジスタ22のバックゲートとトランジスタ21のソースとが接続される。このような回路構成により、温度変化等の影響を抑え、高いインピーダンスを維持することができる。

(もっと読む)

通信システム、車載通信装置及び分岐コネクタ

【課題】電力線を介した通信に関し、利得低下の防止及び伝送品質の低下を防止を実現することができる通信システムを提供する。

【解決手段】バッテリ4からの電力を供給するための電力線3がECU1,1,…及びアクチュエータ2,2,…に接続し、ECU1,1,…及びアクチュエータ2,2,…は夫々電力線3から電力の供給を受けると共に、電力線3を介して通信を行なう。ECU1,1,…及びアクチュエータ2,2,…は、電力線3の分岐点31からの分岐に夫々接続される。分岐点31に、負性インピーダンス変換回路5の一端を接続し、他端を固定電位に接続する。

(もっと読む)

遅延回路及び電圧制御発振回路

【課題】電源ノイズにより遅延時間が影響を受けにくい遅延回路及び遅延回路を用いた電圧制御発振回路を提供する。

【解決手段】第1及び第2の電源端子と一対の差動信号入力端子と一対の差動信号出力端子とを備え、一対の差動信号入力端子から入力した信号を遅延させて一対の差動信号出力端子から出力する遅延部と、電流制御端子により制御された電源電流を遅延部の第1の電源端子と第2の電源端子との間に流すように制御する電流制御部と、第1及び第2の電源端子の電圧が一定の電圧になるように制御する電圧制御部と、を備える。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

フィルタ回路及び通信装置

【課題】電荷の移動に伴う過渡現象が出力に与える影響を抑止すること。

【解決手段】入力端に入力された電圧信号を電流信号に変換するトランスコンダクタンスアンプ102と、複数のキャパシタから構成され、トランスコンダクタンスアンプ102から出力された電流信号が周期毎に各キャパシタへ順次に入力されるキャパシタ集合体と、電流信号が入力された1群のキャパシタを互いに接続し、当該1群のキャパシタに蓄積された電荷を加算するシェアスイッチS1aS〜S4aS,S1bS〜S4bSと、シェアスイッチS1aS〜S4aS,S1bS〜S4bSにより電荷が加算された後、1群のキャパシタのうちの少なくとも1つのキャパシタを出力端に接続するダンプスイッチS1aD〜S4aDと、を備える。

(もっと読む)

フィルタ回路

【課題】高速でかつ低消費電流であり、MOSトランジスタのしきい値電圧の絶対値が低い場合でも入力信号レベルを大きくすることができるフィルタ回路を提供する。

【解決手段】ゲートから信号を入力するMOSトランジスタ(Tr)1、Tr2、ドレインがMOSトランジスタ1のソースに接続され、ゲートがMOSトランジスタ2のソースに接続されるTr3、ドレインがTr2のソースに接続され、ゲートがTr1のソースに接続されるTr4、Tr3のソースに電流を供給する電流源5、Tr4のソースに電流を供給する電流源6、Tr1〜Tr4のソースの各々に接続されるコンデンサ7、8を含むフィルタ回路に、Tr3、Tr4の動作点が飽和領域内の線形領域に近い側から遠い側に向かう方向にシフトするように電圧を印加する電圧源101、102を設ける。

(もっと読む)

フィルタ回路および通信装置

【課題】フライングキャパシタを備え、急峻な減衰特性を備えた上でさらにQ値を可変にすることが可能なフィルタ回路の提供。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタCh1と、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタCh2と、を備え、フライングキャパシタは、出力端から入力端へ切り替わってから所定の時間遅延して入力端から出力端へ切り替わり、入力端から出力端へ切り替わってから所定の時間遅延して出力端から入力端へ切り替わる、フィルタ回路。

(もっと読む)

アクティブフィルタの設計

【課題】LCフィルタをシミュレートすることで低素子感度フィルタの実現を可能にするアクティブ低域フィルタ回路を提供する。

【解決手段】信号入力端子から直列に複数個の抵抗Rを接続し、信号入力端子側からの各抵抗の接続点に順次演算増幅器A1、・・・・An−1の非反転入力端、出力端、反転入力端の順に接続し、各演算増幅器の非反転入力端と接地間に従来のLCフィルタの設計法を用いて求めた値のコンデンサC1、・・・・Cn、および演算増幅器の非反転入力端間にC1,3、・・・・Cn−1,nを接続し、前記の直列に接続された複数個の抵抗Rの最終端から出力信号を取り出す。

(もっと読む)

フィルタ回路

【課題】平滑用コンデンサに対する充電電流及び放電電流による時定数を大きくした場合であっても、平滑用コンデンサの体格の大型化や、オフセット電圧の増加を抑制することが可能なフィルタ回路を提供する。

【解決手段】入力電圧とフィルタ処理電圧との電圧差に応じた電流を、カスコード型カレントミラー回路を利用して減衰させて、平滑用コンデンサC1の放電電流I11及び放電電流I12を発生させる。さらに、平滑用コンデンサC1の充電電流I12の一部となるベース電流Ib1’を流すトランジスタT23を、トランジスタT24と抵抗R13,R14からなる回路により、フィルタ回路10の後段回路と分離する。

(もっと読む)

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

無線受信機用半導体装置

【課題】マルチバンド無線受信機のバンドパスフィルタを集積回路で構成する場合に、回路規模が大きくなり、チップ面積が大きくなったり、製造コストが高くなる。

【解決手段】混合回路58は無線受信信号SRFをダウンコンバートして中間信号SIFを生成する。IFBPF60は、抵抗R及びキャパシタCを用いたRCアクティブフィルタで構成され、SIFから目的受信信号を抽出する。抵抗Rは、クロック信号SCLによって駆動されるスイッチトキャパシタからなる等価抵抗により構成される。SCLを生成するフィルタ制御クロック生成回路72は、SCLの周波数fCLを、目的受信信号が属するバンドに応じて切り換えることができる。IFBPF60の通過帯域は、クロック周波数fCLによる抵抗Rの等価抵抗値の切り換えにより、受信バンドに対応して変更できる。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

パルス伸長回路及び半導体装置

【課題】幅のより短いパルスに対して伸長が可能なパルス伸長回路及び半導体装置を提供する。

【解決手段】それぞれのソースが定電流源21を介して電源端子5に接続され、それぞれのドレインが定電流源21より電流駆動能力の大きな定電流源22を介して接地端子6に接続され、ゲートが入力端子27に接続されたp‐MOSトランジスタP1及びゲートが出力端子28に接続されたp‐MOSトランジスタP2と、一端がp‐MOSトランジスタP1、P2のソースと定電流源21との間に接続され、他端が接地端子6に接続されたキャパシタC1と、ドレインがp‐MOSトランジスタP2のゲートに接続され、且つ定電流源23を介して電源端子5に接続され、ソースが接地端子6に接続され、ゲートがp‐MOSトランジスタP1、P2のドレインと定電流源22との間に接続されたn‐MOSトランジスタN1とを備える。

(もっと読む)

アクテイブバンドパスフィルタ及び磁気記憶装置

【課題】中心周波数と独立に、帯域幅を調整するアクテイブバンドパスフィルタに関し、帯域幅の調整が容易で、且つ回路構成を簡単化する。

【解決手段】帯域通過ブロック(1)と、帯域通過ブロック(1)と等しい分母多項式を持つ2次の帯域阻止ブロック(2)と、帯域阻止ブロック(2)の出力を増幅する増幅ブロック(3)との直列接続回路で、負帰還回路を構成する。増幅ブロック(3)の増幅度により、帯域幅を、周波数と独立に制御でき、調整が容易で、且つ回路構成も簡単化できる。

(もっと読む)

キャパシタンス乗算器回路

キャパシタンス乗算器回路が、追加の回路を追加することまたは追加の電力を必要とすることなしにキャパシタンス乗算器効果を達成するために、回路のRCフィルタ中のキャパシタを通る電流を検知し、その電流を乗算するように構成される。回路は、RCフィルタと、フィルタ出力に接続された第1の信号経路と、フィルタに入力に接続された第2の信号経路とを含む。フィルタを通る電流出力(iout)は、2つの経路に分割され、第1の経路において検知され、第2の経路において乗算される。乗算された電流は、キャパシタCの実効キャパシタンスを上げるために第2の経路からフィルタ入力にフィードバックされる。キャパシタンス乗算器回路は、フィルタ中のキャパシタの実効キャパシタンスを上げる際に、全体的な回路の周波数応答、直線性性能および/または安定性に影響を及ぼさない。  (もっと読む)

(もっと読む)

インピーダンス調整回路およびインピーダンス調整方法

【課題】インピーダンスを十分な精度で調整する。

【解決手段】一端を電源Vddに接続する抵抗11、12のそれぞれの他端をそれぞれ接続する端子13、14と、一端をスイッチ素子17を介して端子13に接続し他端を接地する可変抵抗素子19と、一端をスイッチ素子18を介して端子14に接続し他端を可変抵抗素子19の一端に接続する可変抵抗素子20とを備える。スイッチ素子17をオンとし、スイッチ素子18をオフとし、可変抵抗素子19の一端の電位が基準電圧となるように可変抵抗素子19の抵抗値を調整し、調整された可変抵抗素子19の抵抗値を維持して、スイッチ素子17をオフとし、スイッチ素子18をオンとし、可変抵抗素子20の一端の電位が基準電圧となるように可変抵抗素子20の抵抗値を調整する。

(もっと読む)

1 - 20 / 47

[ Back to top ]