Fターム[5J106CC20]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 複数の発振回路・VCO (166) | 複数のループVCO (43)

Fターム[5J106CC20]に分類される特許

1 - 20 / 43

無線機

【課題】煩雑なメンテナンスを行わなくても周波数精度を高く保つことができ、かつ変調信号による周波数偏移を大きくすることができる無線機を提供する。

【解決手段】基準信号を出力する電圧制御水晶発振器と、高周波信号を出力する電圧制御発振器と、基準信号と高周波信号とが入力され、高周波信号の位相が基準信号と同じになるように位相同期を行う位相同期回路と、参照信号を発生する参照信号発生部と、基準信号の周波数を補正する周波数補正信号を電圧制御水晶発振器に出力するとともに、基準信号と参照信号とに基づき、基準信号の周波数が参照信号の周波数に対して所定の範囲内となるように周波数補正信号の値を変更する制御部と、から無線機を構成する。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

クロック生成装置及びクロック同期方法

【課題】冗長構成を有するとともにクロックの同期が確実に行えるクロック生成装置、及び、クロック同期方法を提供する。

【解決手段】クロック生成装置は、クロックC1、クロックC2をそれぞれ出力するVCXO14、24と、クロックC1又はクロックC2が供給されるとともに主たる機能に使用される主機能部31に設けられ、クロックC1及びクロックC2の位相を比較し、クロックC1及びクロックC2の位相ずれの情報を含む位相差情報を生成する位相比較器33と、この位相差情報に基づいてVCXO24に出力する制御電圧を調整し、クロックC1の位相にクロックC2の位相を同期させる第2制御部22と、を有する。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

クロック信号制御回路及びクロック信号制御方法

【課題】クロック信号の周波数制御をより好適に行うこと。

【解決手段】モニタ回路12のリングオシレータ16によるモニタ結果であるモニタ信号MSの周波数に応じて設定値記憶回路13からテーブル値TVALを出力させる。そして、そのテーブル値TVALに応じてクロック信号生成回路14のPLL回路15a,15bにより生成した発振信号と等しい周波数のクロック信号CLKを対象回路11に供給する。

(もっと読む)

信号受信装置、信号受信装置の制御方法及びコンピュータプログラム

【課題】1つの位相比較器及びループフィルタを複数の同期保持チャネルで共有することで、同期保持チャネルの増加に伴う回路規模の増大を抑えることが可能な信号受信装置を提供すること。

【解決手段】所定の周波数のキャリアを生成する信号生成器を含む位相同期ループ部と、衛星から受信した信号のキャリアと信号生成器が生成したキャリアとの位相差を検出して出力する1以上の位相比較器と、位相比較器が出力する位相差情報からノイズを除去して所望のループの応答を実現する1以上のループフィルタと、を備え、同時に追跡可能な最大衛星数N(Nは2以上)に対して、位相比較器及びループフィルタの数MはN>Mである、信号受信装置が提供される。

(もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

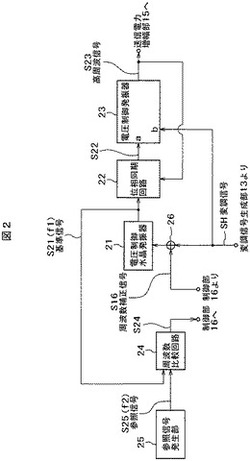

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

冗長構成システムにおける基準信号同期制御方法

【課題】運用系と待機系の位相差を正確に求めることが出来る冗長構成システムにおける基準信号同期制御方法を提供することである。

【解決手段】装置の基準信号を生成し、運用系と待機系の冗長構成を成すユニットにおいて、運用系のハードウェアと、待機系のハードウェアで、同じタイミングの基準信号を用いて装置を動作させるために、運用系から出力する基準信号は、各機能部の他、待機系にも送り、待機系は、運用系から入力される基準信号と自ら生成する基準信号との位相差を、運用系から待機系までの遅延を擬似的に実現させ、そこから求められた遅延量に従い、待機系が生成する基準信号に遅延分のオフセットをかけることで、運用系の基準信号と同期させる。

(もっと読む)

クロック信号発生回路

【課題】簡単な回路構成により、低速の基準クロックから高速のクロック信号を生成することができ、高速クロック信号の周波数選択の制限を緩和することができるクロック信号発生回路を提供すること。

【解決手段】クロック信号発生回路100は、低速の基準クロック信号S1を発生する基準クロック信号発生回路110と、基本クロック信号発生回路110からの低速の基準クロック信号S1をN1逓倍し、逓倍出力S2を出力するPLL回路130と、PLL回路130の逓倍出力S2を1/N分周し、低速の基準クロック信号S1よりも高速の第2の基準クロック信号S3を出力する分周回路140と、分周回路140の第2の基準クロック信号S3をN2逓倍し、高速のクロック信号である逓倍出力S4を出力するPLL回路150とをこの順序で備える。

(もっと読む)

シンセサイザ

【課題】本発明は、周波数可変間隔(チャネルステップ)を細かく設定できると同時に位相比較周波数を高く設定し信号近傍の位相雑音を抑制することを目的とする。

【解決手段】本発明に係るシンセサイザは、高周波信号を発生させる第1のループ84に、第1のループ84の基準周波数を調整するための第2のループ85を設けたことを特徴とする。第2のループ85が第1のループ84の基準周波数を目的の周波数に調整する。第1のループ84は、第2のループ85の調整した基準周波数を用いて高周波信号を発生させる。第2のループ85が第1のループ84の基準周波数を微調整するので、第1のループ84の分周回路の分母を小さくしても周波数設定の分解能は粗くならない。第1のループ84の分周回路の分母を小さくしても、分解能を落とすことなく所望の周波数を発振する。

(もっと読む)

シンセサイザ装置及びこれを備える携帯通信端末

【課題】デュアルシンセサイザ装置において、基板の定在波比が劣化しても、簡単な構成でアイソレーションの低下を防止する。

【解決手段】プリント基板13上には第1及び第のPLLシンセサイザ部11及び12が配置され、第1及び第2のPLLシンセサイザ部には基板に形成された配線パターン13aを介して基準発振器14から基準信号が与えられ、選択スイッチ(SW)45によって第1及び第2のPLLシンセサイザ部からの出力信号のうちいずれか一方が選択される。配線パターンのインダクタンスとこのインダクタンスと対向するアースパターンからなる第1及び第2のコンデンサとによってローパスフィルタが構成される。

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

位相同期回路、同期検波回路および放送受信装置

【課題】簡易な構成で入力信号と同一周波数、同一位相の再生信号を出力すること。

【解決手段】位相同期回路1は、VCO13、混合器11、LPF12からなる第1のフィードバックループで周波数を合わせ、第1のフィードバックループで得られた制御信号をVCO23、混合器21、LPF22、加算器24からなる第2のフィードバックループに供給することで、第2フィードバックループから周波数と位相がともに入力信号と同一な再生信号を出力する。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

1 - 20 / 43

[ Back to top ]