Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

261 - 271 / 271

PLL回路

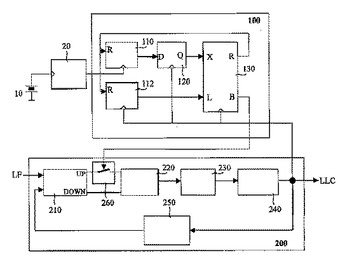

本発明は、位相又は周波数検出回路(210)の出力信号に応じて制御される発振回路(240)を有する位相同期ループ装置に関し、切替制御手段(130)は、所定の閾値周波数が供給される第1のタイマ手段(110)及び発振回路(240)の出力周波数が供給される第2のタイマ手段(112)の出力に応答して遮断信号を発生するように設けられる。遮断信号に基づいて、遮断手段(260)は、発振回路(240)への出力信号の供給を抑制する。これにより、PLL装置の出力周波数は、周波数閾値を超えて変化することが回避可能となるとともに、唯1つのPLL回路だけで済むことになる。

(もっと読む)

(もっと読む)

電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザ

本発明は、発振器および周波数シンセサイザに関する。特に、電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザに関する。

本発明は、アナログ入力端に入力される電圧およびデジタル入力端に入力されるデジタル値によって出力信号の周波数が決定される発振器と、間欠的に前記アナログ入力端に入力される電圧を第1の閾値電圧および第2の閾値電圧と大小を比較し、その結果に応じて前記デジタル入力端に入力されるデジタル値を変化させるデジタル同調器と、を備える電圧制御デジタルアナログ発振器を提供する。また、これを用いた周波数シンセサイザを提供する。本発明に係る発振器および周波数シンセサイザは、雑音が少ないながらも、広帯域の周波数出力を得ることができる長所がある。

(もっと読む)

(もっと読む)

PLL回路のΣΔ変調器

PLL回路の比較分周器の分周比を変調する変調信号を生成するΣΔ変調器。複数の直列接続された積分器(9a〜9c)は、入力信号Fを積算するとともに、積算値が所定値を超えたときオーバーフロー信号OF1〜OF3を出力する。微分器(10a〜10e)は各積分器(9a〜9c)のオーバーフロー信号OF1〜OF3を転送する。加算器(11)は微分器から出力される出力信号(a〜f)に所定の係数を乗算し、その乗算値を加算する。終段の積分器(9c)と、その前段の積分器(9b)との間には、各積分器のクロック信号(fp)の分周信号に同期して積算値を転送する制御回路(12)が接続されている。制御回路(12)を設けることにより、次数を減少させることなく、変調信号の変調幅が減少される。 (もっと読む)

可変遅延回路

本発明に係る可変遅延回路は、直列に接続され、基準クロック信号又はデータ信号を順次遅延させる複数段の第1可変遅延素子と、複数段の第1可変遅延素子に並列に接続され、基準クロック信号を遅延させる第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の位相とを比較する位相比較器と、位相比較器の比較結果に基づいて、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の所定のサイクル後の位相と略等しくすべく、複数段の第1可変遅延素子のそれぞれの遅延量を制御する遅延量制御部とを備える。 (もっと読む)

可調周波数変換器

回路基板にマウントされた電気回路を有する可調周波数変換器が開示される。上記回路は、共振器を備える位相同期ループ(PLL)を提供するにように設計されている。柔軟な材料が回路基板と共振器の間に配置される。電導性リードにより短絡させられる少なくとも1つの受動素子が共振器に作動的に接続される。周波数変換器の共振周波数は、電導性リードを切断し、関連付けられた受動素子を活性化させることにより変更することができる。 (もっと読む)

半導体装置及び電圧制御発振回路

電圧制御発振回路(15)内に互いに異なる段数の独立した複数のリング発振回路を設け、セレクタ(22)により何れか1つのリング発振回路の出力を帰還クロック信号(FB)として選択的に出力することで、独立しているリング発振回路の出力が常に帰還クロック信号として出力されるようにして、動作速度が高速であってもデューティ比が崩れていない帰還クロック信号を出力でき、入力信号(DLLI)が出力されるまでの遅延時間を任意に調整できるようにする。  (もっと読む)

(もっと読む)

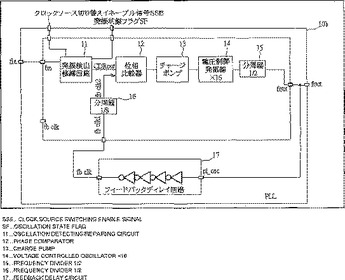

半導体集積回路装置

半導体集積回路装置におけるクロック発生器には、発振検出修繕回路11が設けられている。この発振検出修繕回路11は、外部接続されたクロック発振器が生成したクロック信号finの正常/異常を検出する。クロック信号finが正常の際には、該クロック信号finを選択して出力する。また、クロック信号finが異常の場合には、発振検出修繕回路11が生成したクロック信号を選択して出力する。クロック発生器は、発振検出修繕回路11が選択して出力するクロック信号に基づいてシステムクロックを生成する。また、クロック信号finが異常の場合、CPUは、各モジュールを停止させた後、該CPUを停止させる異常終了処理を実行する。  (もっと読む)

(もっと読む)

セル配列を用いた可変インピーダンス回路

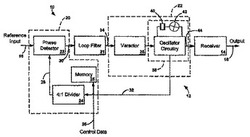

電圧制御回路(100)において、電圧制御発振器(110)(VCO)の周波数を制御する可変コンデンサを駆動するために、回路要素の配列(500)が用いられる。配列(500)は、複数のセル(600)、少なくとも1つの出力、複数の粗設定入力(383-388)及び複数の精細設定入力(380-382)を有する。両方の種類の入力は、前記セルの選択可能な組合せを有効にするようにされる。VCO(110)は、複数の周波数帯域にわたる範囲の複数のビットアドレス処理可能な参照周波数で動作する。アドレス制御回路(130)は、前記粗設定入力(383-388)を制御することによって、前記複数の周波数帯域のうちの1つを確定するとともに、また前記精細設定入力を制御することによって、前記周波数帯域のうちの1つを確定する。1つの実施例において、前記アドレス制御回路は、VCO回路(100)のための周波数帯域を設定するのに用いられ、アナログ信号は、前記帯域内の所望な周波数に同調するのに用いられる。  (もっと読む)

(もっと読む)

遅延ロックループのための起動回路

遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】制御電圧対発振周波数特性が調整可能なVCOを含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、リング状に直列に接続された複数のインバータと、バイアス電圧VBP1に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第1群のPチャネルトランジスタQP11等と、バイアス電圧VBN1に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第1群のNチャネルトランジスタQN11等と、バイアス電圧VBP2に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第2群のPチャネルトランジスタQP21等と、バイアス電圧VBN2に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第2群のNチャネルトランジスタQN21等とを具備する。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

261 - 271 / 271

[ Back to top ]