Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

101 - 120 / 271

VCO回路及びそれを用いたPLL回路

【課題】VCO回路の最適な発振状態を設定するために、製造されたIC毎にバラツキを評価し且つそのバラツキに応じた設定値を指示しなければならないという問題がある。

【解決手段】VCO回路は、制御電圧に応じ制御電流を流す電圧電流変換器と、その制御電流に応じ所定の周波数で発振する電流制御発振器からなる構成において、制御電圧に応じ電圧電流変換器の変換利得を調節する調節回路を更に備えたことを特徴とし、外部からの制御に依存せずに、製造されたIC毎のバラツキに応じ、VCOをロックアップさせる、いわゆる自己制御性(Self Regulating Characteristics)を有する電圧制御発振器を提供することができる。

(もっと読む)

シンセサイザ

【課題】本発明は、周波数可変間隔(チャネルステップ)を細かく設定できると同時に位相比較周波数を高く設定し信号近傍の位相雑音を抑制することを目的とする。

【解決手段】本発明に係るシンセサイザは、高周波信号を発生させる第1のループ84に、第1のループ84の基準周波数を調整するための第2のループ85を設けたことを特徴とする。第2のループ85が第1のループ84の基準周波数を目的の周波数に調整する。第1のループ84は、第2のループ85の調整した基準周波数を用いて高周波信号を発生させる。第2のループ85が第1のループ84の基準周波数を微調整するので、第1のループ84の分周回路の分母を小さくしても周波数設定の分解能は粗くならない。第1のループ84の分周回路の分母を小さくしても、分解能を落とすことなく所望の周波数を発振する。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

半導体装置

【課題】高速応答性と動作の安定化を実現したPLL回路を備えた半導体装置を提供する。

【解決手段】低電源電圧VddLで動作する位相比較回路の低振幅信号を夫々高電源電圧で動作するNチャネルMOSFET入力構成の第1差動回路とPチャネルMOSFET入力構成の第2差動回路に入力する。上記第1及び第2差動回路の負荷としてダイオード接続MOSFETとクロスカップル接続のMOSFETを並列構成にして用いる。ゲートに所定のバイアス電圧が供給されたPチャネルMOSFET,NチャネルMOSFETを直列接続する。上記PチャネルMOSFETのソースは、上記第1差動回路の出力信号で制御し、NチャネルMOSFETのソースは、上記第2差動回路の出力信号で制御し、PチャネルMOSFET及びNチャネルMOSFETのドレインからアップ電流又はダウン電流を形成する。

(もっと読む)

CP出力型位相比較器の制御方法及びCP出力型位相比較器

【課題】CP出力型位相比較器に関し、REFクロック歯抜け後の位相スリップを防止することができる定電流CP出力型位相比較器を提供。

【解決手段】PLL回路に用いる位相比較器において、位相比較器の状態遷移モードをハイインピーダンス状態と、電流吐き出し状態と、電流吸い込み状態の3つの状態を設け、電流吸い込み状態からハイインピーダンスに移行する条件として、REFクロックの立ち上がりに加え、フィードバッククロックの立下がりにおいてもハイインピーダンス状態に遷移するようにして、クロック歯抜け後の出力位相スリップを防止するように構成する。

(もっと読む)

半導体集積回路装置

【課題】本発明は、複数の回路モジュールにクロック信号を供給する際に、クロック信号配線における信号がトグルすることによる消費電力を削減することを特徴とする。

【解決手段】クロックジェネレータ20と、複数の回路モジュール111〜11nと、1つの回路モジュール11nにクロックジェネレータ20で発生されたクロック信号CLKnを供給するクロック信号配線41と、回路モジュール11n以外の回路モジュールに接続された電圧制御発振器311、312、313、…と、クロックジェネレータ20で発生された直流電圧を任意に分圧して、もしくは分圧せずに電圧制御発振器311、312、313、…に供給する複数の配線42を具備し、回路モジュール11nに供給されたクロック信号CLKnがクロックジェネレータ20に帰還クロック信号RetCLKとして帰還される。

(もっと読む)

シンセサイザ装置及びこれを備える携帯通信端末

【課題】デュアルシンセサイザ装置において、基板の定在波比が劣化しても、簡単な構成でアイソレーションの低下を防止する。

【解決手段】プリント基板13上には第1及び第のPLLシンセサイザ部11及び12が配置され、第1及び第2のPLLシンセサイザ部には基板に形成された配線パターン13aを介して基準発振器14から基準信号が与えられ、選択スイッチ(SW)45によって第1及び第2のPLLシンセサイザ部からの出力信号のうちいずれか一方が選択される。配線パターンのインダクタンスとこのインダクタンスと対向するアースパターンからなる第1及び第2のコンデンサとによってローパスフィルタが構成される。

(もっと読む)

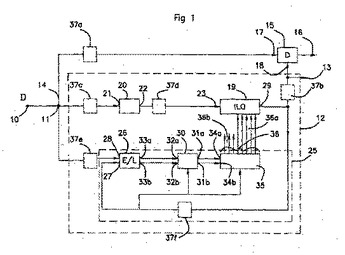

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

PLL回路及びそれを用いた周波数設定回路

【課題】ループフィルタ出力での基準周波数成分を十分に落とせ、かつ、PLLループ内の位相余裕を確保できるPLL回路の提供。

【解決手段】本発明のPLL回路は、電気信号により発振周波数が制御される周波数発振器(VCOまたはICO)13からの出力信号が高域通過フィルタ(HPF)14を介して位相検波器11の一方の入力端子に入力され、位相比較器11の他方の入力端子には基準周波数が入力され、前記位相比較器11の出力信号はループフィルタ12を介して、その直流成分を前記電気信号として周波数発振器13を制御する。

(もっと読む)

DLL回路

【課題】DLL回路を備えたLSIの電磁放射強度を低減し、電磁放射ノイズの電子機器への影響を低減する。

【解決手段】DLL回路は、入力信号に基づいて同期基準信号を生成する入力回路101と、同期基準信号を遅延する第1遅延部102と、前記第1遅延部102によって遅延された同期基準信号の同期位置を調整し、同期対象信号を生成するタイミングオフセット回路103と、 前記同期基準信号と前記同期対象信号との位相差を比較する位相比較回路105と、前記位相比較回路105の比較結果に基づいて前記第1遅延部102の出力信号を選択する第1制御回路106と、前記同期基準信号又は前記同期対象信号を遅延する第2遅延部104と、前記位相比較回路105の比較結果が所定の範囲内である場合に、前記第2遅延部104の出力信号を選択する第2制御回路107と、を備え、前記位相比較回路105は、前記同期基準信号と前記同期対象信号のうち前記第2遅延部104によって遅延された信号と他方の信号との位相差を比較する。

(もっと読む)

PLL回路および再生装置

【課題】データ信号からクロックを復調する際に、周波数ロックがはずれることを防ぎ、再生装置の再生品質を高める。

【解決手段】PLL回路200は位相追従ループと周波数追従ループを備える。周波数追従ループは、周波数比較器202とローパスフィルタLPF225とを備える。周波数比較器202は、復調クロックCLKとデータ信号S1との周波数差を検出し、検出結果に応じた周波数誤差信号を出力する。LPF225は、周波数誤差信号に応じて充放電するコンデンサ226の充放電により周波数誤差信号を平滑して周波数制御電圧信号FVCを得る。第1の制御部240と第2の制御部250は、周波数ロック状態において、周波数比較器202からLPF225への出力が遮断されるオフ期間と遮断されないオン期間が交互に繰り返されるように制御し、オフ期間においてリーク電流に起因するFVCの変動を補正する。

(もっと読む)

シンボル同期回路

【課題】同期回路が1系統で、温度変化等によるクロック位相ずれの増大を防止できるシンボル同期回路を提供すること。

【解決手段】シンボル同期回路は、戻し段数決定部104を有し、可変遅延器101から左端信号109及び右端信号110を取り出す。左端信号109と右端信号110は、クロック信号107をそれぞれ異なる遅延段数により遅延させた信号である。遅延段数とは、クロック信号107を遅らせるために通過させた遅延素子の個数を意味する。戻し段数決定部104は、左端信号109と右端信号110の位相差がクロック周期の自然数倍の時間に最も近くなるときの、左端信号109と右端信号110のそれぞれの遅延段数の差を、戻し段数として算出する。巡回制御部103は、戻し段数決定部104から指示される段数に基づいて戻し処理を行なう。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】より容易に広い制御電位の範囲にわたって発振周波数の線形性が高い電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路、n個の可変容量回路、及び負性抵抗回路と、電源電位からn個の基準電位を生成する基準電位発生部114とを備える。n個の可変容量回路の可変容量素子の一方端子には、n個の基準電位のいずれかがそれぞれ入力される。n個の可変容量回路の可変容量素子の他方端子には、発振周波数をフィードバック制御するための制御電位Vtが共通入力される。そして、第1〜第3の可変容量回路A〜Cの一方端子には、第1〜第3の基準電位Vref1〜3がそれぞれ入力される。この第1〜第3の基準電位Vref1〜3はそれぞれ固定で、かつ、第1の基準電位Vref1と第2の基準電位Vref2の電位差と、第2の基準電位Vref2と第3の基準電位Vref3との電位差が異なっている。

(もっと読む)

多相クロック生成回路およびシリアルデータ受信回路

【課題】位相比較時のオフセットを少なくして高精度で高分解能の等位相多相クロックが生成されるとともに、小回路規模化および低消費電力化が図れる多相クロック生成回路およびシリアルデータ受信回路を提供する。

【解決手段】複数の電圧制御遅延回路2a〜2jを直列接続し、初段の電圧制御遅延回路2aの差動出力から生成される信号F00と、最終段の前段の電圧制御遅延回路2iの差動出力から生成される信号F88Aの逆相の信号であるF00Aとを、位相比較器3で比較し、比較結果をチャージポンプ4、ローパスフィルタ5を経由してバイアス回路から出力する制御電圧信号Pnct,Ncntで信号F00とF00Aとの位相差が無くなるように電圧制御遅延回路2a〜2jの遅延を調整し、電圧制御遅延回路2a〜2jの各差動出力信号からクロック生成部7でシングル信号に変換して等位相の多相クロックを生成する。

(もっと読む)

アナログDLL回路

【課題】遅延の可変量を所望の遅延範囲に設定でき、素子バラツキによる電流変化の影響を低減でき、ジッタ精度の良いクロックを生成できるアナログDLL回路を提供する。

【解決手段】DLL回路を構成するバイアス回路は、第1乃至第3のPMOSトランジスタQ1、Q3、Q5と、第1乃至第3のNMOSトランジスタQ2、Q4、Q6と、定電流源Iと、抵抗Rとから構成されている。定電流源Iは、電源と第2のPMOSトランジスタQ3のドレインとの間に接続されている。この定電流源Iによる定電流を加えてオフセットを持たせることにより、遅延の可変量を所望の遅延範囲に設定でき、ローパスフィルタ出力(Vi)の変化による遅延の変化を小さくすることにより、ジッタ精度の良いクロックを生成できる。

(もっと読む)

半導体装置

【課題】半導体制御装置において、供給先別にクロックの位相を制御し、且つクロック供給の供給先別優先順位を制御することによって、動作時の電源電圧変動を抑えこれにより動作時の消費電力を抑える。

【解決手段】機能により複数に分割された機能モジュールと、上記機能モジュールの夫々に供給されるクロック信号を生成するクロック発振回路と、外部から入力される上記機能モジュールの夫々に対するクロック供給イネーブル信号に従って、上記クロック発振回路の生成するクロック信号を上記機能モジュールの夫々に供給するクロック制御回路を含む半導体装置を提供する。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

位相同期回路

【課題】PLL回路のフィルタを構成する素子の定数を容易に設計する。

【解決手段】位相比較器10で入力信号INと参照信号REFの位相が比較され、位相差に応じたパルス状の電流IDが出力される。電流IDは電圧電流変換器20のキャパシタ21で平滑され、制御電圧VCとして演算増幅器22に与えられる。演算増幅器22で、制御電流ICによって回路網24〜26で生ずるノードN2の電圧と制御電圧VCとが比較され、この制御電圧VCに応じた電流が流れるようにNMOS23が制御される。PMOS23に流れる電流は直列接続されたPMOS27に流れ、このPMOS27に対して電流ミラーを構成するPMOS28から、同じ大きさの制御電流ICが電流制御発振器30に供給される。平滑用のキャパシタ21と回路網24〜26は独立しているので、回路網24〜26を構成する素子の定数を容易に設計することができる。

(もっと読む)

周波数シンセサイザ及びフェーズロックループ、並びにクロック生成方法

【課題】従来構成のPLLを用いることなく、高精度の分周を回路増加を抑えつつ実現可能な周波数シンセサイザ及びクロック生成方法を提供する。

【解決手段】周波数シンセサイザは、リファレンスクロック発生器501からのN相のクロックを基に複数の周波数のクロックを生成する位相選択合成器502、503を備える。位相選択合成器502、503において、クロック選択手段504は、N相クロックと位相番号(j:0から(N−1)までの整数)を入力し、位相番号に対応したクロックを選択することで(N/M)fのクロックを生成する。位相番号生成手段505は、(N/M)fのクロックと分周分母M及び分周分子Nを入力し、(N/M)fのクロックに同期して、分周分母M及び分周分子Nから算出される値(M−N)を累算し、累算値ACCをNで割った剰余を位相番号(j)とする。

(もっと読む)

周波数切替え装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときにシステム誤動作が起きるのを防ぐことのできる周波数切替え装置を提供する。

【解決手段】 周波数切替え器5は、位相周波数比較器10と、チャージポンプ回路11と、LPF回路12と、VCO回路13と、カウンタ回路14と、カウンタ回路14の動作を制御する制御部8を備える。制御部8は、逓倍数変更部16と、変更許可判定部15を備える。変更許可判定部15は、カウンタ回路14のカウンタ値に基づいて、逓倍数を目標逓倍数に変更するのを許可するか否かを判定する。例えば、カウンタ値が目標逓倍数以下の基準値(例えば、カウンタ値0)になったときに、逓倍数の変更を許可する。

(もっと読む)

101 - 120 / 271

[ Back to top ]