Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

121 - 140 / 271

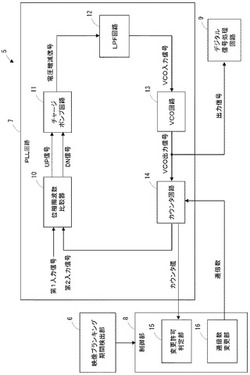

周波数切替え装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときにシステム誤動作が起きるのを防ぐことのできる周波数切替え装置を提供する。

【解決手段】 周波数切替え器5は、位相周波数比較器10と、チャージポンプ回路11と、LPF回路12と、VCO回路13と、カウンタ回路14と、カウンタ回路14の動作を制御する制御部8を備える。制御部8は、逓倍数変更部16と、変更許可判定部15を備える。変更許可判定部15は、カウンタ回路14のカウンタ値に基づいて、逓倍数を目標逓倍数に変更するのを許可するか否かを判定する。例えば、カウンタ値が目標逓倍数以下の基準値(例えば、カウンタ値0)になったときに、逓倍数の変更を許可する。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、高安定な基準信号の入力がなく、自走したときでも発振周波数を安定に保つことができる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、外部基準信号を検波する検波回路17と、パルス生成の情報が入力されるとパルスを生成してループフィルタ14に出力するPWM回路22と、電圧情報と対応するパルス生成の情報を記憶するメモリ21と、位相比較器12とループフィルタ14との接続をオン/オフするスイッチ13と、検波回路17で検出された外部基準信号のレベルが適正範囲内であればスイッチ13をオンとし、レベルが適正範囲外であればスイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する発振周波数制御回路である。

(もっと読む)

撮像装置

【課題】サンプルホールドタイミングを高精度に決定しながらも消費電力を抑えることが可能な撮像装置を提供する。

【解決手段】撮像素子と、撮像素子から出力される撮像信号OSに相関二重サンプリング処理等を行うAFEとを有するデジタルカメラであって、DLL回路40と、AFEを制御するための制御信号(サンプルホールドタイミングパルスshp)をDLL回路40から出力されるクロックpulseに基づいて生成するパルス発生回路と、ブランキング期間中、DLL回路40を、そのロック状態を維持させたまま停止させる制御を行うDLL制御部51とを備える。

(もっと読む)

ヘテロダイン受信機、PLL発振回路及び間欠受信制御方法

【課題】PLL発振回路を使用して間欠受信動作を行う受信機のオン・オフ時間の比率を大きくして、省電力効果の向上を図ったPLL発振回路、ヘテロダイン受信機及びその間欠受信制御方法を提供する。

【解決手段】PLL発振回路の要部への電源制御用第一のスイッチと、位相比較器と低域フィルタとの間に挿入した第二のスイッチ回路とを備え、これらを間欠的に制御することにより、PLLの同期を促進する。

(もっと読む)

発振回路、PLL回路、半導体チップ、および、試験装置

【課題】発振回路における位相雑音成分を低減する。

【解決手段】発振信号を生成する発振回路であって、与えられる制御電圧に応じた周波数の発振信号を出力する電圧制御発振器と、電圧制御発振器が出力する発振信号の位相の変動成分を抽出し、位相の変動成分に応じて制御電圧を調整するジッタ復調器とを備える発振回路を提供する。発振回路は、電圧制御発振器に入力される制御電圧の、予め定められたカットオフ周波数より大きい周波数成分を除去して、電圧制御発振器に供給するローパスフィルタを更に備えてよい。

(もっと読む)

電圧制御発振器、PLL回路

【課題】 低周波の発振信号であっても安定して出力することが可能な電圧制御発振器及びPLL回路を提供する。

【解決手段】 本発明に係る電圧制御発振器1は、インダクタ4及び可変キャパシタ5を有するLC共振回路2と、複数の負性抵抗回路NR1、NR2、…、NRnを備える。各負性抵抗回路NR1、NR2、…、NRnは、定電流源CG1、CG2、…、CGnを介して夫々接地線と接続される構成であり、各定電流源は、夫々個別に導通状態(一定電流を流す状態)と非導通状態(開放された状態)との間で切換制御が可能に構成されており、本発明に係る電圧制御発振器1は、これらの各定電流源の導通制御を行うための制御手段7を備える構成である。

(もっと読む)

フィードフォワード分割器を有する適応帯域幅位相ロックループ

【課題】位相ロックループを提供する。

【解決手段】一部の実施形態では、チップは、第1及び第2の電圧制御式発振器(VCO)出力信号を供給するための第1及び第2のVCOと、第1及び第2VCO出力信号の第1及び第2の周波数を第1及び第2の分周率によって分割するための第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)を含む。チップはまた、第1及び第2分周率を選択するための位相ロックループ制御回路を含む。他の実施形態も説明して特許請求する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成するための技術が説明される。位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。  (もっと読む)

(もっと読む)

位相ロック・ループを制御する方法、利得制御装置及び位相ロック・ループ・システム

【課題】マルチ・ギガヘルツ範囲で動作し且つ低ジッタの、調整可能な利得を有する位相ロック・ループ(PLL)を提供する。

【解決手段】

1つの実施形態では、PLLのfVCO 信号の諸特性を取得する。これらの特性は、fVCO 信号及びPLLの位相ロック状態に関する異なるタイプのジッタの出現回数を含む。利得制御モジュールは、前記取得した諸特性の分析に基づき、少なくともPLLの一部を制御する。例えば、PLLが位相ロックされているか、又はループ・フィルタの漏洩がある場合、PLL内にあるチャージ・ポンプの利得が減少される。前記取得した特性に基づいて、チャージ・ポンプのミスマッチが検出される場合、当該ミスマッチを修正するために、追加の制御信号がチャージ・ポンプに供給される。

(もっと読む)

クロックデータ復元装置

【課題】トランスミッタ・クロック・ジッタや符号間干渉が大きい場合であっても安定してクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、サンプラ部10、検出部20、オフセット決定部30、クロック出力部40およびDA変換部50を備える。クロック信号CK,CKXの位相は、入力デジタル信号の位相と一致するよう調整される。サンプラ部10におけるオフセット付与量(±Voff)は、値D(n-1)がハイレベルである場合の第1信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整され、値D(n-1)がローレベルである場合の第2信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整される。復元されたクロック信号として、クロック信号CK,CKXの何れかが出力される。復元されたデータとして、デジタル値D(n)の時系列データが出力される。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

電圧生成回路及び発振装置

【課題】位相雑音特性が良好で、かつ低消費電力、小型化に適した発振装置を提供すること。

【解決手段】固定電圧Vrefが印加される第1の端子と、可変電圧Vcが印加される第2の端子と、前記第1の端子と前記第2の端子との間に直列接続された、抵抗値rのm個の抵抗器及び抵抗値RINの入力抵抗器と、前記m個の抵抗器のうちn個の抵抗器を選択するための複数のスイッチと、制御電圧を出力する第3の端子と、を有する抵抗切替部と、前記複数の抵抗器に流す定電流の電流値Ioffを設定し当該定電流を供給する電流供給部とから構成され、{Vref+n×r×[(VC−Vref)/(m×r+RIN)]}で与えられる第1の電圧と、{−(n×r×Ioff)}で与えられる第2の電圧との重ね合わせにより規定される第3の電圧を、前記第3の端子から制御電圧として出力する。

(もっと読む)

スペクトラム拡散クロック発生装置

【課題】スペクトラム拡散されたクロックにて動作するデバイスとスペクトラム拡散されていないクロックで動作するデバイスとの間において、同期扱いのまま信号のやり取りを行うことを可能とする。

【解決手段】基準クロックRCLKと出力クロックCLKOの位相差を検出する周波数位相比較器104と、この位相差に応じて充放電信号を発生するチャージポンプ103と、充放電信号に応じた差信号を発生するループフィルタ104と、前記差信号を変調してスペクトラム拡散変調信号を生成するスペクトラム拡散変調器106と、このループフィルタの出力とスペクトラム拡散変調信号の合成信号に応じて出力クロックを発生するクロック発生器107とを備える。スペクトラム拡散変調器106は、出力クロックの周期と基準クロックの周期との差分の符号を反転させるとともに前記差分の絶対値を順次変化させるスペクトラム拡散変調信号を生成する。

(もっと読む)

遅延ロックループ回路

【課題】安定なクロック信号を供給できる遅延クロックループ回路を提供する。

【解決手段】遅延ロックループ回路において、電圧制御遅延線回路は、複数段の遅延素子を備え、基準となるクロックから多相クロックを生成する。位相比較回路は、初段と最終段の遅延素子からの出力をそれぞれシングル波形に変換した第1と第2のクロックの位相差を求める。充電回路と放電回路は、前記位相差に対応する時間だけ充電電流および放電電流をそれぞれ生成し、補正回路は、この充電電流と放電電流の差を所定値に保つ。ローパスフィルタは、充電電流または放電電流により充放電され第1の制御電圧を生成する容量を備える。第2制御電圧生成回路は、第1制御電圧が所定の一定電圧になるように生成した第2の制御電圧を出力する。電圧制御遅延線回路は、多相クロック生成手段を制御する第1と第2の制御電圧を入力して、第1と第2のクロックの間の位相差を一定にする。

(もっと読む)

位相同期回路および電子機器

【課題】位相同期回路において、発振回路の周波数変換ゲインのばらつきに起因する帯域やダンピングファクタのばらつきの発生を防止する。

【解決手段】ゲイン特性情報取得部107Aは、判定基準周波数f1,f2を使って、初期電流Iini と各周波数で発振させるための周波数制御電流Iosciとを合成して電流制御発振部101Aに供給しながら、実動時の電流制御発振部101Aの周波数変換ゲインKcco を規定する判定基準周波数f1,f2の各発振制御信号Iosci_1,Iosci_2の差の情報(Iout_2 )を測定し、そのデータを周波数比較結果保持部172_2に記憶しておく。位相同期動作時には、周波数比較結果保持部172_2に記憶しておいた周波数比較結果fcompのデータD(f2)に基づく制御電流Icpcnt を補正信号として使って、周波数変換ゲインKcco のばらつきが相殺されるように駆動部104Zを制御する。

(もっと読む)

ディレイ調整回路およびその制御方法

【課題】同一チップ上の半導体素子のばらつきによる遅延特性のばらつきを補正するディレイ調整回路を提供すること。

【解決手段】ディレイ調整回路は、9段のディレイ素子が直列接続されるディレイ部と、ディレイ部の7段目の信号の立ち上がりエッジである第1エッジが第1基準信号の立ち上がりエッジである第1基準信号エッジよりも進んでいるか否かを検知する第1カウンタ10と、ディレイ部の9段目の信号の立ち上がりエッジである第2エッジが第1基準信号エッジよりも遅れているか否かを検知する第2カウンタ11と、第1カウンタ10において第1エッジが第1基準信号エッジよりも進んでおり、かつ、第2カウンタ11において第2エッジが第1基準信号エッジよりも遅れるように、基準信号Vbを補正して、ディレイ部のディレイ素子の遅延時間を調整する出力電流Ib1を出力するディレイ素子調整部と、を備えている。

(もっと読む)

無線LAN集積回路装置と無線LANシステム

【課題】簡単な構成で使用環境に対応した広範囲の温度抑制機能を持ち、安定した送受信動作を実現した無線LAN用集積回路装置及びそれを用いた無線LANシステムを提供する。

【解決手段】アンテナにて受信された高周波信号を高周波増幅回路で増幅する。復調用ミキサーにより上記増幅された上記高周波信号をPLL回路で形成された周波数信号を用いてダウンコンバートする。上記復調用ミキサーの出力信号を可変利得増幅回路で増幅する。上記復調用ミキサーの出力信号の強度を測定回路で検出し、上記可変利得増幅回路の利得制御信号を形成する。と上記PLL回路として、温度センサーと、上記温度センサーの出力信号をデジタル信号に変換するADCと、上記ADCの出力信号によりPLLループ帯域の温度変動抑制を行う抑制回路を設ける。

(もっと読む)

遅延同期ループ及びこれを備えた半導体メモリ装置

【課題】遅延同期ループ及びこれを備える半導体メモリ装置を公開する。

【解決手段】入力クロック信号と偶数個の遅延クロック信号のうちの1つの遅延クロック信号との位相を比較して第1アップ信号及び第1ダウン信号を発生し、入力クロック信号の上昇エッジと下降エッジのうちの1つのエッジを検出してパルス信号を発生し、第1アップ信号及び第1ダウン信号に応答して第1制御信号を変更する第1制御部、及びリング状に従属連結された偶数個の遅延セルを備え、第1制御信号に応答して偶数個の遅延セルの遅延時間が変更されて入力クロック信号の周期と同一の周期を有する偶数個の遅延クロック信号を発生し、偶数個の第1選択信号のうちの活性化された1つの第1選択信号に応答して偶数個の遅延クロック信号のうちの少なくとも1つの遅延クロック信号の遷移が制御され、残りの遅延クロック信号の遷移が少なくとも1つの遅延クロック信号の遷移に応答して遷移する遅延器を備えた周期同期部で構成されている。

(もっと読む)

半導体集積回路装置およびそのテスト方法

【課題】PLL回路のテスト回路のチップ面積を小さくする。

【解決手段】分周器PSのテスト時に、バランT1を介してテスト制御電圧信号TCおよびRFテスト信号TSが入力端子IN1、IN2に供給される。テスト制御電圧信号TCは、抵抗R1、R2を流れ、NPNトランジスタQ0がオンとなることで、電圧制御発振器V1およびバッファB10は、電流源I1からの電流が供給されず動作を停止し、バッファB10の出力インピーダンスは高くなる。入力端子IN1、IN2の電位は、テスト制御電圧信号TCの電位にあるので、バラクタダイオードVD1、VD2は、順バイアス状態となって、容量値がより大きくなる。RFテスト信号TSは、出力インピーダンスの高いバッファB10の影響を受けることなく、バラクタダイオードVD1、VD2を介して分周器PSに入力される。

(もっと読む)

低電力のモジュラス分周器ステージ

モジュラス分周器ステージ(MDS)は、第1と第2のステージを含んでいる。MDSは、MDSが2分割モードまたは3分割モードのいずれで動作するかを決定するモジュラス除数制御信号Sを受信する。MDSのステージは、他のMDSからフィードバック・モジュラス制御信号も受信する。MDSは、2分割モードの場合、フィードバック・モジュラス制御信号にかかわらず、2で分割(分周)する。電力を節約して使用するため、MDSステージが2分割モードで動作するとき、第1のステージには電力が供給されない。MDSは、3分割モードの場合、フィードバック・モジュラス制御信号に依存して2または3のいずれかで分周する。電力消費をさらに減らすため、MDSステージが3分割モードにあるにもかかわらず2分割動作を行っているとき、第1のステージには電力が供給されない。第1のステージが電力供給されていないとき、電力ダウントランジスタは、第1のステージの出力を適正な論理レベルに維持する。 (もっと読む)

121 - 140 / 271

[ Back to top ]