Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

81 - 100 / 271

周波数および電圧制御回路、電子機器およびネットワーク装置

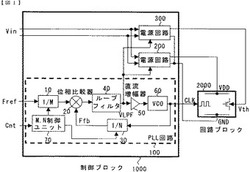

【課題】PLL回路を搭載する電子機器を低消費電力で運用するモードに切替えるとき、または、高速処理可能な運用モードに切替えるとき、一度回路の処理を止めてから、クロック周波数、電源電圧、MOSFETの閾値電圧を切替える必要があった。また切替えにそれぞれ別の制御回路、手法が必要であった。

【解決手段】PLL回路のループフィルタが出力する電圧値に連動させて電源電圧および、MOSFETの閾値電圧を切替えることによって、クロック周波数を変える動作をさせるだけで、被制御回路の電源電圧およびMOSFETの閾値電圧も切替える。また、PLL回路の応答特性を単調増加もしくは単調減少で緩やかな変化にすることで、回路の動作を止めずにモードが切替えを可能とする。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】デジタルオーディオ回路で使用する第1クロック信号CLKAとDC−DCコンバータで使用する第2クロック信号CLKBとの周波数差によって生ずる可聴周波数帯域のノイズ信号を除去することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】発振周波数制御回路23は、第1クロック信号CLKAの第1周波数FAと第2クロック信号CLKBの第2周波数FBとの差が可聴周波数帯域に入ると、第2発振回路21に対して、該帯域に留まらないように第2周波数FBを変化させるようにし、第2周波数FBが可聴周波数帯域に入った場合は、第2発振回路21に対して、第2周波数FBを上昇させて最大可聴周波数以下にならないようにした。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

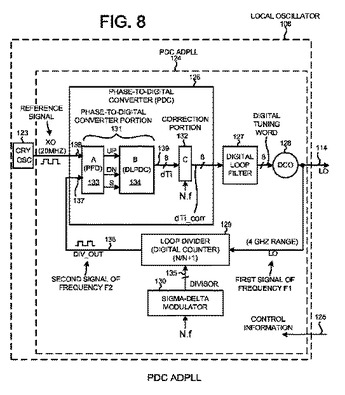

自己訂正する位相デジタル伝達関数を有する位相ロックループ

位相ロックループは、位相デジタル変換器部分、ならびに新規訂正部分を含む。位相デジタル変換器(PDC)部分は、第1の位相誤差ワードのストリームを出力する。新規訂正部分は、第1の位相誤差ワードを受け取り、そしてループフィルタへと供給される第2の位相誤差ワードのストリームを生成する。PDC部分は、ある種の不完全性を示す位相デジタル伝達関数を有する。第1の例においては、訂正部分は、第1の位相誤差ワードの対の間の平均差を決定し、そして遅延要素伝搬遅延の変化に起因したPDC部分の伝達関数の傾斜における変化について訂正するために第1の位相誤差ワードを正規化するためにこの平均差を使用する。第2の例においては、訂正部分は、PDC部分の伝達関数における利得ミスマッチについて訂正する。第3の例においては、訂正部分は、PDC部分の伝達関数におけるオフセットミスマッチについて訂正する。  (もっと読む)

(もっと読む)

PLL回路

【課題】 VCOを構成する電流制御発振回路を制御する電流を生成する電圧−電流変換の動作を高速化して、従来に比較して周波数制御の応答特性を向上させるPLL回路を提供する。

【解決手段】 本発明のPLL回路は、電圧−電流変換回路と電流加算器と電流制御発振回路とから構成され、制御電圧及び制御電流に対応した周波数のパルスを出力する電圧制御発振回路と、パルスと、電圧制御発振回路が生成すべき周波数の基準パルスとの位相差により、第1の制御信号及び第2の制御信号を出力する位相検出器と、第1の制御信号により、第1の充電電流または第1の放電電流を出力する第1のチャージポンプ回路と、第1の充電電流または第1の放電電流により制御電圧を生成し、電圧制御発振回路に出力するループフィルタと、第2の制御信号により、第2の充電電流または第2の放電電流である制御電流を生成し、制御電圧発振回路に出力する第2のチャージポンプ回路とを有する。

(もっと読む)

通信装置、及びそのシステムクロック制御方法

【課題】 受信バッファ量を増減させずに、IP網の揺らぎに対処する。

【解決手段】 通信装置であるIP−PBX100は、IP網5からのパケットを一時的に溜める受信バッファ32と、受信バッファに溜まったパケットをシステムクロック信号に同期して順次処理するパケット処理部33と、受信バッファに溜まっているデータ量を検出するバッファデータ量検出部40と、バッファデータ量検出部で検出されたデータ量に応じた周波数のシステムクロック信号を発振するシステムクロック発振部50と、を備えている。

(もっと読む)

クロックリカバリ回路

【課題】 クロック信号の切り替え時における不要成分の発生を効果的に抑制できるクロックリカバリ回路を提供する。

【解決手段】 異位相の選択クロック信号を複数の選択クロック信号群に分類し、前段選択制御信号により選択クロック信号の1つを前段出力クロック信号として出力する前段選択回路を、選択クロック信号群毎に備える前段選択回路群14と、後段選択制御信号により前段出力クロック信号の1つを再生クロック信号RCLKとして出力する後段選択回路15と、受信データと再生クロック信号RCLKの位相差に基づいて位相制御信号を出力する位相制御回路11と、位相制御信号により特定される選択クロック信号を選択する前段選択制御信号を出力する前段選択制御回路12と、切り替えが必要な場合に、現在の前段出力クロック信号と新たな前段出力クロック信号の論理値が同じになる期間に後段選択制御信号を出力する後段選択制御回路13を備える。

(もっと読む)

FMチューナ

【課題】FMチューナのステレオ復調部における、パイロット信号をキャプチャするPLLを構成するVCOを、CR発振回路を用いて構成すると、温度に応じた発振周波数の変動に対応してキャプチャレンジが大きく設定される。そのため、パイロット信号の近傍周波数のノイズ等にPLLが誤って同期しやすくなる。

【解決手段】ステレオ復調部76を含むチューナ半導体チップ内に温度センサ回路94を設け、VCO部位の温度を検知する。温度センサ回路94の出力信号STPに基づいて、VCOの発振周波数fVCOを調整し、温度によるfVCOの変動を補償する。これによりキャプチャレンジの幅を、セラミックレゾネータ等を用いた場合のように狭く設定できる。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、外部基準信号の検波における温度特性に応じて外部基準信号の入力レベルの適正範囲内を特定し、その適正範囲の内外に対して電圧制御発振器の制御電圧を制御して高安定な発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、温度センサ22と、固定電圧供給回路23と、外部基準同期モードとして位相比較器12とループフィルタ14を接続し、固定電圧モードとして固定電圧供給回路23とループフィルタ14を接続する選択スイッチ13と、検波回路17で検出された外部基準信号レベルの検波電圧が温度センサ22で検出された温度の温度特性に応じた適正範囲内であれば外部基準同期モードとし、適正範囲外であれば固定電圧モードとして選択スイッチ13を切り替えるCPU20とを有する発振周波数制御回路である。

(もっと読む)

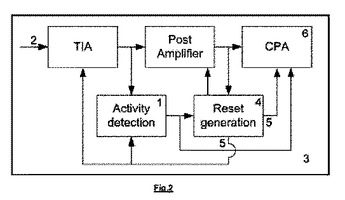

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

遅延ロックループ回路

【課題】クロック信号CKに対し、1周期Tだけ正確に遅れた出力信号OT、及び、可変遅延回路70に用いたn個の各遅延セルにて均等な遅延時間T/nの出力信号を得る。

【解決手段】DLL回路は、制御信号CTLに基づき遅延時間が変わる同一構成の遅延セル50−11,〜,50−3nにより構成される第1、第2の入力ゲート40−1,40−2及び可変遅延セル70と、遅延セル50−11と入力容量が同一の位相比較回路80内の第3、第4の入力ゲート82−1,82−2とを有している。位相比較回路80は、クロック信号CKが入力ゲート40−1を経た出力信号CK−Aと、クロック信号CKが入力ゲート40−2と可変遅延回路70とを経て遅延した出力信号OTとの各信号波形の位相を比較する。その比較結果は、負帰還を掛ける制御信号CTLとして、入力ゲート40−1、40−2及び可変遅延回路70へ与えるようにした。

(もっと読む)

PLLキャリブレーション

変調信号を位相ロックループに加える方法であって、前記変調信号をフィルタリングして低周波数成分と高周波数成分を準備し、位相ロックループのフィードバック経路及びフィードフォワード経路にそれぞれ加えることを含む。前記高周波数成分は、前記フィードフォワード経路に加えられる前に、ゲイン係数によりスケールされる。前記低周波数成分も、ゲイン係数によりスケールされた後、前記フィードフォワード経路に加えられる。前記変調信号とループエラー信号との共通の低周波数範囲におけるエネルギーが見積もられ、その後、前記ゲイン係数は前記測定されたエネルギーに基づいて変更される。  (もっと読む)

(もっと読む)

PLL回路

【課題】DCOの変換利得が常に一定の目標値となるように調整して安定したPLL動作を実現する。

【解決手段】まず、DCOの前段に位置する乗算器に、デジタル値である“1”を入力した状態で一度収束動作を完了させる。続いて、最初の収束状態でのDCOの制御デジタル値を任意の設定値で除したデジタル値をDCOの前段に位置する乗算器に切り替えて入力して、2度目の収束状態でのDCOの制御デジタル値を任意の設定値に収束させる。PLLの系において、DCOを制御するデジタル値の基準値を任意の値に調整して、DCOの変換利得を所望の値に調整できる。

(もっと読む)

高周波モジュール

【課題】入力デジタル信号に対するクロックのより実効性の高い位相補償をより簡単な手法で実現する。

【解決手段】数十Gbps帯の伝送レートを有する入力デジタル信号と数十GHz帯のクロックとを入力信号とし、入力デジタル信号のレベルをクロックを用いて検出することにより入力デジタル信号に所定の処理を施す高速ロジック回路を備えた高周波モジュールであって、クロックに所定の遅延量を付与して高速ロジック回路に出力すると共に、遅延量を操作信号に基づいて可変設定する可変遅延回路と、入力デジタル信号と可変遅延回路から高速ロジック回路に入力されるクロックとの位相差を検出し、該位相差に応じた位相差信号を出力する位相比較器と、上記位相差信号から位相差を示す直流信号を抽出するフィルタと、上記直流信号から可変遅延回路に対応した遅延操作信号を生成する制御器とを具備する。

(もっと読む)

クロックデータリカバリー回路

【課題】周波数オフセットによるジッタ耐性の低下を防止するクロックデータリカバリー回路を提供する。

【解決手段】ディジタル制御発振器107における発振周波数の変化が矩形パルス状になるようにし、その周波数変化パルスの高さと幅を制御パラメータとしてディジタル制御回路104、105、106に与える。

(もっと読む)

チャージポンプ回路、チャージポンプ装置、PLL回路、DLL回路、クロックデータリカバリシステム

【課題】チャージポンプ回路による充放電動作の正確性を向上させる。

【解決手段】充放電回路101では、充電部111は、制御信号UPに応答して充電電流を発生させ、放電部112は、制御信号DNに応答して放電電流を発生させ、これらの合成電流が中間電流Iaとして出力される。レプリカ回路102は、充放電回路101と同一の構成を有し、制御信号SIGに応答して、充電電流と放電電流との電流量の差(誤差成分)に相当する中間電流Ibを出力する。電流調整回路103は、中間電流Ibの極性を反転させ、調整電流Icとして出力する。これにより、中間電流Iaから中間電流Ib(誤差成分)が除去される。

(もっと読む)

位相ロックループ回路

【課題】出力クロック信号の定常位相誤差を防止することを課題とする。

【解決手段】リファレンスクロック信号及びフィードバッククロック信号の位相差を検出する位相差検出器(101)と、前記検出された位相差に応じて、第1のコンデンサを電源電圧又は基準電位に接続する第1のチャージポンプ回路(102)と、前記検出された位相差に応じて、第2のコンデンサを前記電源電圧又は前記基準電位に接続する第2のチャージポンプ回路(122)と、前記第1及び第2のコンデンサの電圧を比較して比較結果信号を出力する比較器(141)と、前記比較結果信号に応じて、前記第1のコンデンサを前記電源電圧又は前記基準電位に接続する第1のスイッチ(142)と、前記第1のコンデンサに接続され、前記第1のコンデンサの電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振器(104)とを有する。

(もっと読む)

高速シリアルインターフェース回路及び電子機器

【課題】トランジスタの経時変化による信頼性の劣化等を防止できる高速シリアルインターフェース回路及びこれを含む電子機器を提供すること。

【解決手段】高速シリアルインターフェース回路は、データレシーバ回路10、クロックレシーバ回路20、シリアル/パラレル変換回路40を少なくとも有するロジック回路ブロック30、自走クロック生成回路70、クロック検出回路80を含む。クロック検出回路80は、差動クロック信号線を介してクロックが転送されているか否かを検出する。クロックレシーバ回路20は、自走クロック生成回路70から自走クロックOSCKを受け、差動クロック信号線を介してクロックが転送されていないことが検出された場合には受信クロックCKINの代わりに自走クロックOSCKをロジック回路ブロック30に出力する。

(もっと読む)

クロック生成回路及び電子機器

【課題】入力クロックから出力クロックまでの遅延時間のロックと出力クロックの精度の良い位相調整とを両立できるクロック生成回路、電子機器の提供。

【解決手段】クロック生成回路は、クロックCK1を受け、クロックCK2を出力するスキュー調整回路10と、クロックCK2を受け、クロック遅延時間がロックされた多相クロックRCK1〜RCKMを生成して出力するDLL回路40と、多相クロックのいずれかに対応するクロックを、出力クロックCKQとして出力するクロック出力回路70を含む。スキュー調整回路10は、クロックCK1を遅延させたクロックをクロックCK2として出力する遅延回路30と、多相クロックのいずれかに対応するクロックCK3を受け、クロックCK1とCK3の位相が一致するように、クロックCK1に対するクロックCK2の遅延時間を調整する遅延調整回路20を含む。

(もっと読む)

位相調整装置

【課題】設計時以降に生じる位相差の変動を内部で自動的に調整することで、予め設定された位相差を有する2つの信号を出力する。

【解決手段】2つのクロック信号の位相差を予め定められた位相差に調整する位相調整装置であって、第1クロック信号に対する第2クロック信号の遅延量を選択的に変更可能な遅延部11と、前記遅延量を制御する制御部12とを備え、前記制御部12は、準備モードにおいて、前記遅延量を第1の時間間隔で段階的に増加又は減少させ、遅れ期間、又は、進み期間を検出し、調整モードにおいて、前記遅れ期間又は前記進み期間と同じ長さの期間において第2の時間間隔で前記遅延量を段階的に変化させることで、前記第2クロック信号の位相差を予め定められた位相差に調整し、前記第2の時間間隔と前記第1の時間間隔との比は、180度と予め定められた位相差との比に等しい。

(もっと読む)

81 - 100 / 271

[ Back to top ]