Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

41 - 60 / 271

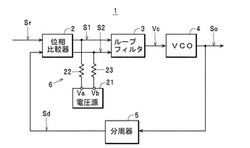

位相同期回路

【課題】デジタル型の位相比較器だけで構成しつつ、不感帯の影響を排除して出力信号の位相雑音を低減する。

【解決手段】制御電圧Vcに応じた周波数の出力信号Soを出力する電圧制御発振器4と、位相比較対象信号Sdおよび基準信号Srを入力して、位相比較対象信号Sdの位相が基準信号Srの位相に対して遅れているときには両信号Sd,Srの位相差に応じたパルス幅の第1パルス信号S1を出力し、位相比較対象信号Sdの位相が基準信号Srの位相に対して進んでいるときには両信号Sd,Srの位相差に応じたパルス幅の第2パルス信号S2を出力する位相比較器2と、両パルス信号S1,S2を入力すると共に両パルス信号S1,S2の差分を積分して制御電圧Vcを出力するループフィルタ3とを備え、両パルス信号S1,S2のうちの一方のパルス信号の信号電圧を他方のパルス信号の信号電圧と異なる電圧に規定する電圧規定部6を備えている。

(もっと読む)

信号レベル変換回路および位相同期回路

【課題】信号レベル変換回路の上限動作周波数を向上させる。

【解決手段】クロック信号をゲート(G)電極に受ける第1MOSトランジスタ(MOS−Tr)と,ドレイン(D)電極を第1MOS−TrのD電極に接続される第2MOS−Trと,逆相のクロック信号をG電極に受ける第3MOS−Trと,G電極およびD電極を第2MOS−TrのG電極と第3MOS−TrのD電極に接続された第4MOS−Trと,第1および第2MOS−TrのD電極から取り出した信号を受けるインバータ回路により構成されたレベル変換回路において,第2MOS−Trのソース電極と電源の間,または,第4MOS−Trのソース電極と電源の間の少なくとも一方に,並列に接続した複数の第5MOS−Trを設け,インバータ回路の出力の平均電圧が低電位側の電源と高電位側の電源の中間の電圧になるように第5MOS−Trの導通及び遮断を制御する制御回路を設ける。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

遅延ロックドループ回路

【課題】原理的に定常ジッタがなく、基準クロック信号のデューティ比にかかわらず高精度な遅延クロック信号を生成可能な遅延ロックドループ回路を実現する。

【解決手段】遅延素子(10)は、基準クロック信号の立ち上がり(又は立ち下がり)から、ループフィルタ(40)の出力に基づいた量だけ遅延して変化する遅延クロック信号を生成する。信号生成回路(20)は、基準クロック信号の立ち上がり及び立ち下がり並びに遅延クロック信号の変化に応じて相補的に変化する二つの信号を生成する。チャージポンプ回路(30)は、ループフィルタ(40)に対して、これら二つの信号に従って、基準クロック信号の立ち上がり(又は立ち下がり)から遅延クロック信号の変化までの間プッシュ動作(又はプル動作)を、遅延クロック信号の変化から基準クロック信号の立ち下がり(又は立ち上がり)までの間プル動作(又はプッシュ動作)を行う。

(もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラを提供する。

【解決手段】PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL300)とを備えている。このPLL300は、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器312と、前記発振器312に結合され、前記基準信号341を受信し、且つ前記基準信号341と、フィードバック信号342との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD302)と、前記PFD302に結合され、周期的にPFD302が誤り訂正信号を生成することができるようにする抑制回路321とを備えている。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にし、同期クロックのずれを小さくしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力し、データ入力信号に特定期間変化がない場合に擬似信号を供給する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号の入力端子とVCXO109の入力端子との接続を、異常信号によりオンにするスイッチ104とを有するタイミングリカバリー回路である。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

デッドロック検出回路およびデッドロック復帰回路

【課題】誤検出することなく、デッドロック状態を正確に検出することができるデッドロック検出回路を提供する。

【解決手段】デッドロック検出回路は、PLL回路のデッドロック状態を検出するものであり、PLL回路の電圧制御発振器の出力信号を分周して、第1の分周クロックを出力するPLL内蔵分周器と、電圧制御発振器の出力信号を分周して、PLL回路の位相比較器へのフィードバッククロックとなる第2の分周クロックを出力するフィードバック分周器と、第1の分周クロックの周期によって決定される所定の期間に含まれる、第2の分周クロックのクロック数に基づいて、デッドロック状態であるか否かを表す判定信号を出力する誤ロック検出回路とを備えている。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

チャージポンプ回路、及びクロック生成器

【課題】チャージポンプ容量の充電電流と放電電流とが等しくなるように補正する。

【解決手段】外部から充電制御信号を受けて制御電圧を増加させ、外部から放電制御信号を受けて制御電圧を減少させる第1のモードと、補正動作を行う第2のモードとを有したチャージポンプ回路であって、第1のモードにおいて、充電制御信号に応じて第1のノードを通して充電電流を流し出す充電部と、放電制御信号に応じて第2のノードを通して放電電流を吸い込む放電部と、第2のモードにおいて、第1のノードと第2のノードとに一端が接続される検出抵抗と、検出抵抗の他端に参照電圧を供給する電圧源と、充電部が検出抵抗の一端へ充電電流を流し出し放電部が検出抵抗の一端から放電電流を吸い込んだ状態における検出抵抗の一端の電圧と参照電圧との差に基づいて、充電部が流し出す充電電流と放電部が吸い込む放電電流とが等しくなるように補正する補正部とを備える。

(もっと読む)

フィルタ回路

【課題】本発明は、フィルタリング特性調整機能を有するアナログフィルタを有するフィルタ回路に関し、アナログフィルタのフィルタリング特性を簡易な補正回路によって補正する機能を備える。

【解決手段】アナログフィルタ50と、レプリカ回路としての発振器61と、周波数比較ロジック62を備え、周波数比較ロジック62で、その発振器61の発振周波数が基準周波数となるように、発振器61とアナログフィルタ50との双方を同時に調整する。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部と、を有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記生成部から出力された前記制御電圧と前記参照電圧とを比較し、前記生成部から出力される制御電圧が前記参照電圧に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

クロッククリーンアップ位相ロックループ(PLL)

【解決手段】スプリアスを低減し受信機性能を向上し得るクロッククリーンアップ位相ロックループ(PLL)が述べられる。典型的な一設計では、集積回路はPLL及びアナログ/デジタルコンバータ(ADC)を含む。PLLは、フラクショナル分周比で生成され、突発的周波数ジャンプによるスプリアスを有する第1クロック信号を受信する。第1クロック信号は、集積回路外部のフラクショナルNの周波数シンセサイザによって生成され得る。PLLは、整数の分周比で、低減されたスプリアスを有する第2クロック信号を生成する。ADCは、第2クロック信号に基づいてアナログベースバンド信号をデジタル化してデジタルサンプルを供給する。集積回路は更に、低ノイズ増幅器(LNA)を有し、これは第1クロック信号をクリーンアップするPLLの使用により、集積回路の基板を介して結合するより小さいスプリアスを観測し得る。 (もっと読む)

オシレータ及びオシレーティング信号を生成する方法

【課題】位相同期ループクロック発生器等に好適に使用できるオシレータ及びオシレーティング信号を生成する方法を提供する。

【解決手段】オシレータであって、第1スターブドインバータ(current−starved inverter)と、前記第1スターブドインバータの内部インバータとクロスカップルされる内部インバータを含む第2スターブドインバータと、前記第1スターブドインバータの内部インバータの出力と接続される第1インバータと、前記第2スターブドインバータの内部インバータの出力と接続される第2インバータとを具備し、前記第1インバータの出力は、前記第2スターブドインバータの外部インバータの入力に供給され、前記第2インバータの出力は、前記第1スターブドインバータの外部インバータの入力に供給されることを特徴とする。

(もっと読む)

発振回路、DC−DCコンバータ及び半導体装置

【課題】CPUなどの特別な制御回路が不要で、しかも無線送受信回路で用いている周波数に関わりなく、スイッチングノイズの影響を無視できるレベルまで軽減することが可能な発振周波数制御回路を提供する。

【解決手段】周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、アップダウン制御回路20は、第1の検出回路30がクロック信号のハイレベル又はローレベルの時間が第1の遅延時間以下になったことを検出した場合は、ダウン信号を可変周波数発振回路に出力し、第2の検出回路40がクロック信号のハイレベル又はローレベルの時間が第2の遅延時間以上になったことを検出した場合は、アップ信号を可変周波数発振回路10に出力する。

(もっと読む)

PLL回路および通信用半導体集積回路装置

【課題】スプリアス特性の向上が実現可能なPLL回路およびそれを搭載した通信用半導体集積回路装置を提供する。

【解決手段】例えば、PLL回路を含む高周波ICチップRF_CP3において、PLL回路内に複数の電圧制御発振回路ブロックVCO_BK1〜VCO_BK3を設ける。そして、ループフィルタの一部となる2次のループフィルタFLT_Aを位相検出等を行うシンセサイザブロックSYNに配置し、他の一部となる1次のループフィルタFLT_BをVCO_BK1〜VCO_BK3のそれぞれに配置する。さらに、VCO_BK1〜VCO_BK3のそれぞれにおいては、インダクタL1,L2をRF_CP3の内側でなく外側(外周の一辺)に近くなるような向きにレイアウトする。

(もっと読む)

41 - 60 / 271

[ Back to top ]