Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

61 - 80 / 271

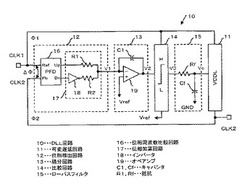

DLL回路

【課題】高精度な同期特性を有するDLL回路を提供する。

【解決手段】第1クロック信号CLK1が入力され、第1クロック信号CLK1を遅延した第2クロック信号CLK2を出力するとともに、制御信号Vcにより遅延時間が可変される可変遅延回路11と、第1クロック信号CLK1および第2クロック信号CLK2が入力され、第1クロック信号CLK1と第2クロック信号CLK2との位相を比較して、その位相差ΔΦに応じた信号を出力する位相検出回路12と、位相検出回路12の出力V1を積分する積分回路13と、積分回路13の出力V2を予め定めた基準値Vrefと比較し、比較結果を出力する比較回路14と、比較回路14の出力V3を平均化し、高周波成分を除去した信号を、制御信号Vcとして可変遅延回路11に出力するローパスフィルタ15と、を具備する。

(もっと読む)

PLL回路、PLL制御方法、情報再生装置およびコンピュータプログラム

【課題】PLL回路の安定動作を実現可能な、PLL回路を提供すること。

【解決手段】VCOと、アナログRF信号をディジタルRF信号に変換して出力するA/D変換部と、VCOが出力するクロックとA/D変換部の出力との位相差を検出して出力する位相差検出部と、直前の出力値に位相差検出部の出力を加算して出力するローパスフィルタと、ローパスフィルタの出力をアナログ信号に変換するD/A変換部と、ローパスフィルタの出力を設定する出力設定部と、を含み、出力設定部は、周期的にローパスフィルタの出力を取得し、出力設定部に所定の信号が入力されると、出力設定部はローパスフィルタの出力を用いてローパスフィルタの出力をPLLのキャプチャレンジの範囲内に強制的に設定する、PLL回路が提供される。

(もっと読む)

PLL回路

【課題】回路や制御を複雑にすることなく、電圧制御発振回路の発振周波数レンジを広く保持しつつ出力クロックのジッターを低減可能なPLL回路を提供すること。

【解決手段】前段のLPF3から入力される制御電圧信号VCTRLの電位に応じた周波数を有する出力クロックを、制御端子に入力される制御電圧に応じて遅延時間が変化する遅延回路のM個を環状に接続したリングオシレータを用いて発生するVCO回路4aを備えるPLL回路において、VCO回路4aは、制御電圧信号VCTRLから低周波帯域の制御電圧信号VCTRLを抽出する低域通過フィルタを備え、前記リングオシレータは、前記M個の遅延回路のうち、m個(m<M)の各遅延回路の制御端子に制御電圧信号VCTRLが入力され、(M−m)個の各遅延回路の制御端子に制御電圧信号VCTRL2が入力される。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

FM受信装置

【課題】ノイズの少ないFM受信装置を提供する。

【解決手段】アンテナと、発振回路と、位相比較回路と、チャージポンプ回路と、ループフィルタと、VCOと、VCO発振信号を所定の周波数ごとに分周し分周発振信号を生成する第1の分周回路と、VCO発振信号を所定の周波数ごとに分周し局部発振信号を生成する第2の分周回路とを備え、VCOはLC共振回路を含まない構成のものであり、分周発振信号を位相比較回路の入力信号とするものであって、局部発振信号と電波の信号より、複数の中間周波数信号を生成するミキサと、中間周波数信号をA/D変換するA/D変換器と、A/D変換器より出力された信号のうち、複数の中間周波数信号に対応するいずれか一つを選択し復調するデジタル復調器と、を備えたことを特徴とするFM受信装置を提供することにより上記課題を解決する。

(もっと読む)

基準信号発生装置

【課題】外部環境による精度低下への影響を低下させ、且つ、ユーザに必要以上の手間を掛けることなく、安定して高精度な基準周波数信号を継続的に出力し続ける。

【解決手段】制御部10は、位相差の平均が、監視閾値未満であるかどうかによって、較正の有無を判定する。ここで、監視閾値は、当該基準周波数信号発生装置1が搭載される通信機器に求められる精度の仕様を満たすとともに、この仕様の限界に対して所定の余裕を持てるような値に設定されている。監視閾値未満の場合、制御部10は、自身で生成した維持用制御電圧信号を電圧制御発振器14へ与え、監視閾値に達する場合、ループフィルタ12からの制御電圧信号を電圧制御発振器14に与え、電圧制御発振器14はこの制御電圧信号に基づいて較正を行う。

(もっと読む)

半導体集積回路装置

【課題】PLL回路におけるジッタを低減しながら、ワイドレンジで安定した動作を行う。

【解決手段】PLL回路のオシレータを構成する遅延バッファ7のインバータ13,14は、電流制限用トランジスタであるトランジスタ8を介して電源電流が供給されている。トランジスタ8は、バイアス電流である入力信号in1に応じてインバータ13,14に供給する電流制限する。このトランジスタ8を設けたことにより、発振周波数の低い帯域における該インバータ13,14に流れるリーク電流を防止することができる。

(もっと読む)

電圧制御発振回路

【課題】出力クロックのスキューを補正でき、不良率を低減できる電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路14は、最終段の出力と最初段の入力とが接続されることによって環状に接続される複数段の遅延回路を備える第1リングオシレータ21と、最終段の出力と最初段の入力とが接続されることによって環状に接続される複数段の遅延回路を備える第2リングオシレータ22と、前記第1、第2リングオシレータにクロスカップル接続される一対の第1、第2反転回路23-1,23-2と、入力が前記第1リングオシレータの出力に接続される第3反転回路と、入力が前記第2リングオシレータの最終段の遅延回路の入力に接続される第4反転回路とを少なくとも備える第1位相合成回路25と、入力が前記第2リングオシレータの出力に接続される第5反転回路と、入力が前記第1リングオシレータの最終段の遅延回路の入力に接続される第6反転回路とを少なくとも備える第2位相合成回路26とを具備する。

(もっと読む)

PLL回路およびシリアルインターフェース回路

【課題】加速用のチャージポンプを並列状に接続したPLL回路について、チャージポンプの出力電圧が定電流領域から外れることでチャージポンプの出力電流の上限値が低く制限されることによるロックイン時間短縮効果の制限や、PLLの帯域が高くなりすぎPLLが不安定になってしまうことによるロックイン時間短縮効果の制限を除去し、より一層ロックイン時間を短縮することを目的とする。特にシリアルデータの伝送を行うインタフェース回路についてSATAのPM復帰の規格を満たすことを目的とする。

【解決手段】本発明の一実施形態に係るPLL回路80は、位相検出器1、チャージポンプ2、ループフィルタ3、電圧制御発振器4を備え、ループフィルタ3は抵抗値が可変であり、チャージポンプ2aと並列動作可能な加速用チャージポンプ2b、加速用チャージポンプ2bの動作およびループフィルタ3の抵抗値可変のタイミングを制御する制御部5を備える。

(もっと読む)

オーディオ参照クロックを生成可能な受信装置

【課題】PLL回路に入力されるリファレンス周波数を高くすることができる受信装置を提供する。

【解決手段】受信装置1は、ピクセルクロックを1/CTSで分周して、第1の信号として出力する第1の分周器11と、商CTSquoの値に対応する周期をN−CTSremに対応する回数分第1の信号の周期内に含み、かつ、CTSquo+1に対応する周期をCTSremに対応する回数分第1の信号の周期内に含む第2の信号を、ピクセルクロックの周期を制御することによって出力する周期制御部21と、周期制御部21から出力される第2の信号によって得られるリファレンス信号に基づいて、所望の周波数にロックされた信号を出力するPLL回路31とを備える。周期制御部21は、CTSremの和を随時計算し、当該和がしきい値N−1をオーバーフローするときに応じて、第2の信号の周期を制御する。

(もっと読む)

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

PLL回路およびそのIC

【課題】 PLL回路としての動作を中断することなく適切な発振信号を出力できるようにする。

【解決手段】 測定時、第1の制御電圧をVCO31に供給する電圧供給回路302と、VCO31の発振周波数を測定する周波数測定回路303とを設ける。使用時、VCO31に供給される第2の制御電圧の大きさを測定する電圧測定回路304を設ける。測定時、電圧供給回路302および周波数測定回路303により、第1の制御電圧とVCO31の発振周波数の変化の割り合いとの関係を示すデータテーブルを作成する。使用時、データテーブルを参照して、電圧測定回路の測定した第2の制御電圧を発振周波数の変化の割り合い示す制御感度に変換する。可変分周回路32の分周比Nにかかわらずオープンループ時の伝達関数が一定となるように、変換結果の制御感度によりチャージポンプ回路34のチャージポンプ電流の大きさを制御する。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】 インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】 インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

位相補間器及びクロックデータリカバリ装置

【課題】本発明は、ミキサの数を減らすことで回路面積及び消費電力を縮小し、位相の不整合を抑制することが可能な位相補間器を提供する。

【解決手段】位相差が0度のクロックD0を与えられミキサ2個分の遅延量を有するクロックD0+2Dcを出力する2ミキサM11、M12、位相差が0度のクロックD0と位相差が90度のクロックD90とを与えられ位相差が45度の遅延量とミキサ2個分の遅延量とを有するクロックD90+2Dcを出力するミキサM1、M13、クロックD0、D90、D45+2Dcのいずれか2つを用いて位相差が所定角度の遅延量とミキサ2個分の遅延量とを有するクロックを生成して出力する少なくとも1つのミキサを備える。

(もっと読む)

バラクタをVCOに使用したPLL回路

【課題】VCOゲインを変化させて、ループゲインを可変可能にするPLL回路を提供すること。

【解決手段】本発明のPLL回路は、切り換え信号により、VCOのゲインが変化し、これにより前記VCOを含むPLL回路のループゲインあるいはループ帯域が変化させるために、2つのインダクタ、2対の逆接続バラクタ及び負性抵抗素子を有するタンク回路、あらかじめ設定された少なくとも2つのDCバイアス電圧を生成し、入力した制御信号に応じて、2つのDCバイアス電圧の一つに対応する静的なDCバイアス電圧が各バラクタに印加されるようにするバイアス回路、及び周波数制御信号を入力してVCOの発信周波数を制御する、バラクタに接続された回路、を備えたVCOを含む。この構成は、制御信号に関する切り替えノイズを発生することもなく、実効的なロックアップ時間の短縮およびロックアップ後の位相雑音の低減に好適である。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】周波数変動の大きな基準発振器を用いて、周波数変動を抑制した局部発振信号及び分周逓倍信号を出力するシンセサイザを小型に実現すること。

【解決手段】本発明のシンセサイザ2は、基準発振器3から出力された基準発振信号を基に局部発振信号を生成して周波数変換部5に入力するとともに、周波数補償部7から出力された周波数補償信号を基に局部発振信号の周波数補償を行うシンセサイザ2であって、局部発振信号を分周又は逓倍した分周逓倍信号を、周波数変換部5の出力側に接続された後段回路部6に入力する分周逓倍部2aを有する。この構成により、シンセサイザ2が周波数変動を補償した局部発振信号を出力するとともに、この局部発振信号を分周又は逓倍して分周逓倍信号を生成することにより、少なくとも1つのシンセサイザで、局部発振信号及び分周逓倍信号の周波数変動を補償することができる。

(もっと読む)

起動制御回路付き水晶発振回路および位相同期回路

【課題】 水晶発振回路が定常発振に達するまでの起動時間を短くすることができる起動制御回路付き水晶発振回路、水晶発振回路の起動時間を短くすることで間欠動作の比率を大きくし、低消費電力化に寄与する位相同期回路を実現する。

る。

【解決手段】 水晶振動子と負性抵抗回路を備えた水晶発振回路の起動制御を行う起動制御回路を含み、一定の発振周波数の信号を出力させる起動制御回路付き水晶発振回路であって、水晶発振回路は、水晶振動子を励振する励振信号を外部から入力するための信号入力端子を備え、起動制御回路は、発振周波数またはそれに近い周波数を有する励振信号を生成し、水晶発振回路の起動時に励振信号を励振信号入力端子に入力し、水晶発振回路の発振周波数が安定する前に励振信号の入力を停止する構成である。

(もっと読む)

位相ロックループ回路及び遅延ロックループ回路

【課題】ジッタの増加を防止し、カットオフ周波数の変動を防止することができる位相ロックループ回路及び遅延ロックループ回路を提供することを課題とする。

【解決手段】リファレンス信号とフィードバック信号との位相を比較し、その位相差を示す位相差信号を出力する位相比較器(101)と、前記位相差信号に応じたチャージポンプ電流を出力するチャージポンプ(102)と、抵抗及び容量を含み、前記チャージポンプ電流を平滑化して制御電圧に変換するローパスフィルタ(103)と、前記制御電圧に応じた周波数の発振信号を生成する電圧制御発振器(104)と、前記発振信号を分周した分周信号を生成し、前記分周信号を前記フィードバック信号として前記位相比較器に出力する分周器(105)とを有し、前記ローパスフィルタ内の抵抗は、前記制御電圧に応じて変化する可変抵抗であることを特徴とする位相ロックループ回路が提供される。

(もっと読む)

周波数および電圧制御回路、電子機器およびネットワーク装置

【課題】PLL回路を搭載する電子機器を低消費電力で運用するモードに切替えるとき、または、高速処理可能な運用モードに切替えるとき、一度回路の処理を止めてから、クロック周波数、電源電圧、MOSFETの閾値電圧を切替える必要があった。また切替えにそれぞれ別の制御回路、手法が必要であった。

【解決手段】PLL回路のループフィルタが出力する電圧値に連動させて電源電圧および、MOSFETの閾値電圧を切替えることによって、クロック周波数を変える動作をさせるだけで、被制御回路の電源電圧およびMOSFETの閾値電圧も切替える。また、PLL回路の応答特性を単調増加もしくは単調減少で緩やかな変化にすることで、回路の動作を止めずにモードが切替えを可能とする。

(もっと読む)

61 - 80 / 271

[ Back to top ]