Fターム[5J106CC59]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相変換回路 (594) | 移相・遅延回路 (564) | 可変移相・遅延回路 (359)

Fターム[5J106CC59]に分類される特許

201 - 220 / 359

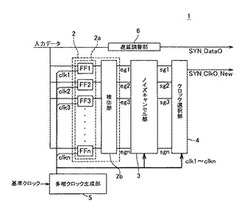

クロックリカバリ回路

【課題】シリアル伝送されるデータにノイズが混入しても、そのノイズの影響を少なくすることができるクロックリカバリ回路を提供する。

【解決手段】基準クロックから多相クロック生成部5で生成された多位相クロックのうち、入力されたシリアルデータの変化点の中間(真中)に立ち上がりがあるクロックを選択して出力するクロックリカバリ回路1において、入力データのエッジを検出した後に、所定以下の信号幅のノイズ成分を除去するノイズキャンセル部3を設け、ノイズ成分によるクロックの切替えが起らないようにしてクロック選択部4へ出力する。

(もっと読む)

多相クロック生成回路およびシリアルデータ受信回路

【課題】位相比較時のオフセットを少なくして高精度で高分解能の等位相多相クロックが生成されるとともに、小回路規模化および低消費電力化が図れる多相クロック生成回路およびシリアルデータ受信回路を提供する。

【解決手段】複数の電圧制御遅延回路2a〜2jを直列接続し、初段の電圧制御遅延回路2aの差動出力から生成される信号F00と、最終段の前段の電圧制御遅延回路2iの差動出力から生成される信号F88Aの逆相の信号であるF00Aとを、位相比較器3で比較し、比較結果をチャージポンプ4、ローパスフィルタ5を経由してバイアス回路から出力する制御電圧信号Pnct,Ncntで信号F00とF00Aとの位相差が無くなるように電圧制御遅延回路2a〜2jの遅延を調整し、電圧制御遅延回路2a〜2jの各差動出力信号からクロック生成部7でシングル信号に変換して等位相の多相クロックを生成する。

(もっと読む)

信号処理システム、記録情報再生システムおよび信号受信システム

【課題】製造コスト上昇を抑える。

【解決手段】信号処理システムであって、制御端子に与えられた制御信号に応じた遅延を、入力端子に入力された信号に与えて出力端子から出力する第1の遅延回路と、前記第1の遅延回路と同様に構成され、入力端子と出力端子とが接続された第2の遅延回路を有し、発振信号を出力する発振器と、前記発振器の発振信号に応じた信号と基準となる信号との間の位相を比較し、比較結果を示す信号を出力する位相比較回路と、前記位相比較回路の出力信号の低周波成分を、前記第1及び第2の遅延回路の制御信号として用いられるように出力するフィルタ回路とを有する。前記第1の遅延回路の入力端子に与えられ、その出力端子から出力された遅延した信号が、前記基準となる信号として前記位相比較回路に与えられている。

(もっと読む)

アナログDLL回路

【課題】遅延の可変量を所望の遅延範囲に設定でき、素子バラツキによる電流変化の影響を低減でき、ジッタ精度の良いクロックを生成できるアナログDLL回路を提供する。

【解決手段】DLL回路を構成するバイアス回路は、第1乃至第3のPMOSトランジスタQ1、Q3、Q5と、第1乃至第3のNMOSトランジスタQ2、Q4、Q6と、定電流源Iと、抵抗Rとから構成されている。定電流源Iは、電源と第2のPMOSトランジスタQ3のドレインとの間に接続されている。この定電流源Iによる定電流を加えてオフセットを持たせることにより、遅延の可変量を所望の遅延範囲に設定でき、ローパスフィルタ出力(Vi)の変化による遅延の変化を小さくすることにより、ジッタ精度の良いクロックを生成できる。

(もっと読む)

位相同期回路

【課題】 簡易な手段で、PLL回路の入力信号と出力信号との位相差(定常位相誤差)を小さくし、同期範囲を拡大すること。

【解決手段】 PLL回路は、基準信号と比較信号との位相差を検出する位相比較器と、ループフィルタと、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号から生成した比較信号を位相比較器にフィードバックする比較信号生成回路とを有している。さらに、PLL回路は、基準信号と比較信号との周波数が同期しているときに、基準信号の位相に対する比較信号の位相の遅延量を検出する誤差検出回路を有している。例えば、比較信号生成回路は、誤差検出回路により検出された遅延量に応じて、出力信号を遅延させ、出力信号から遅延させた信号を比較信号として位相比較器にフィードバックする。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 PVT変動に起因して周波数変調プロファイルが変化することを防止することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 入力クロックCLKINと出力クロックCLKOUTの位相を位相比較記30で比較し、その比較結果信号POに基づいて制御回路20で新たな遅延パターンを算出し、その新たな遅延パターンに従って1クロックパルス毎に遅延セル11_0,11_1,11_2,11_3,…,11_N−2,11_N−1,11_Nの段数を切替信号S[0],S[1],S[2],S[3],…,S[N−2],S[N−1],S[N]により切り替えながら入力クロックCLKINを入力させて周波数変調を行なう。

(もっと読む)

可変遅延回路、可変遅延装置およびVCO回路

【課題】入力信号に対して小さな遅延時間の制御を行うことができる可変遅延回路、可変遅延装置及びVCO回路を提供する。

【解決手段】可変遅延回路は、入力信号を遅延させるトランスファゲートTG1およびトランスファゲートTG3と、トランスファゲートTG1およびトランスファゲートTG3と入力信号との間に設けられるトランスファゲートTG2およびトランスファゲートTG4と、を備えている。

(もっと読む)

位相比較回路

【課題】遅延時間が短く、しかも、メタステーブルが起こった場合において確実に後段回路の誤動作を防ぐことができる位相比較回路を提供する。

【解決手段】D-F/F21は外部クロック信号CLK1を制御クロック信号RCLKに基づいて読み込む。インバータINVA1、INVB1はスレショルドレベルが異なるインバータであり、インバータ22の出力を反転して出力する。インバータINVA2、INVB2はヒステリシス特性を有するインバータであり、インバータINVA2、INVB2の出力を反転して出力する。EX-NOR回路30、Dラッチ31、アンドゲート32は、インバータINVA2、INVB2の出力が一致している時、遅延回路33の出力をD-FF23および遅延回路34へ加え、一致していない時はオフとする。D-F/F23はアンドゲート32を介して供給される制御クロック信号RCLKの遅延信号に基づいてインバータ22の出力を読み込み出力する。

(もっと読む)

位相補間器

【課題】プロセス条件、電源電圧、温度の変動によらず、微小な位相をプログラマブルに調整できる位相補間器を提供する。

【解決手段】PLL回路のフィードバック信号(FBCLK)に非等間隔なクロックを入力し、PLL回路が本来備える位相合せ機能により、基準信号REFCLKとフィードバック信号FBCLK間に微小な位相差を与え、かつ、アップ、ダウン電流が等しいチャージポンプ(CP)回路を用いてプロセス条件、電源電圧、温度依存性が無い位相差を実現する。

(もっと読む)

位相調整回路および位相調整方法

【課題】 VCOの出力に生じている周波数変動を動的に補正し、これによりロングタームジッタを削減することが可能な位相調整回路の提供。

【解決手段】 周波数比較部12において、基準クロックRIN1の分周クロックREF1の周波数とフィードバッククロックFIN1の分周クロックFB1の周波数を測定および比較し、位相調整部13において、周波数比較部12の比較結果により、FB1の周波数がREF1より高ければカウンタ13−1をカウントアップして可変遅延回路13−2の遅延量を増やし、FB1の周波数がREF1より低ければカウンタ13−1をカウントダウンして可変遅延回路13−2の遅延量を減らす。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

シフタ及び加算器を利用して遅延時間を調節する遅延固定ループ及びクロック遅延方法

【課題】シフタ及び加算器を利用して遅延時間を調節する遅延固定ループを提供する。

【解決手段】第1入力クロックの1クロック周期に対応する第1デジタル値を出力するマスタ遅延固定ループと、第1デジタル値を受信し、第1入力クロックの1クロック周期より短い時間ほど第2入力クロックを遅延させて出力するスレーブ遅延固定ループとがある。該スレーブ遅延固定ループは、シフタ136、演算器138及び可変遅延回路132を備え、該シフタ136は、第1デジタル値をシフトして第2デジタル値として出力し、該演算器138は、第2デジタル値に、工程、電圧及び温度(PVT)によって変化するオフセット値を加算または減算して第3デジタル値として出力し、該可変遅延回路132は、第3デジタル値に対応する時間ほど第2入力クロックを遅延させて出力する。

(もっと読む)

デューティサイクル補正機能を有する遅延ロックループ回路およびその制御方法

【課題】PVT変動が発生しても安定して正確な遅延ロックおよびデューティサイクル補正を可能とする。

【解決手段】外部クロックが入力されて第1内部クロックを生成し、前記第1内部クロックを内部の遅延手段によって遅延して複数の第2内部クロックを出力した後にフィードバックを受けて、前記第1内部クロックとの位相差によって前記遅延手段の遅延時間を調整することにより、前記第2内部クロックの遅延ロックがなされるようにする遅延ロックループブロックと、前記複数の第2内部クロックのデューティサイクルを補正したデューティサイクル補正クロックを出力するデューティサイクル補正ブロックと、前記複数の第2内部クロックの位相比較結果に応じてデューティ補正エラーの発生を判断して、前記デューティサイクル補正クロック又は前記複数の第2内部クロックのうちの1つを前記遅延ロックループブロックにフィードバックするエラー判断部とを備える。

(もっと読む)

電圧制御遅延装置およびDLL回路

【課題】 サンプル毎にトランジスタなどの構成素子の特性がばらついたとしても、すべてのサンプルにおいて制御電圧―遅延時間特性がばらつきの影響を受け難い電圧制御遅延装置を提供する。

【解決手段】 本発明の電圧制御遅延装置は、入力された制御電圧を電流に変換する電圧電流変換部108を含み、該電圧電流変換部108により変換された電流に比例した制御電流を出力する制御手段と、入力信号を前記制御電流に応じた時間だけ遅延させて出力する遅延手段とを備え、前記電圧電流変換部108は、所定の入力電圧範囲において線形の電圧電流変換特性を有している。

(もっと読む)

クロック発生回路

【課題】 DLL回路を用いたクロック発生回路においては、活性化される半導体装置が切り替わる場合に、DLL回路のロック時間が長くなるという問題がある。

【解決手段】 DLL回路の遅延調整回路を固定長遅延回路と、N個の可変長遅延回路で構成し、N個の半導体装置に内部クロックを供給する。N個の可変長遅延回路の遅延差をN個の半導体装置に対する遅延差と同じくする。選択された半導体装置に対し、遅延差がなくなるようにN個の可変長遅延回路からの遅延クロックを選択する。

(もっと読む)

CASレイテンシを利用してロッキングレゾリューション調節が可能な遅延同期ループ回路

【課題】単位遅延器の数を増やさなくとも広いロッキング範囲を有し、またロッキングサイクル時間を減らせる遅延同期ループ回路を提供する。

【解決手段】遅延ライン、位相検出器、制御回路を備える。遅延ラインは、直列連結された多数の単位遅延器を含んで制御信号に応答して選択される単位遅延器を通じて外部クロック信号を遅延させる。位相検出器は、前記外部クロック信号の位相と前記遅延ラインから出力される内部クロック信号の位相とを比較し、外部クロック信号と遅延ラインから出力される内部クロック信号間の位相差を検出する。制御回路は、前記位相検出器の出力信号に応答して前記制御信号を発して遅延制御信号に応答して前記遅延ラインのロッキング位相ステップを可変にする。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。  (もっと読む)

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、より向上したデューティ比特性を持つクロックを出力するDLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、立ち上りクロックのデューティ比及び立ち下りクロックのデューティ比を感知して、デューティ比感知信号を出力するデューティ比感知ユニットと、デューティ比感知信号に応じて、補正制御信号を生成する補正制御ユニットと、補正制御信号に応じて、内部クロックのデューティ比を補正し、基準クロックを出力するデューティ比補正ユニットとを含むことを特徴とする。

(もっと読む)

クロック位相シフト回路

【課題】プロセス条件、電源電圧、温度等の変動によらず、入力クロックの位相シフトの調整ができ、かつ、従来のDLL回路を用いた場合と比較して占有面積の小さいクロック位相シフト回路を提供する。

【解決手段】入力クロックを遅延させる遅延回路の遅延セルと同一の遅延セルで構成されたリングオシレータを用いて、入力クロックのm周期分の発振出力をカウントし、入力クロックの1周期分の遅延セル段数を計算して位相シフト量分の遅延セル段数を設定する。

(もっと読む)

201 - 220 / 359

[ Back to top ]