Fターム[5J106CC59]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相変換回路 (594) | 移相・遅延回路 (564) | 可変移相・遅延回路 (359)

Fターム[5J106CC59]に分類される特許

161 - 180 / 359

信号発生システム

【課題】サンプリング周波数変更時も、第1及び第2信号発生装置の出力信号間の位相関係を維持できるようにする。

【解決手段】第1及び第2信号発生装置は、専用ケーブルで結合され、サンプリング・クロック、シーケンス・クロック、トリガ/イベント信号が第1信号発生装置から第2信号発生装置に供給される。また、両装置のCPUは、ケーブルを介して情報を交換する。専用ケ―ブルのため、ケーブル及び周辺回路を含めた通信手段における通信遅延量は、既知で一定である。第1又は第2信号発生装置のCPUは、サンプリング周波数が変更されると、通信遅延量に相当するサンプリング・クロックのクロック数と位相を計算する。この計算値に応じて、第1信号発生装置の遅延回路130は波形データをサンプリング・クロック単位で遅延し、第2信号発生装置の位相調整回路216及び218は波形データをサンプリング・クロックの位相レベルで遅延する。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

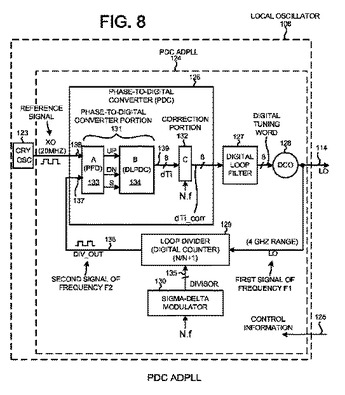

自己訂正する位相デジタル伝達関数を有する位相ロックループ

位相ロックループは、位相デジタル変換器部分、ならびに新規訂正部分を含む。位相デジタル変換器(PDC)部分は、第1の位相誤差ワードのストリームを出力する。新規訂正部分は、第1の位相誤差ワードを受け取り、そしてループフィルタへと供給される第2の位相誤差ワードのストリームを生成する。PDC部分は、ある種の不完全性を示す位相デジタル伝達関数を有する。第1の例においては、訂正部分は、第1の位相誤差ワードの対の間の平均差を決定し、そして遅延要素伝搬遅延の変化に起因したPDC部分の伝達関数の傾斜における変化について訂正するために第1の位相誤差ワードを正規化するためにこの平均差を使用する。第2の例においては、訂正部分は、PDC部分の伝達関数における利得ミスマッチについて訂正する。第3の例においては、訂正部分は、PDC部分の伝達関数におけるオフセットミスマッチについて訂正する。  (もっと読む)

(もっと読む)

遅延制御回路及び遅延制御方法

【課題】遅延制御回路における定常位相誤差を排除できる構成の提供。

【解決手段】第1の可変遅延回路及び第1の位相制御回路を備えた遅延制御回路において、更に、第1、第2のクロックパスのいずれか一方に配された第2の可変遅延回路と、前記第2の可変遅延回路に対する遅延値を用いて、前記第1のクロックパス又は第2のクロックパスに対し、前記第1の位相調整回路にて発生する定常位相誤差を相殺する追加のフィードバックループを形成するよう配設される第2の位相調整回路と、を備える。

(もっと読む)

DLL回路,撮像装置,メモリ装置

【課題】DLL回路における正常ロック状態の安定性を向上させる。

【解決手段】可変遅延回路10は、入力クロックCKinを順次遅延させ、それぞれ位相が異なる遅延クロックCK(1),・・・CK(k)を生成する。位相比較回路11は、遅延クロックCK(n−m),CK(n+m)の立ち上がりエッジ間の期間を有効期間として規定し、その有効期間中においてのみ遅延クロックCK(1),CK(n)のそれぞれの電圧レベルに基づいて位相比較する。遅延制御回路12は、位相比較回路11による比較結果に基づいて、可変遅延回路10における遅延時間を制御する。

(もっと読む)

DLL回路およびその制御方法

【課題】より迅速な固定完了時間を有し、半導体集積回路の高速化実現をより効率的に支援するDLL回路およびその制御方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックと動作開始信号に応答して初期動作信号を生成する初期動作設定手段と、前記初期動作信号、位相比較信号、および初期設定コードに応答して遅延制御コードを生成するシフトレジスタと、前記初期動作信号および前記遅延制御コードに応答して前記基準クロックまたはフィードバッククロックを遅延させ、複数の単位遅延クロックを生成する遅延ラインと、前記基準クロックと前記複数の単位遅延クロックに応答して前記初期設定コードを生成する初期遅延モニタリング手段とを含むことを特徴とする。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を設定された遅延量だけ遅延して出力する遅延線路と、出力端子から出力される第2のクロック信号と第1のクロック信号との位相差に基づいて、遅延線路の遅延時間長を設定する遅延時間長設定部と、第1のクロック信号と第2のクロック信号の位相関係が特定の位相関係にあるか否かを検出する位相関係判定部と、特定の位相関係の検出時、遅延線路を含む伝搬経路上の第1のクロック信号を位相反転する位相反転/非反転部とで構成する。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティ比特性を有するクロックを生成する。

【解決手段】本発明は、デュアルループタイプ(Dual Loop Type)のDLL回路であって、第1位相検知信号に応答し、第1遅延制御信号を生成して第1遅延ラインの遅延量を制御し、第1遅延量情報信号を出力する第1遅延制御手段と、第2位相検知信号に応答し、第2遅延制御信号を生成して第2遅延ラインの遅延量を制御し、第2遅延量情報信号を出力し、前記第1遅延制御信号と半周期情報信号に応答して前記第2遅延ラインの遅延量を再び制御する第2遅延制御手段と、前記第1遅延量情報信号と前記第2遅延量情報信号の入力を受け、基準クロックの半周期情報を抽出して前記半周期情報信号を生成する半周期検知手段と、前記第1遅延ラインの出力クロックと前記第2遅延ラインの出力クロックを組み合わせてデューティ比補正クロックを出力するデューティーサイクル補正手段とを含む。

(もっと読む)

信号生成回路

【課題】基準クロックの周期より細かい周期で制御された複数の出力信号を出力する信号生成回路を提供する。

【解決手段】本発明にかかる信号生成回路は、基準クロックを出力する状態と、基準クロックに基準クロックの1周期より短い第1時間の遅延を持たせた信号を出力する状態と、を切り換え可能な入力段遅延回路10と、入力段遅延回路10の出力が変化した時点から入力段遅延回路10の出力を基準クロックの1周期より短い第2時間保持するゲート回路33を有し、ゲート回路33の出力に対応する信号を出力する制御部30と、制御部30の出力信号に第2時間の遅延を持たせた信号を出力する出力段遅延回路20と、を備え、入力段遅延回路10は、制御部30の出力信号の変化に応答して出力状態の切り換えを行う。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

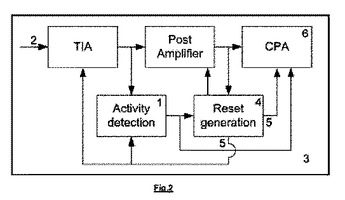

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

遅延固定ループ

【課題】ノイズの干渉、PVTの変動、及び頻繁に起こるパワーダウンモードへの進入・脱出など、半導体メモリ素子の最悪の状況でも安定的に動作できる遅延固定ループを提供すること。

【解決手段】遅延固定をなすために、ソースクロックの第1のクロックエッジ及び第2のクロックエッジに対応する第1の遅延クロック及び第2の遅延クロックを生成する遅延固定部と、前記第1の遅延クロックと第2の遅延クロックとの位相差を検出して加重値選択信号を出力する位相検出部と、前記第1の遅延クロックと第2の遅延クロックとの遅延固定時点から予定された期間に獲得した前記加重値選択信号を格納する加重値格納部と、該加重値格納部に格納された加重値選択信号に対応する加重値を反映し、前記第1の遅延クロックの位相と第2の遅延クロックの位相とを混合して遅延固定ループクロックとして出力する位相混合部とを備えることを特徴とする。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】クロック生成回路が、ロック状態とは180°位相のずれた状態(擬似ロック状態)の出力クロックを出力する可能性がある。

【解決手段】遅延同期ループ型のクロック信号生成回路として、(a)第1のクロック信号を遅延して第2のクロック信号を生成する遅延線路と、(b)第2のクロック信号が第1のクロック信号に位相同期するように、遅延線路における遅延量を可変制御する遅延量制御部と、(c)第1のクロック信号と第2のクロック信号との擬似ロック状態を検出する擬似ロック検出部と、(d)擬似ロック状態の検出時、遅延線路の遅延量を変更する擬似ロック状態解除部とを有するものを提案する。

(もっと読む)

マルチチャネル・データ検出システム用に構成されたエラー組み合わせ論理およびエラー信号を生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの位相エラー組み合わせ論理を提供することにある。

【解決手段】 この位相エラー組み合わせ論理は、各チャネルに関する位相エラー情報を受信することと、受信位相エラー情報を結合し、結合された位相エラーを生成するように構成された組み合わせ論理と、結合された位相エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された位相エラー出力とを含む。さらに、エラー信号組み合わせ論理は、各チャネルに関するフェーズ・ロック・ループに関連する信号のエラー情報を受信することと、受信エラー信号情報を結合し、結合されたエラー信号を生成し、たとえば、信頼性情報により、各チャネルからの受信エラー信号情報に重みを付けるように構成された組み合わせ論理とを含む。エラー補償出力は、結合され重みが付けられたエラー信号を少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成される。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

データ駆動回路及び遅延固定ループ回路

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず正常に動作可能なデータ駆動回路及び遅延固定ループ回路を提供する。

【解決手段】第1のデータ信号を第2のクロック信号に基づいてサンプリングし、アナログ変換することにより得られた第2のデータ信号を出力するデータ駆動部と、第2のデータ信号の変化開始時点から所定期間内であることを知らせるマスク信号を生成するマスク信号生成部と、第1のクロック信号から第2のクロック信号−第1のクロック信号と第2のクロック信号の間には遅延が存在し、該遅延は前記第1のクロック信号と第2のクロック信号の間の位相差に応じて変化し、位相差に応じる前記遅延の変化は前記マスク信号により遮断される−を生成する遅延固定ループと、を備える。

(もっと読む)

データ駆動回路及び遅延固定ループ

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず、正常に動作可能なデータ駆動回路及び遅延固定ループの提供。

【解決手段】第1のクロック信号の入力を受けて第2のクロック信号を出力する遅延固定ループにおいて、前記第1のクロック信号、前記第2のクロック信号及び少なくとも一つの遅延信号によって位相差信号-前記第1のクロック信号又は前記第2のクロック信号によって前記第1のクロック信号と前記第2のクロック信号の間の位相差に該当する値を有し、前記少なくとも一つの遅延信号によって位相差無しに該当する値を有する-を出力する位相検出器21と、前記第1のクロック信号を遅延させることにより前記第2のクロック信号及び前記少なくとも一つの遅延信号を求める遅延線23-前記第1のクロック信号に対する前記第2のクロック信号の遅延は前記位相差信号により変更される-と、を備える。

(もっと読む)

タイミング制御回路及び半導体記憶装置

【課題】プロセスや動作環境等の変化に対して、遅延変動の小さいタイミングを生成しアクセス時間を短縮可能とする、タイミング制御回路及び該タイミング制御回路を備えた半導体記憶装置を提供する。

【解決手段】周期T1を持つ第1のクロック信号と、周期T2の第2のクロック群(CKb)が入力され、疎調遅延回路(CD)と微調遅延回路(FD)を備え、疎調遅延回路(CD)は活性化信号の活性化から第1のクロック信号の立ち上がりエッジをカウントするカウンタを有し、第1のクロック信号からの遅延量がほぼm・T1である疎調タイミング信号(CT)を生成し、微調遅延回路(FD)はL個の並列した多相クロック制御遅延回路からなり、それぞれL相の第2のクロック群による疎調タイミング信号(CT)のサンプリングのタイミングをn・(T2/L)だけ遅延させ、遅延されたパルスのORをとることで微調タイミング信号(FT)とする。

(もっと読む)

ジッタ検出回路及び半導体装置

【課題】サイクルトゥサイクルジッタの程度を検出する。

【解決手段】PLL回路(2)の発振クロック信号(vco)の遅延信信号を基準クロック信号(ref)の複数の遅延信号の変化に同期して複数のラッチ回路(23_1〜23_n)にラッチする。ラッチ回路毎にその出力又はその反転信号をセレクタ(24_1〜24_n)で選択する。セレクタ毎にその出力の変化回数をカウンタ(25_1〜25_n)で計数する。制御回路(28)は、発振クロック信号の2nサイクル毎に、前回のセレクタの選択が非反転出力であれば今回カウンタの計数値がn以上のときセレクタの選択状態を反転し、前回のセレクタの選択が反転出力であれば今回前記カウンタの計数値がn以上のときにセレクタの選択状態を反転する。前記第1カウンタの計数値が例えばジッタ検出情報として出力される。

(もっと読む)

半導体装置及びその駆動方法

【課題】デューティ補正クロック及びその反転クロックが実質的に正確に180度の位相差を有して出力可能な半導体装置のデューティ補正回路を提供すること。

【解決手段】本発明の半導体装置は、第1クロックと、第2クロックと、前記第1、第2クロックのデューティを補正するための信号である補正信号とを受信し、前記補正信号に基づいて前記第1、第2クロックのデューティに対してデューティ比が補正された第1出力クロック及び第2出力クロックを出力するデューティ比補正回路と、前記第1出力クロックの所定の基準遷移時点と前記第2出力クロックの所定の基準遷移時点との間隔に相当する情報をもつ前記補正信号を形成して前記デューティ比補正回路に出力するクロックエッジ検出部とを備える。

(もっと読む)

161 - 180 / 359

[ Back to top ]