Fターム[5J106CC59]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相変換回路 (594) | 移相・遅延回路 (564) | 可変移相・遅延回路 (359)

Fターム[5J106CC59]に分類される特許

101 - 120 / 359

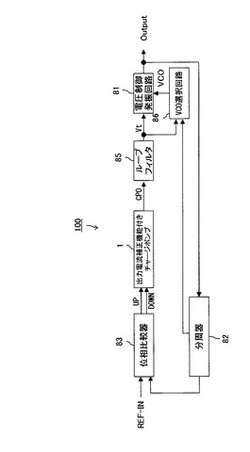

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

クロックデータリカバリ回路および逓倍クロック生成回路

【課題】データ入力の位相変化に対する受信マージンの減少を抑止でき、誤受信の確率の増大を抑止できるクロックデータリカバリ回路および逓倍クロック生成回路を提供する。

【解決手段】入力データと抽出クロックの位相差を検出して位相差に応じたアナログ量を出力する第1の位相検出器110と、ループフィルタ150と、第1の位相検出器の出力に応じてループフィルタから電流を充電または放電するチャージポンプ130,140と、VCO160と、入力データと抽出クロックの位相差の極性を検出する第2の位相検出器120と、第2の位相検出器の検出結果に応じて第1の位相検出器がもつ位相オフセットを相殺する補正位相情報を発生する補正位相情報発生部210と、補正位相をループ200に加算する補正位相加算部220と、を有し、補正位相加算部220は、チャージポンプの充電電流と放電電流を相対的に変化させる。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

DLL回路

【課題】LPF出力の変化に対するロック周波数の変化量のゲイン設定のばらつきの抑制でジッタ精度をより向上できるDLL回路の提供。

【解決手段】遅延クロックを生成する遅延回路101と、遅延クロックと入力クロックの位相差信号を出力する位相比較回路10と、位相差信号対応の位相差電圧を出力するチャージポンプ回路20と、チャージポンプ回路出力の高周波成分を除去するローパスフィルタ回路30と、ローパスフィルタ回路の出力電圧を電流に変換する第1電圧−電流変換回路40及び基準電圧Vrefを電流に変換する第2電圧−電流変換回路50を含み、第1電圧−電流変換回路の出力電流から第2電圧−電流変換回路の出力電流を減算した結果を変換した電圧とオフセット電流Idを変換した電圧とを含み、位相差電圧が基準電圧より小の場合、オフセット電流を変換した電圧を制御電圧Vcontとして遅延回路に出力する遅延制御回路102と、を備える。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

デューティ検出回路及びこれを備えるクロック生成回路、並びに、半導体装置

【課題】デューティ検出信号を高頻度に更新する。

【解決手段】内部クロックRCLK,FCLKのデューティを検出する複数のデューティ検出部210−1〜210mと、複数のデューティ検出部を互いに異なる位相で動作させる制御部220と、複数のデューティ検出部からのデューティ検出信号を選択する出力選択部230とを備える。本発明によれば、複数のデューティ検出部が互いに異なる位相で動作することから、各デューティ検出部におけるデューティ検出信号の生成頻度よりも高頻度でデューティ検出信号DCCSを出力することが可能となる。このため、本発明によるデューティ検出回路をDLL回路のクロック調整に使用すれば、DLL回路の制御周期を短縮することが可能となる。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

クロック位相調整回路

【課題】実装面積や消費電力を低減させることができるクロック位相調整回路を提供すること。

【解決手段】n個の第1の遅延素子15を多段に接続し、入力クロック信号INCLKをその周期の1/nずつ遅延させたクロック信号をそれぞれ出力するDLL回路2と、n個の第1の遅延素子15から出力されるクロック信号のうち1つのクロック信号を選択して出力する第1のセレクタ回路3と、この第1のセレクタ回路3から出力されるクロック信号CLK1を遅延させる遅延部4を備えている。遅延部4は、1又は複数の直列に接続された遅延回路20を有しており、この遅延回路20は、前段の遅延回路10に設けられた第1の遅延素子15の遅延量に対して1/2の遅延量を有する第2の遅延素子21と、入力されたクロック信号CLK1と第2の遅延素子21により遅延されたクロック信号のいずれかを選択して出力する第2のセレクタ回路22とを備える。

(もっと読む)

遅延ロックドループ回路

【課題】原理的に定常ジッタがなく、基準クロック信号のデューティ比にかかわらず高精度な遅延クロック信号を生成可能な遅延ロックドループ回路を実現する。

【解決手段】遅延素子(10)は、基準クロック信号の立ち上がり(又は立ち下がり)から、ループフィルタ(40)の出力に基づいた量だけ遅延して変化する遅延クロック信号を生成する。信号生成回路(20)は、基準クロック信号の立ち上がり及び立ち下がり並びに遅延クロック信号の変化に応じて相補的に変化する二つの信号を生成する。チャージポンプ回路(30)は、ループフィルタ(40)に対して、これら二つの信号に従って、基準クロック信号の立ち上がり(又は立ち下がり)から遅延クロック信号の変化までの間プッシュ動作(又はプル動作)を、遅延クロック信号の変化から基準クロック信号の立ち下がり(又は立ち上がり)までの間プル動作(又はプッシュ動作)を行う。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

半導体装置

【課題】従来のデューティ検出回路では、キャパシタに対するプリチャージ後の充放電動作が、通常のデューティ検出動作中の充放電動作とは異なるものとなり、正確なデューティ検出ができなかった。

【解決手段】内部クロック信号CLKがハイレベルを取る期間とロウレベルを取る期間との比(デューティ比)を積算し、電気的に記憶する記憶部(キャパシタC1,C2)と、記憶部(キャパシタC1,C2)における積算動作(デューティ検出動作)を制御する積算動作制御回路42と、一端が積算動作制御回路42と接続され、他端が電源線(VDD,GND)に接続された定電流回路(バイアストランジスタBTr1,BTr2)と、積算結果を初期化するプリチャージ回路43とを備え、プリチャージ回路43による初期化の実施中に電流回路(バイアストランジスタBTr1,BTr2)に電流を流すようにする。

(もっと読む)

クロック分周回路、及びクロック分周方法

【課題】動作回路の通信タイミングを考慮すると共に、分周時に出力クロック信号の位相調整が可能なクロック分周回路、及びクロック分周方法を提供することである。

【解決手段】本発明にかかるクロック分周回路100は、入力クロック信号(クロックS)のクロックパルスと、通信タイミング信号26と、位相調整信号60に応じて生成されたリセット値81と、に基づき、入力クロック信号に対する通信タイミングの相対的な位相を示すカウント値55を生成し、カウント値55に基づき入力クロック信号のM個のクロックパルスのうち通信タイミング以外のクロックパルスに対してクロックパルスをマスクするマスク信号25を生成するマスク制御回路20を有する。更に、マスク信号25に応じて入力クロック信号のクロックパルスをマスクするマスク回路10を有する。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

デジタル位相ロック・ループ(DPLL)、デジタル位相ロック・ループ(DPLL)内のジッタを制御するための方法、デジタル制御発振器(DCO)内のディザを最適化するための方法、および自己ディザリング・デジタル制御発振器(DCO)回路

【課題】 デジタル位相ロック・ループ(DPLL)および方法を提供する。

【解決手段】 デジタル位相ロック・ループ(DPLL)および方法は、入力として基準クロックを受け取り、ディザリングした基準クロック信号を出力するように構成された調整可能遅延線を含む。位相周波数検出器(PFD)は、ディザリングした基準クロック信号をフィードバック・クロック信号と比較して、ディザリングした基準クロック信号とフィードバック・クロック信号との位相および周波数の差を決定するように構成される。デジタル制御発振器(DCO)は、PFDから早遅判断を受け取り、それに応じて出力を調整するように構成され、ディザリングした基準クロック信号はDPLLの全体的な動作を強化するためにジッタ応答を分散する。

(もっと読む)

位相混合回路及びそれを備える遅延固定ループ回路

【課題】PVTが変動してもジッタの増加を防止する位相混合回路及びそれを備えた遅延固定ループ回路を提供する。

【解決手段】位相制御信号に応答して第1入力信号及び第2入力信号の位相を混合し、単位位相値の自然数倍分だけの位相が可変される位相混合信号を出力する位相混合部と、PVT変動情報を含むPVTコード信号に応答して前記単位位相値を調整する位相値調整部とを備える。

(もっと読む)

DLL回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】短時間でロックさせることが可能なDLL回路を提供すること。

【解決手段】外部クロックCKと内部クロックLCLKの立ち上がりエッジの位相を比較する位相判定回路111と、外部クロックCKと内部クロックLCLKの立ち下がりエッジの位相を比較する位相判定回路112と、判定結果に基づいて内部クロックLCLKR,LCLKFのアクティブエッジの位置を調整する調整部120と、内部クロックLCLKR,LCLKFのアクティブエッジの調整方向とが互いに同方向であることに応答して内部クロックLCLKR,LCLKFの調整量の一方を他方よりも大きくする制御回路150とを備える。これにより、位相調整しながらデューティを50%に近づけることが可能となることから、DLL回路のロックに要する時間を短縮することが可能となる。

(もっと読む)

クロックデータリカバリ回路

【課題】簡単な回路で高データレートおよび低データレートに対応させる。

【解決手段】クロック信号CLK0、CLK1のエッジに係るタイミングt1、t2、t3(ただし、t2<t1<t3)でサンプリングした入力データ信号DATAINの論理値をそれぞれD1、D2、D3とする時、D1≠D2であるか、D1≠D3であるかを検出する検出回路11と、検出回路11の検出結果に基づいて、入力データ信号DATAINの論理値の遷移タイミングがタイミングt2、t3に一致するようにクロック信号CLK0、CLK1の位相を変化させるクロック発生回路14と、を備える。

(もっと読む)

適応的遅延調整を有する位相補間器

【課題】参照信号と補間信号間の位相関係を確実に保持し、より小さく、より簡単な構成の装置を実現するために応用可能な位相補間器を提供する。

【解決手段】位相補間器は、2つの可調整遅延器30及び31、可調整遅延器30で遅延された信号と可調整遅延器31で遅延された信号との位相差を検出する位相比較器32、位相比較器32の出力を積分する積分器33、可調整遅延器30及び31の制御電圧を設定する乗算器34−1、34−2を備える。位相比較器32と積分器33を備えるフィードバックループは、可調整遅延器30の遅延量を制御し、{ACK1、ACK2}及びICK間の位相関係を確実に保持し、安定なICK位相を実現する。

(もっと読む)

101 - 120 / 359

[ Back to top ]