Fターム[5J106CC59]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相変換回路 (594) | 移相・遅延回路 (564) | 可変移相・遅延回路 (359)

Fターム[5J106CC59]に分類される特許

61 - 80 / 359

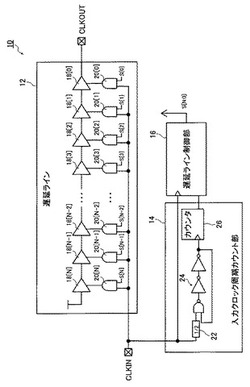

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

位相同期ループのジッタ検出方法及び装置

【課題】別途のジッタ計測装備を使用せずとも位相同期ループのジッタ水準を検出できる位相同期ループのジッタ検出方法及び装置を得る。

【解決手段】基準クロックとフィードバッククロックとの位相差信号を検出し、その位相差信号によって一定の周波数の発振信号を生成する位相同期ループと、入力遅延制御信号によって多数のキャパシタをスイッチングし、前記位相同期ループからの前記位相差信号を前記遅延制御信号によって遅延させる可変位相遅延部と、前記位相同期ループからの前記位相差信号と前記可変位相遅延部によって遅延された位相差信号とを比較し、前記位相差信号の遅延期間を検出する比較部と、前記比較部から検出された遅延期間以後にロック範囲内に位置することを検出するロック検出部とを備える。

(もっと読む)

ジッタ除去回路

【課題】従来では、基準クロック生成回路が生成するクロックにジッタが発生するという問題があった。

【解決手段】本発明にかかるジッタ除去回路は、基準クロック51のジッタを除去するジッタ除去回路であって、サンプリングクロック52に同期して基準クロック51のエッジを検出するラッチ回路12と、基準クロック51のエッジ間隔をカウントするカウンタ13と、各エッジ間隔のカウント数に基づいて基準クロック51の位相を調整する位相調整回路14と、を備える。

(もっと読む)

クロックデータリカバリー回路およびその動作方法

【課題】回路規模および消費電力を削減すること。

【解決手段】クロックデータリカバリー回路3では、クロック発生器300のサンプリングクロックに応答してA/D変換器301がA/D変換し、順次生成の複数のデジタル出力信号はデータ補正部303に供給され、順次生成の複数の補正デジタル信号は位相比較器305に供給される。位相比較器305の出力はループフィルタ306を介してタイミング生成部304に供給され、複数の再サンプリングタイミングの情報Pvcoはデータ補正部303に供給される。検出回路302はアナログ入力信号の周期Tとサンプリングクロックの周期tの比T/tの誤差情報nvcoを生成して、タイミング生成部304は複数の遅延時間で複数の再サンプリングタイミングを生成して、データ補正部303は複数の補正率で複数の補正デジタル信号を生成する。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

バーストデータ再生装置

【課題】バーストデータからクロックを抽出してデータの再生を行うバーストデータ再生装置を得ること。

【解決手段】入力バーストデータ、ICLK、θCLKを入力し、入力バーストデータとICLKとの間の比較結果を出力する周波数位相比較部1と、入力バーストデータとICLKとの比較結果に基づいて準同期状態または非準同期状態を示す検出信号を出力する準同期状態検出部2と、比較結果を平滑化するループフィルタ部3と、準同期状態の場合は非準同期状態の場合よりも小さな利得でループフィルタ部3の出力信号を増幅する線形利得可変増幅部4と、線形利得可変増幅部4の出力信号に基づいてICLKおよびθCLKを生成する多位相型電圧制御発振部5と、入力バーストデータを遅延させる遅延調整部6と、遅延調整後の入力バーストデータとICLKに基づいてデータを再生する識別部7と、を備える。

(もっと読む)

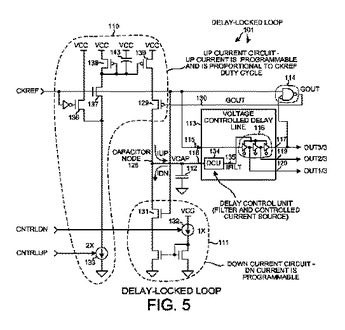

入力信号デューティサイクル変動に依存しない遅延を有する遅延ロックループ

遅延ロックループ(DLL)は、第1の信号を「遅延時間」だけ遅延させ、それによって第2の信号を生成するために、遅延線を使用する。キャパシタは、第1の信号の第1のエッジで開始して第2の信号のエッジまで続く第1の率で充電される。次いで、キャパシタは、第1の信号の別のエッジまで第2の率で放電される。制御ループは、キャパシタが充電される量が、キャパシタが放電される量と同じであるように、遅延時間を制御する。遅延時間は、一定であり、第1の信号のデューティサイクルの変動に実質的に依存しない。一例では、デューティサイクル歪み相殺(duty cycle distortion cancellation)は、第1の信号のデューティサイクルの変化に対して比例して第1の率を変更することによって達成される。別の例では、第1の率および第2の率は、第1の信号のデューティサイクルに依存しない。  (もっと読む)

(もっと読む)

PLL回路および電子機器

【課題】PLL回路の回路規模の増大を抑制しながら、安定性と周波数引込み速さとを独立に設定可能にする。

【解決手段】PLL回路1は、信号を遅延する遅延閉ループ19により発振信号を生成するリング発振部2と、位相比較部3、チャージポンプ4、平滑フィルタ5、平滑電流源6、遅れ成分フィルタ7、および補正電流源8を有する。遅れ成分フィルタ7は、平滑フィルタ5と並列にチャージポンプ4の出力に接続され、チャージポンプ4の出力信号に含まれる応答遅れ成分を抽出する。リング発振部2は、遅延閉ループ19において信号を遅延する遅延部として、平滑電流源6および補正電流源8の少なくとも一方の電流源から供給される電流により動作して信号を遅延する遅延部11を有する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路の消費電力を低減する。

【解決手段】内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110を制御することによって内部クロック信号LCLKの位相を調整する位相制御部120と、位相制御部120の動作モードを切り替えるモード切り替え回路130とを備える。位相制御部120は、サンプリングクロック信号SYNCLK2に同期して内部クロック信号LCLKの位相を変化させる第1の動作モードと、内部クロック信号LCLKの位相を固定させる第2の動作モードを有しており、モード切り替え回路130は、リフレッシュ信号REFBなどのトリガ信号に応答して位相制御部120を第1の動作モードに遷移させ、内部クロック信号LCLKが所望の位相に達したことに応答して位相制御部120を第2の動作モードに遷移させる。

(もっと読む)

半導体装置

【課題】搭載された異なるPLL回路の夫々の出力信号の同期化を実現する半導体装置を提供する。

【解決手段】所定の周波数の信号を入力し、当該入力信号の整数倍の周波数の信号を当該入力信号と同期させて出力する、2つの異なるPLL回路(2、4)によって同期化された信号を夫々分周し、当該分周した信号の位相差に応じた所定の遅延量に基づいて一方のPLL回路(2)の出力信号を遅延させることで、他方のPLL回路(4)の出力信号(42)に同期させたクロック信号(41)を生成する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】比較的小さな電源電圧による速度変動を高精度で抑制して比較的大きな電源電圧による速度変動を高速で抑制する。

【解決手段】半導体集積回路は、第1と第2の機能ブロックMOD00、01、クロック生成回路PLL、クロック供給回路CS0を具備する。第1と第2の機能ブロックMOD00、01には、電圧値の相違する第1と第2の電源電圧VDD00、1が供給される。MOD00は一方の電源電圧VDD01が供給可能な第1の内部回路BUF00と第1の論理回路MFF00を含み、MOD01は他方の電源電圧VDD00が供給可能な第2の内部回路BUF01と第2の論理回路MFF01を含む。クロック供給回路CS0は微調遅延段回路FC0と粗調遅延段回路CC0と位相差計測回路RSM0を含み、RSM0は第1と第2の動作クロック信号COUT00、01の位相差に応答してFC0の遅延時間TF0とCC0の遅延時間TC0を制御する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路において、カウンタ回路のスタックやロック動作の遅延を防止する。

【解決手段】位相判定信号PD0を生成する位相判定回路120と、位相判定信号PD0をサンプリングしこれに基づいて位相判定信号PD2を生成するサンプリング回路130と、位相判定信号PD2に基づいて内部クロック信号LCLKを生成するクロック生成部110とを備える。サンプリング回路130は、サンプリング周期内に位相判定信号PD0の論理レベルが変化した場合に位相判定信号PD2を固定する連続判定回路132と、位相判定信号PD1がハイレベルを示すまで位相判定信号PD2をハイレベルに固定する初期動作回路133と、位相判定信号PD1がハイレベルを示した後、連続判定回路132の動作を無効化する無効化回路134とを備える。

(もっと読む)

位相補正方法、位相補正回路、及びそれを含む信号処理装置

【課題】ローカルオシレーターから出力された信号の位相補正方法を提供する。

【解決手段】方法は、同位相出力信号の位相と直交位相出力信号の位相との比較結果に相応するデジタルコードを発生させる。方法は、同位相出力信号の位相と直交位相出力信号の位相との差を90°にするために、直交位相差動入力信号とデジタルコードとに応答して、同位相出力信号の位相を調節し、同位相差動入力信号とデジタルコードとに応答して、直交位相出力信号の位相を調節する。

(もっと読む)

遅延同期ループ回路

【課題】外部クロック信号が擾乱したとき、擬似ロックを検出し初期化したとき、電源を投入したとき、いずれの場合も確実にロックはずれを防止でき、レイアウトがコンパクトなDLL回路を提供する。

【解決手段】遅延同期ループ回路であって、入力クロックを、制御電圧の大きさに応じて遅延させて帰還クロックを出力する電圧制御遅延手段と、帰還クロックと基準クロックとを比較して位相差を検出し、該位相差に応じて、制御電圧を上昇させるための上昇信号と該制御電圧を下降させるための下降信号とを出力する位相比較器と、上昇信号と下降信号とに応じて制御電圧を決定し、電圧制御遅延手段に出力する制御電圧生成手段と、基準クロックと電圧制御遅延手段からの中間クロックとの論理和に基づき位相比較器をリセットする。

(もっと読む)

半導体装置及び位相検知回路

【課題】位相検知の誤判定を防止した高精度の位相検知回路を提供する。

【解決手段】電源線VSS1とセンスノードLSAT、LSAB間に、nMOSトランジスタの組(M1、M2、M3)、(M4、M5、M6)を備え、各トランジスタのゲートに内部クロックRCLK、RCLKのインバータINV1による反転信号、外部ロックCK、/CKをそれぞれ入力し、電源線VDD1とセンスノードLSAT、LSAB間に、pMOSトランジスタの組(MP1、MP2、MP3)、(MP4、MP5、MP6)を備え、各トランジスタのゲートにFCLKのインバータINV2による反転信号、内部クロックRCLK、外部ロックCK、/CKをそれぞれ入力し、センスノードLSAT、LSABは差動アンプAMPで増幅されラッチ回路L1でラッチされる。pMOSトランジスタ(MP11、MP12、MP13)はLSAT、LSABをプリチャージ・イコライズする。

(もっと読む)

61 - 80 / 359

[ Back to top ]