Fターム[5J106CC59]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相変換回路 (594) | 移相・遅延回路 (564) | 可変移相・遅延回路 (359)

Fターム[5J106CC59]に分類される特許

341 - 359 / 359

遅延ロック・ループ

【課題】位相検出器がDLLの出力の位相を基準入力の位相と比較する遅延ロック・ループ(DLL)について説明する。

【解決手段】位相比較器の出力は、位相比較器出力信号を経時時に積分するように機能する差動チャージ・ポンプを駆動する。チャージ・ポンプ出力は、位相比較器の出力が平均で50%の時間だけハイになるようにDLL出力の位相を調整する無限範囲を有するフェーズ・シフタを制御する。DLLが、位相検出器の出力が平均で50%の時間だけハイになるまでフェーズ・シフタを調整するので、DLL出力クロックの入力基準クロックとの関係は、使用される位相検出器のタイプにしか依存しない。さらに、DLLは、ディザ・ジッタを最小限に抑え、同時に獲得時間を最小限に抑えるように制御される。また、デューティ・サイクル補正増幅器を使用して、所望のデューティ・サイクル、たとえば50%を有するDLL出力クロックが生成される。

(もっと読む)

遅延ロックループ回路

【課題】基準クロック信号/クロック信号間の位相を合致させるように位相制御の遅延ロックループ(DLL)回路で、回路規模縮小化、低消費電力化を図かった、電圧制御可変遅延線(VCDL)を使用するアナログDLL回路を提供

【解決手段】イニシャル信号入力により第1のクロック信号の初期位相設定を行う遅延ロックループ回路で、基準クロック信号位相と第1のクロック信号位相の比較結果に応じた信号を出力の位相比較器と、イニシャル信号入力時に位相比較器出力信号に応じた選択信号を発生の初期位相差検出器と、イニシャル信号入力時に初期位相差検出器からの選択信号で位相が異なる第2のクロック信号中の基準クロック信号に最近接位相の第2のクロックを選択し、第3のクロック信号として出力の初期位相差設定回路と、第3のクロック信号に位相比較器からの信号に応じた位相遅延を付加の第1のクロック信号を出力の電圧制御可変遅延線とを備える遅延ロックループ回路を提供。

(もっと読む)

混成信号集積回路

本発明は、混成信号集積回路、すなわちアナログ回路とデジタル回路の両方を備える集積回路に関する。本発明は特に、このような装置内のノイズ低減に関する。デジタル回路がアナログ回路と同じ集積回路装置内に含まれる場合は、デジタル回路がかなりの量のノイズの追加の発生源となり得る。その結果、アナログ信号にクロストーク、電気的干渉、および信号歪みが加えられる。本発明は、アナログ回路(26)とデジタル回路(29、30)を備える集積回路であって、デジタル回路がASM(30)を含む集積回路を提供する。ASMは、クロック信号を必要としない。その動作は適切な入力条件によってトリガされるが、SSMとは異なり、その入力に変化がないときはアイドルとなり、デジタル回路によって発生されるノイズ・レベルを低減する。  (もっと読む)

(もっと読む)

遅延回路、半導体集積回路、位相調整回路、DLL回路およびPLL回路

【課題】 大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することが可能な遅延回路を得る。

【解決手段】 インバータ1〜nを複数段直列接続して形成され、各P−chトランジスタ1a〜naの基板電極に電位VDDHを供給し、各P−chトランジスタ1a〜naのソース電極にスイッチ1c〜ncが接続され、そのソース電極に供給する電位として電位VDDHまたは電位VDDLを選択可能にされ、また、電位VDDHおよび電位VDDLのうちの少なくとも一方の電位は調整自在にされたものである。

電位VDDHまたは電位VDDLの電位調整、およびスイッチ1c〜ncによる電位選択に応じて、P−chトランジスタ1a〜naに逆バイアスまたは順バイアスをかけ、大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することができる。

(もっと読む)

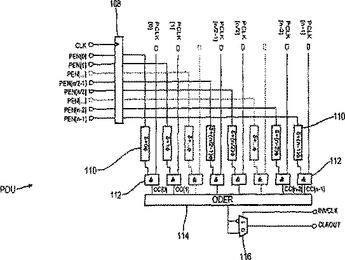

所定のクロック信号特性を有するクロック信号を生成するための方法および装置

所定のクロック信号特性を有するクロック信号(CLKOUT)を生成するための方法および装置であって、まずマスタクロック信号(CLK)に関して本質的に同一の周波数およびそれぞれ異なる位相関係を有する多数のクロック信号(PCLK[n−1:0])を準備し、次いで、準備された多数のクロック信号から(生成されるクロック信号に従って準備された制御信号(PEN[])に基づいて)所定のクロック信号を選択し、選択したクロック信号を組み合わせて所望のクロック信号(CLKOUT)を生成する。  (もっと読む)

(もっと読む)

アナログ遅延回路の同調範囲を設定する方法及び装置

アナログ遅延線、ハイブリッド遅延線及び遅延ロック・ループ(DLL)のための装置及び方法が記述される。DLLにおいて、粗位相検知器が、粗遅延線の遅延を増すか減らすかを示す粗位相調整信号を制御する際に基準信号とフィードバック信号とを比較する。同様に、微細位相検知器が基準信号とフィードバック信号とを比較してロック・バイアス信号を生成する。この信号はアナログ微細遅延線の遅延を増減する。アナログの微細遅延線及び粗遅延線は直列に接続され、粗遅延と微細遅延とからなる全遅延を有するハイブリッド遅延線を作る。更に、微細バイアス発生器はアナログ位相発生からの初期バイアス信号又はロック・バイアス信号に応答して微細遅延を制御する。  (もっと読む)

(もっと読む)

PLL回路およびDLL回路

【課題】 ロックするまでの時間を短縮することができ、初期制御電圧を、回路の用途に応じて変更することができ、製造条件等により、ロックするまでの時間が変動することを防ぐことのできるPLL回路およびDLL回路を提供する。また、ジッタを迅速に低減することのできるDLL回路を提供する。

【解決手段】 PLL回路は、位相比較器3と、チャージポンプ4と、ループフィルタ5と、電圧制御発振器6と、選択信号に応じて制御電圧のレベルを選択する電圧設定回路10と、複数個の選択信号のうち少なくとも1つを出力し、電圧制御発振器6において周波数の増減された出力クロックの、入力クロックに対する逓倍数を検出し、複数個の選択信号の中から最適な選択信号を特定し、電圧設定回路10に出力する設定値判定回路9とを含み、各回路は、待機信号に応じて処理の開始および停止を行なう。

(もっと読む)

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

クロック同期回路におけるクロック捕捉

クロック捕捉同期回路は、まず基準クロック信号から同期クロック信号を生成し、そして同期クロック信号を捕捉し、基準クロック信号が除かれた後も同期クロック信号を出力し続ける。クロック捕捉同期回路はまた、同期クロック信号の入力依存ジッタを低減する。本発明により、基準クロック信号が除かれた後、同期クロック信号を出力し続けるクロック同期回路が提供される。また、本発明により、同期クロック出力信号の入力依存ジッタをもし除去しないとしても低減はするクロック同期回路が提供される。  (もっと読む)

(もっと読む)

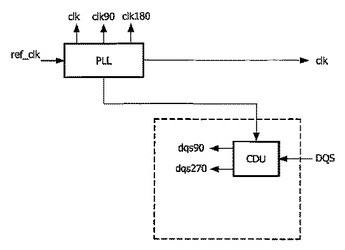

多重データレートRAMメモリコントローラ

多重データレートRAMメモリモジュールのメモリコントローラを備える。前記コントローラは、参照クロック(ref clk)から異なるクロック位相(clk、clk90、clk180)を生成するためのPLLユニット(PLL)を含む。さらに、ストローブ信号(dqs)を遅延させるための制御可能な遅延ユニット(CDU)を備える。  (もっと読む)

(もっと読む)

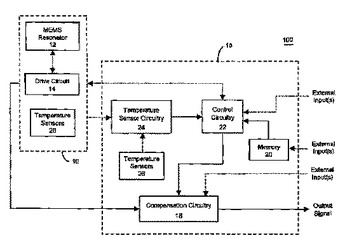

周波数および/または位相補償された微細電気機械発振器

本明細書で説明され、図示される多数の発明がある。1態様で、本発明は、出力信号を生成する微細電気機械共振器と、微細電気機械共振器の出力信号を受け取り、値のセットに応答して第2周波数を有する出力信号を生成するために微細電気機械共振器に結合された周波数調整回路構成と、を有する、補償された微細電気機械共振器を対象とする。1実施形態で、値を、微細電気機械共振器の動作温度および/または微細電気機械共振器の製造変動に依存する、微細電気機械共振器の出力信号の周波数を使用して、決定することができる。1実施形態で、周波数調整回路構成に、周波数逓倍器回路構成(たとえば、PLL、DLL、ディジタル/周波数シンセサイザ、および/またはFLLならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。周波数調整回路構成に、それに加えてまたはその代わりに、周波数分周器回路構成(たとえば、DLL、ディジタル/周波数シンセサイザ(たとえば、DDS)、および/またはFLL、ならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。  (もっと読む)

(もっと読む)

精密制御される遅延をもつ遅延ロックループ

本発明は遅延ロックループ回路(200)を開示し、その回路には遅延させられる信号のための入力手段(210)を有し、その入力手段は前記入力信号を第1と第2の分岐へとスプリットする手段を有している。第1の分岐における信号は、その信号を遅延させる部品(220)に接続され、第2の分岐における信号は、第1の分岐における遅延部品による遅延に対する遅延のない基準として用いられる。その遅延部品(220)は、受動調整可能遅延ラインであり、この回路はその調整可能遅延ラインのための調整手段(230)を有し、その調整手段は前記基準信号による影響が及び、第1の分岐には選択された位相遅延がある遅延信号を出力する出力手段を有している。その遅延部品(220)は、連続的に調整可能であることがふさわしく、例えば、調整可能な強誘電性の遅延ラインである。  (もっと読む)

(もっと読む)

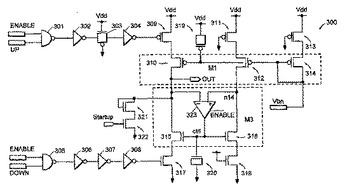

PLL/DLL用の高出力インピーダンスチャージポンプ

プルアップ回路とプルダウン回路と演算増幅器とを含む、位相ロックループ/遅延ロックループで使用するためのチャージポンプ。チャージポンプはプルアップおよびプルダウン回路の動作に関連したスタティック位相誤差を最小限にするように設計される。演算増幅器の使用はまた、低電源電圧の影響を軽減する。  (もっと読む)

(もっと読む)

可変遅延回路

本発明に係る可変遅延回路は、直列に接続され、基準クロック信号又はデータ信号を順次遅延させる複数段の第1可変遅延素子と、複数段の第1可変遅延素子に並列に接続され、基準クロック信号を遅延させる第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の位相とを比較する位相比較器と、位相比較器の比較結果に基づいて、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の所定のサイクル後の位相と略等しくすべく、複数段の第1可変遅延素子のそれぞれの遅延量を制御する遅延量制御部とを備える。 (もっと読む)

クロックリカバリ回路及び通信デバイス

本発明に係るクロックリカバリ回路は、第1遅延量でデータ信号を順次遅延させる複数段の第1可変遅延素子と、第1遅延量より大きい第2遅延量で、クロック信号を順次遅延させる複数段の第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された複数のデータ信号を、同一段の第2可変遅延素子によって遅延されたクロック信号によりサンプリングする複数のタイミングコンパレータと、連続する2つのタイミングコンパレータの2つのサンプリング結果を排他的論理和演算する複数のEOR回路と、複数のEOR回路の演算結果に基づいて、クロック信号を遅延させるリカバリ可変遅延回路とを有する。 (もっと読む)

遅延ロックループ位相混合回路

例えば遅延ロックループ(DLL)回路において、位相を微調整するための技術および回路構成を提供する。1つまたは複数の遅延素子を電流源の出力ノードと選択的に接続することにより、複数の位相信号を、単一の電流源から生成するようにすることができる。遅延素子は、電流源を切り替えることによって生成される信号のタイミングを変更するようにすることができる。  (もっと読む)

(もっと読む)

半導体装置及び電圧制御発振回路

電圧制御発振回路(15)内に互いに異なる段数の独立した複数のリング発振回路を設け、セレクタ(22)により何れか1つのリング発振回路の出力を帰還クロック信号(FB)として選択的に出力することで、独立しているリング発振回路の出力が常に帰還クロック信号として出力されるようにして、動作速度が高速であってもデューティ比が崩れていない帰還クロック信号を出力でき、入力信号(DLLI)が出力されるまでの遅延時間を任意に調整できるようにする。  (もっと読む)

(もっと読む)

位相スイッチングデュアルモジュラスプリスケーラ

デュアルモジュラス分周器を有する位相スイッチングデュアルモジュラスプリスケーラがもたらされる。前記分周器は第一及び第二の2分周回路(A;B)を有しており、前記第二の2分周回路(B)は、前記第一の2分周回路(A)の出力部に結合され、少なくとも前記第二の2分周回路(B)は各々90度で分離される四つの位相出力を有している。位相選択ユニット (PSU)が、第二の2分周回路(B)の四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の一つを選択するためにもたらされる。更に、位相制御ユニットが、制御信号(C0, NC0; C1, NC1; C2, NC2)を位相選択ユニットに供給するためにもたらされ、位相選択ユニットPSUは、制御信号(C0, NC0; C1, NC1; C2, NC2)による四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の選択を実行する。直接論理に基づく位相制御ユニット(PSU)の実現により、より高い速度が可能になり、チップ上の面積が節減される。  (もっと読む)

(もっと読む)

バイアス電流補償回路を有するタイミング発生器及び方法

カレントミラーと共に使用するための電流補償回路が開示される。カレントミラー回路は、第2カレントミラー段を駆動する第1カレントミラー段によって規定される電流経路を有し、第2カレントミラー段は、供給電圧源に結合している。電流補償回路は、供給電圧及び出力ノードに結合するインピーダンス分割器を備える。インピーダンス分割器は、供給電圧源の電圧変化を表す、ノードにおける補償信号を生成するように動作する。補償回路はさらに、出力ノードに結合する入力及び電流経路に接続される電流出力を有する利得段を含む。利得段は補償信号に応答して電流経路に印加するための補償電流を生成するように動作する。  (もっと読む)

(もっと読む)

341 - 359 / 359

[ Back to top ]