Fターム[5J106CC59]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相変換回路 (594) | 移相・遅延回路 (564) | 可変移相・遅延回路 (359)

Fターム[5J106CC59]に分類される特許

41 - 60 / 359

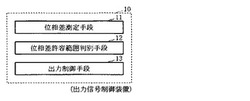

出力信号制御装置、出力信号制御方法および出力信号制御プログラム

【課題】入力信号を遅延させて出力信号を作成する際に、入力信号の変動が原因で出力信号の遅延が規定値内に納まらない場合であっても、この出力信号によるエラーの発生の抑制が可能な出力信号制御装置、方法およびプログラムを得ること。

【解決手段】位相差許容範囲判別手段12は、位相差測定手段11が測定した出力信号の位相差がこの出力信号を入力する回路で許容範囲内であるかを判別する。出力制御手段13は、許容範囲内でないと判別する状態で出力信号の出力を遮断し、許容範囲内となった段階で出力を開始する。

(もっと読む)

DLL回路

【課題】従来のDLL回路では、クロック信号の立ち上がりエッジと立ち下がりエッジとで遅延時間に差が生じる問題があった。

【解決手段】本発明のDLL回路は、入力クロック信号φinに制御電圧Vlfに応じた遅延量を与える遅延バッファBUF1〜BUF4と、入力クロック信号φinを反転させるインバータとINV1、INV2、を含み、入力クロック信号φinを遅延させた出力クロック信号φoutを生成するディレイライン10と、入力クロック信号φinと前記出力クロック信号φoutとの位相差に基づいて制御電圧Vlfを生成する制御電圧生成部とを有し、ディレイライン10は、インバータINV1と遅延バッファBUF1、BUF2とを含む第1の遅延部と、第1の遅延部の後段に設けられ、第1の遅延部と同数のインバータ及び遅延バッファ(INV2、BUF3、BUF4)を含む第2の遅延部と、を有する。

(もっと読む)

クロック発生回路

【課題】 PLLを動作させた状態で、同期外れを起させず、入力クロックの切り替えおよびそれに伴う分周比の切り替えを行うことが可能なクロック発生回路を提供する。

【解決手段】 タイミング制御部8は、入力クロックを指定するクロック選択情報が切り替わった後、分周器1がリファレンスクロックCLKREFを出力するのに応じて、クロック選択指令SELCKを切り替える動作と、分周器1に1個のリファレンスクロックCLKREFを出力させるための入力クロックの個数Rと、分周器6に1個のフィードバッククロックCLKFBを出力させるための出力クロックCLKOの個数Fのうちの少なくとも一方の設定を切り替え、切り替え後の設定個数Rに対応した入力クロックの分周器1によるカウント動作および切り替え後の設定個数Fに対応した出力クロックの分周器6によるカウント動作の両方を開始させる。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

位相制御装置

【課題】従来のこの種の装置では不可能な伝送路長の大きな変化による位相変動を調整できると同時に、検出精度を高める。

【解決手段】高周波信号である原信号を発生する原発振器1と、制御信号に基づいて原信号の通過時間を調整する移相器2と、原信号が伝送される伝送路3と、位相検出用信号を発生する位相検出用発振器4と、位相検出用信号の周波数を切り替える信号を発生する周波数切替信号発生器5と、位相検出用信号を2つに分岐して、基準信号と変調信号として出力する方向性結合器6と、方向性結合器6により分岐した変調信号が伝送される伝送路7,8と、方向性結合器6により分岐した基準信号と方向性結合器6により分岐して伝送路7,8を伝播した変調信号との位相を比較し、比較結果に応じて、原信号の通過時間を調整する制御信号を生成し移相器2に出力する位相検出器9とを備えた位相制御装置である。

(もっと読む)

時間デジタル変換回路、及びその校正方法

【課題】高分解能のTDC回路の消費電力を低減することを目的とする。

【解決手段】本発明に係るTDCは、入力信号を遅延する遅延素子11を複数直列に接続するディレイラインと、ディレイラインの最後段の遅延素子の出力の反転信号を出力する反転素子13と、基準クロック、又は反転素子の出力信号のいずれかをディレイラインの初段の遅延素子に提供するマルチプレクサ15と、を有するリング発振器10と、ディレイラインの遅延素子の接続ノード、又は初段の遅延素子の入力ノードに接続され、被測定信号の変化エッジが、遅延素子11の出力する基準クロックを遅延した信号の変化エッジに対して進んでいるか遅れているかを判定する複数の判定回路17と、判定回路17の判定結果をエンコードするエンコーダ回路31と、エンコーダ回路31の出力から、被測定信号の変化エッジの基準クロックに対する位相を算出する演算回路33と、を備える。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

位相差検出回路、定遅延時間周波数分周回路、および位相同期回路

【課題】より高い周波数において、高い精度で出力信号の位相(タイミング)変動を抑えることのできる位相差検出回路、定遅延時間周波数分周回路、および位相同期回路を得る。

【解決手段】入力信号をN分周し、パルス幅が前記入力信号の周期のB倍となる出力信号を生成し、ここで、Nは、任意の整数であり、Bは0<B<Nを満たす整数ではない実数として規定される分数パルス幅出力分周器(1)と、入力信号と出力信号の排他的論理和信号を生成する演算回路(2)と、排他的論理和信号に対して、特定のよりも低い低域周波数成分の信号を通過させ、入力信号に対する出力信号の遅延時間に相当する値を位相差検出信号として出力する低域通過フィルタ(3)とを備える。

(もっと読む)

PLL回路、DLL回路

【課題】基準クロック信号と比較対象となるクロック信号の両者の位相を比較する位相比較器から位相差信号が出力され続けるPLL回路又はDLL回路にあって、両信号の同期を適切に検出して低ジッタ動作を実現する。

【解決手段】同期判定回路(15)は、基準クロック信号(R)の位相を基準として帰還クロック信号(V)の位相が進相又は遅相であるかを検出し、両信号の位相差の期間、進相検出信号(DOWN)又は遅相検出信号(UP)を出力する進相及び遅相検出部(158)と、進相検出信号(DOWN)が出力されている期間、初期値からの計数を開始する進相期間計数部(155)と、遅相検出信号UPが出力されている期間、初期値からの計数を開始する遅相期間計数部(156)と、進相期間計数部又は遅相期間計数部の計数値が第1の規定値に到達しない回数が第2の規定値を上回ったとき、位相同期検出信号(P_DET)を出力する位相同期判定部(157)と、を備える。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

DLL回路およびそれに使用されるレプリカ回路

【課題】 レイアウト的な制限がないDLL回路を提供すること。

【解決手段】 DLL回路に使用されるレプリカ回路は、第1の電源電圧が供給され、クロックバッファへの入力クロック信号が入力され、レプリカクロック信号を出力する遅延回路を含む。遅延回路は、第1乃至第MのCMOSインバータ回路および第(M+1)乃至第NのCMOSインバータ回路が縦続接続された回路である。複数のトランジスタは、遅延回路の後段側の第(M+1)乃至第NのCMOSインバータ回路のnチャネルMOSトランジスタのソースにそれぞれ接続されている。ローパスフィルタ回路は、第1の電源電圧と異なる第2の電源電圧を低域通過濾波して、その低域濾波した電源電圧を複数のトランジスタの制御端子へ供給する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

41 - 60 / 359

[ Back to top ]