Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

261 - 280 / 296

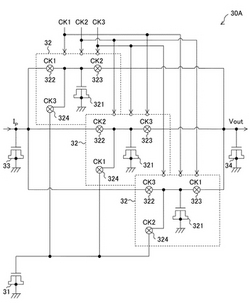

スイッチトキャパシタフィルタ及びフィードバックシステム

【課題】完全に平滑化された信号を出力するスイッチトキャパシタフィルタを実現する。

【解決手段】スイッチトキャパシタフィルタは、3個のスイッチトキャパシタ回路(32)を備えている。各スイッチトキャパシタ回路(32)は、容量(321)を有し、容量(321)が電流信号の入力端に接続された第1の状態、容量(321)が電圧信号の出力端に接続された第2の状態、及び容量(321)がフィルタ容量(31)の側に接続された第3の状態が循環する。そして、これら3個のスイッチトキャパシタ回路(32)は、互いに第1から第3の状態が重ならないようにインターリーブ制御される。

(もっと読む)

クロック・データリカバリ回路

【課題】 外部から高速な参照クロックを入力することなく、回路の安定性が高められたクロック・データリカバリ回路を提供する。

【解決手段】 入力データDataInの立ち下がりエッジと、遅延部10に配列された各1ビット遅延素子11の出力データD1,D2,D3,D4,D5の立ち上がりエッジとの位相を位相比較部20で比較し、その位相比較結果に基づいて遅延部10に配列された各半ビット遅延素子の遅延量をチャージポンプ・ループフィルタ30で調整し、調整された複数の半ビット遅延素子の出力データD0h,D1h,D2h,D3h,D4hに基づいて、入力データDataInの入力周期と同期した周期のクロックRCKをクロック生成部40で生成し、フリップフロップ50でクロックRCKを用いて入力データDataInを取り込む。

(もっと読む)

クロック・データリカバリ回路

【課題】 外部から参照クロックを入力することなく、動作の安定化が図られたクロック・データリカバリ回路を提供することを目的とする。

【解決手段】 初期状態において遅延/クロック兼用回路10に第1の位相比較回路20およびチャージポンプ・ループフィルタ30を作用させてDLL動作させ、その遅延/クロック兼用回路10に備えられた3個の半ビット遅延セル11a,11b,11cの遅延量を調整し、その後、遅延/クロック兼用回路10に第2の位相比較回路40およびチャージポンプ・ループフィルタ50を作用させて特定半ビット遅延セル11aおよびインバータ12でVCOを構成してPLL動作させ、特定半ビット遅延セル11aの遅延量を調整することによりクロックCKの位相を調整し、このクロックCKを用いて入力データDataInを取り込む。

(もっと読む)

クロック切り替え装置及びクロック切り替え方法

【課題】装置の処理を中断することなく自動的にバックアップ用のクロック分配系に切り替えることのできる、クロック切り替え装置及びクロック切り替え方法を提供する。

【解決手段】第1のクロック分配系CIN0のあるクロックパルスT0とその1周期前のクロックパルスT0’の位相を合わせる第1の検出用位相調整手段1と、クロックパルスT0とT0’の論理レベル(HIGH/LOW)が一致しているかどうかチェックし、不一致の場合ALM0をHIGHにする第1の異常検出手段2と、第2のクロック分配系CIN1のあるクロックパルスT1とその1周期前のクロックパルスT1’の位相を合わせる第2の検出用位相調整手段3と、切替信号生成手段6と、切替手段7を有する。

(もっと読む)

タイミングリカバリ回路及び間引きクロック生成方法

【課題】 本発明は、クロック信号の間引き処理にともなう特性劣化を防止したタイミングリカバリ回路及び間引きクロック生成方法を提供することを目的とする。

【解決手段】タイミングリカバリ回路は、第1のタイミング信号を出力端に出力する第1の発振回路と、第2のタイミング信号を出力端に出力する第2の発振回路と、第1のクロック信号の供給端と第1の発振回路の出力端とに結合され第1のタイミング信号に応じて第1のクロック信号のパルスを間引いた第2のクロック信号を出力端に出力する第1の間引き回路と、第1の間引き回路の出力端と第2の発振回路の出力端に結合され第2のタイミング信号に応じて第2のクロック信号のパルスを間引いた第3のクロック信号を生成する第2の間引き回路を含み、第1のタイミング信号及び第2のタイミング信号の何れか一方は固定の周期を有し他方はフィードバック制御に応じた周期を有することを特徴とする。

(もっと読む)

ディジタルPLLのロック状態判定回路

【課題】 反転間隔の長い信号及び短い信号が入力されるディジタルPLLのロック判定を確実に行うことのできるロック状態判定回路を実現することにある。

【解決手段】 PLLの入力信号を、ディジタル制御発振器25からの出力信号により標本化した離散値により入力し、ディジタル制御発振器25の発振周波数の繰返しで得られる離散値の信号レベルが、予め設定される閾値の範囲にあるか否かを電圧比較手段311により検出し、検出した電圧を電圧比較手段311により閾値の範囲外であるとして検出されるときには正の第1の数を、範囲内として検出されるときには負の第2の数をセレクタ312により割り付け、割り付けた数を累積手段321で加算累積し、累積数の大きさに応じPLL2がロック状態にあるか否かをロック判定手段323により判定するようにしてディジタルPLLのロック状態判定回路を実現した。

(もっと読む)

スリップによる分周器

【課題】ある特定回路において、起動時に2つのクロックを互いに同期させる。

【解決手段】装置は、クロック106を受け入れる分周器を備える。前記分周器104は、分周モード信号によって、N分周因子とM分周因子とを選択可能であり、ここで、(N−M)の絶対値は1である。前記装置はまた、スリップ信号112に応答するパルス発生器100を備え、分周器の出力108によって駆動され、前記分周モード信号102を前記分周器104に対して提供する。

(もっと読む)

半導体集積回路及び半導体集積回路のリセット解除方法

【課題】 本発明は、個々の製品や動作環境の違いによる発振安定待ち時間の変動に影響されることなく、信頼性を持って発振安定状態を検出することが可能な半導体集積回路を提供することを目的とする。

【解決手段】 半導体集積回路は、所定の基準電圧を出力する基準電圧回路と、発振信号供給端と基準電圧回路の出力端とに結合され発振信号の電圧と基準電圧との比較結果を出力する比較器と、比較器の出力端に結合され比較結果に応じて発振信号が基準電圧よりも大きな振幅であることを示す安定状態検出信号を出力する検出回路を含むことを特徴とする。

(もっと読む)

分周回路およびデジタルPLL回路

【課題】出力信号に生じるジッタ量を抑えることができる分周回路を提供する。

【解決手段】直列に接続されたD−FF7,9,11を、入力信号S0を基準クロック信号として駆動し、分周比決定信号S21によって選択された分周比で入力信号S0を分周して第1の分周信号S7を生成する回路モジュール3と、直列に接続されたD−FF47,49,51,53を、第1の分周信号S7を基準クロック信号として駆動し、当該直列に接続されたD−FFの段数に応じた分周比である8分周で、第1の分周信号S7を分周して出力信号S57を生成する回路モジュール45と、回路モジュール45のD−FFの出力および4/5選択信号S24に基づいて、分周比決定信号S21を生成するOR回路55とを有する。

(もっと読む)

信号間の位相、周波数、および到達時間の差分を検出するシステムおよび方法

2つの信号間(118および120)の位相、周波数、および到達時間の差分を検出するシステムおよび方法であって、遅延およびジッタを最小にし、2つの信号(118および120)が実質的に同一であったときでも安定して動作する。システムは、2つのシングルエンド型チャージポンプ(188)、位相周波数検出(PFD)回路(280)を含む。極性判定フリップフロップに供給される基準信号が、同期化される信号に対して先行しているとき第1PFDは安定している。極性判定回路に供給され同期化される信号が、基準信号に対して先行しているとき第2相補PFD回路は安定しているが、反転極性出力を有する。極性選択論理回路(284)は、選択されたPFDの極性判定もしくは非極性判定フリップフロップの活性化の間の遅延によって決定される期間において、最初に活性化されたPFDが極性を制御することを保証する。  (もっと読む)

(もっと読む)

ロック検出回路およびこれを用いたPLL回路

【課題】ロック/アンロック状態の範囲を定める許容位相誤差を周波数にかかわらず一定の割合で設定することができ、各種変動やばらつきの影響を受けることなく、ロック/アンロック状態を精度よく検出することができるようにしたロック検出回路およびこれを用いたPLL回路を提供する。

【解決手段】

電圧制御発信回路の発振出力信号FBCLK1に対して位相が前後にずれた出力信号FBCLK2,FBCLK3の位相差をロック状態の範囲として設定し、基準信号REFCLKがこの位相差の範囲内に入っていればロック状態、入っていなければアンロック状態として検出する。

(もっと読む)

2パイ・スリップ検出を用いて位相同期ループ(PLL)シンセサイザを粗調整するためのシステムおよび方法

VCOの周波数と基準周波数との間の位相差を決定し、VCOの周波数と基準周波数との位相差が2πラジアン以上の場合に誤差信号を出力する位相周波数検出器(PFD)を有する位相同期ループ(PLL)シンセサイザ(200)において、少なくとも1つの電圧制御発振器(VCO)(211)を粗調整するためのシステムに関する。続いて、PFDに生成された誤差信号の数を追従するために、監視装置(215)が用いられる。監視装置の回路が所定のレベルに到達する場合、VCOの自走周波数が粗調整され得る。本発明によって、回路の動作に影響を与える動作因子にかかわらずPLLのVCOが動作レンジに留まることが可能なようにPLLを粗調整することを可能とする、大きな利点が示される。  (もっと読む)

(もっと読む)

位相同期回路

【課題】位相同期回路のループバンド幅を最適制御する。

【解決手段】位相同期回路は、電圧制御発振器40のゲインを設定するゲイン設定回路60と、チャージポンプ回路20の電流の大きさ及びループフィルタ30の容量値から決定される時定数を設定する時定数設定回路70とを備えている。位相同期回路のループバンド幅は、ゲイン設定回路60がゲインを所定値に設定し、時定数設定回路70が時定数を所定値に設定することによって、所望値に設定される。

(もっと読む)

キャパシタンスを変化させる方法及び装置

【課題】キャパシタンスを変化させる方法及び装置を提供する。

【解決手段】制御電圧、インダクタンス及びキャパシタンスの変動による共振周波数を持つ発振信号を発生させ、発振信号を出力する複数の増幅器と、入力される信号の初期周波数帯域に対応する可変キャパシタンスを提供する複数のロードキャパシタ部と、を備えることを特徴とする発振器。これにより、低周波で電流の量を増やしてノイズ免疫性を増加させ、高周波では電流の量を減少させて実際動作周波数領域をさらに広げられる。

(もっと読む)

安定度を改善させた周波数ロック・ループ

本発明は、安定度を改善させた信号周波数の変換を可能にする周波数ロック・ループおよび関連する方法を提供する。本発明を具現化している周波数ロック・ループは、入力信号を受け取るための入力と、この入力と異なる周波数を有する出力信号を出力するための出力と、を含んでいる。周波数検出器は、1次チャンネルからの第1の係数化された入力および2次チャンネルからの第2の係数化された入力を受け取ること、第1の係数化された入力と第2の係数化された入力の差を計算すること、ならびに2つの係数化された入力の差に基づいて出力を発生させること、を行うように構成させている。電圧制御発振器は、周波数検出器から出力を受け取り、かつ出力信号を発生させるように構成させている。電圧制御発振器は、周波数検出器の出力に基づいて出力周波数を最適に設定している。従来の周波数ロック・ループと異なり、この周波数検出器では、入力因数が複雑な約分を必要とするか否かと無関係に動作するような2進レート乗算器から入力を受け取っている。すなわち、2進レート乗算器はそれぞれの入力因数の可約性に依存しないため、MおよびNが大きくかつ比較的素数性であるか否かと無関係に、その回路は補正の遅れを生じることがない。

本発明は、従来の設計と比べてより高速かつより良好に動作し、かつループ内に固有極を有さないような回路構成を提供する。さらに、本発明に従って構成した回路は、MおよびNが素数などの比較的大きな既約数であるか否かと無関係に動作する。  (もっと読む)

(もっと読む)

位相同期ループ及び遅延同期ループ

【課題】位相及び遅延同期ループとこれを備えた半導体メモリ装置を提供する。

【解決手段】この回路は、入力クロック信号と出力クロック信号との位相差を検出してアップ信号及びダウン信号を発生する位相差検出器、アップ信号に応答して供給電流を供給して制御信号のレベルを上昇させ、ダウン信号に応答して放電電流を流れるようにして制御信号のレベルを下降させ、ロック状態の後に第1制御電圧に応答して供給電流を補償し、第2制御電圧に応答して放電電流を補償して前記制御信号を出力する電荷ポンプ、ロック状態後にアップ信号とダウン信号とのレベル差に対応する第1制御電圧及び第2制御電圧を発生する補償部、及び、制御信号に応答して出力クロック信号の位相を変更する電圧制御発振器で構成されている。従って、ロック状態後に電荷ポンプの供給電流源と放電電流源との電流量の不一致を補償することによって入力クロック信号と出力クロック信号間の位相差が補償でき、これによりアップ信号とダウン信号間の位相差も補償できる。

(もっと読む)

対称構造を有する位相ロックループシステムにおける静的位相誤差補償のためのデバイス

対称型位相ロックループPLLデバイスにおいて、第1のスイッチペアI1P1、I1P2および第2のスイッチペアI2P1、I2P2が、(i)対称型時間/電圧変換ブロックの第1の出力および第2の出力と、(ii)電圧処理ブロックの第1の入力および第2の入力との間に配置される。さらに、第3のスイッチペアI3P1、I3P2および第4のスイッチペアI4P1、I4P2が、位相比較器PCの第1の入力および第2の入力の上流に配置される。制御手段が、第1のスイッチペアから第4のスイッチペアまでの開/閉を制御して、(a)第1の位相P1中、第1のクロック信号Clkrefが、比較器の第1の入力に接続され、第2のクロック信号Clkdlyが、比較器の第2の入力に接続され、変換ブロックの第1の出力が、処理ブロックの第2の入力に接続され、変換ブロックの第2の出力が、処理ブロックの第1の入力に接続され、さらに(b)第2の位相P2中、第1のクロック信号が、比較器の第2の入力に接続され、第2のクロック信号が、比較器の第1の入力に接続され、変換ブロックの第1の出力が、処理ブロックの第1の入力に接続され、変換ブロックの第2の出力が、処理ブロックの第2の入力に接続されるようにして、静的位相誤差を補償するようにする。  (もっと読む)

(もっと読む)

位相ロックループ回路

PLLはコントローラ(DRC)より成り、コントローラは線形領域検出器(LRD)から与えられる信号に基づいて、周波数変調器から与えられた周波数変調された信号(uDIV)の周波数を調整し、周波数変調された信号(uDIV)の周波数を所望の周波数に変えた後に位相検出器が線形領域に戻るようにする。位相ロックループ回路のロック時間は複雑な回路を必要とせずに改善される。  (もっと読む)

(もっと読む)

位相比較器

【課題】比較演算に係る論理回路の回路規模を削減し、その結果、その回路面積を縮小し、遅延時間を短縮し、消費電力を低減することができる位相比較器を提供する。

【解決手段】位相比較器は、データとデータのハーフレートの位相が90°ずつずれた4相の第1〜第4のクロックとの間の位相を比較するもので、データを4相の第1〜第4のクロックで各々サンプリングする第1〜第4のサンプリング回路と、第1および第2のサンプリング回路によって、その位相が隣接する2相の第1および第2のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のアップ信号を出力する第1の比較回路と、第4および第1のサンプリング回路によって、その位相が隣接する2相の第4および第1のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のダウン信号を出力する第2の比較回路とを備える。

(もっと読む)

遅延ロック・ループ内にエッジ抑制器を備える粗遅延同調回路

本発明は、遅延ロック・ループ(DLL)との使用に適したエッジ抑制器を備える粗遅延同調回路を含む遅延ロック・ループを開示する。ここで開示される同調回路は、DLL回路のロック時間を短縮する。  (もっと読む)

(もっと読む)

261 - 280 / 296

[ Back to top ]