Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

181 - 200 / 296

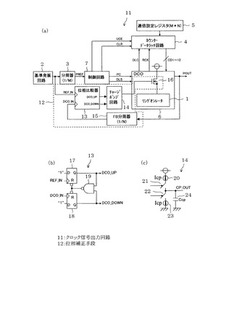

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

温度補償型水晶発振器制御用IC

【課題】端子を共用化するとともに、誤作動が起こる可能性を低減することができる温度補償型水晶発振器制御用ICを提供する。

【解決手段】温度補償型水晶発振器は、モードセレクタ回路100、制御ロジック回路シリアル・インターフェイス200、PROM回路300、発振制御回路400および発振回路500を有し、端子としては電源端子(VCC/CLK)11、入力端子(VC/DATA/PE)12、出力端子(OUT)13および接地端子(GND)14を備える。モードセレクタ回路100は、電源端子11から電源電圧にクロック信号が重畳された第1の信号が入力され、入力端子12から所定のパターンを有する第2の信号が入力された場合に、エミュレーションモードに切り替える。

(もっと読む)

電圧制御発振器を内蔵したPLL(PhaseLockedLoop)回路の位相差検出回路

【課題】低電圧動作時においても、VCO信号と基準信号との位相差を検知し、その位相差に対応したデジタル信号を生成する位相比較器を提供する。

【解決手段】基準信号と対象信号との位相差をデジタル信号として出力する位相比較器において、前記位相差に対応したパルス幅の信号により第1容量素子を充電することによって前記位相差を電荷として検出する第1検出手段と、前記基準信号の周期に対応したパルス幅の信号により第2容量素子を充電することによって基準となる時間差を基準電荷として検出する第2検出手段と、前記第1検出手段により検出された電荷と前記第2検出手段により検出された電荷とを比較する電荷比較手段と、前記電荷比較手段による比較結果により、前記第2容量素子に充電された電荷に対する前記第1容量素子に充電された電荷の比をデジタル信号として出力する出力手段と、を備える。

(もっと読む)

PLL回路

【課題】エクステンダ部の動作遅延時間を短縮して、分周比切り替え動作の誤動作に対するマージン時間を十分に確保し得るプリスケーラを提供する。

【解決手段】プリスケーラ21bは、分周比切り替え信号に基づいて、分周比を切り替えながら入力信号fvcoを分周する分周切り替え部Cと、分周切り替え部の出力信号を所定の分周比で分周するエクステンダ部Eとを備える。分周切り替え部Cは複数段のフリップフロップFF1〜FF3を有し、エクステンダ部Eの少なくとも一部を同期型カウンタで構成するとともに、少なくとも一部を非同期型カウンタで構成する。

(もっと読む)

CDR回路

【課題】再生データに含まれるジッタを簡易且つ正確にモニタ可能にする。

【解決手段】入力データDinを入力して第1再生クロックCLK1を出力する第1クロック再生部10と、前記入力データDinと前記第1再生クロックCLK1を入力して再生データDoutを出力するデータ再生部20と、前記再生データDoutを入力して第2再生クロックCLK2を出力する第2クロック再生部30と、前記第2再生クロックCLK2を入力してジッタ量を検出するジッタ検出部とを備える。ジッタ検出部は、ゲーティング回路40、積分回路50およびジッタ算出回路60からなる。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

クロックリカバリ回路

【課題】シリアル伝送されるデータにノイズが混入しても、そのノイズの影響を少なくすることができるクロックリカバリ回路を提供する。

【解決手段】基準クロックから多相クロック生成部5で生成された多位相クロックのうち、入力されたシリアルデータの変化点の中間(真中)に立ち上がりがあるクロックを選択して出力するクロックリカバリ回路1において、入力データのエッジを検出した後に、所定以下の信号幅のノイズ成分を除去するノイズキャンセル部3を設け、ノイズ成分によるクロックの切替えが起らないようにしてクロック選択部4へ出力する。

(もっと読む)

位相補間器

【課題】プロセス条件、電源電圧、温度の変動によらず、微小な位相をプログラマブルに調整できる位相補間器を提供する。

【解決手段】PLL回路のフィードバック信号(FBCLK)に非等間隔なクロックを入力し、PLL回路が本来備える位相合せ機能により、基準信号REFCLKとフィードバック信号FBCLK間に微小な位相差を与え、かつ、アップ、ダウン電流が等しいチャージポンプ(CP)回路を用いてプロセス条件、電源電圧、温度依存性が無い位相差を実現する。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

クロック再生装置

【課題】安定した高速動作が可能なクロック再生装置を提供する。

【解決手段】クロック再生装置1は、受信データD1からデータ受信用の再生クロックCK1を得るものであって、受信データD1のレベルが所定のレベルである場合に、受信データD1に同期した所定周波数の信号S1を出力する発振器21と、発振器21に直列に接続され、信号S1のレベルが所定のレベルである場合に、信号S1に同期した所定周波数の信号S1を再生クロックCK1として出力する発振器22とを備える。

(もっと読む)

位相補償クロック分周回路

【課題】分周クロックが同期信号に対して常に同一位相となるように制御し誤動作や動作遅れを防止する位相補償クロック分周回路を提供する。

【解決手段】所定周期の源クロックを動作クロックとする第1部品1と、源クロックを分周した分周クロックを動作クロックとし第1部品1と同期した処理を行う第2部品2とが混在するシステムで用いられる位相補償クロック分周回路において、源1クロックを発生し第1部品1に出力するクロック発生手段3と、源クロックを分周して生成した分周クロックを第2部品2に出力する分周手段4と、第1部品1が源クロックから生成し第2部品2に出力する同期信号を取り込み該同期信号のパルスエッジから所定の一定期間だけ遅延させた時点に位相を合わせた分周クロックを分周手段4に発生させる同期制御手段5とを備える。

(もっと読む)

電圧制御遅延装置およびDLL回路

【課題】 サンプル毎にトランジスタなどの構成素子の特性がばらついたとしても、すべてのサンプルにおいて制御電圧―遅延時間特性がばらつきの影響を受け難い電圧制御遅延装置を提供する。

【解決手段】 本発明の電圧制御遅延装置は、入力された制御電圧を電流に変換する電圧電流変換部108を含み、該電圧電流変換部108により変換された電流に比例した制御電流を出力する制御手段と、入力信号を前記制御電流に応じた時間だけ遅延させて出力する遅延手段とを備え、前記電圧電流変換部108は、所定の入力電圧範囲において線形の電圧電流変換特性を有している。

(もっと読む)

位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測のための装置。

【課題】 位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測の方法及び装置を提供する。

【解決手段】 装置は、位相誤差信号を出力するように構成された位相・周波数検出器を含む位相ロック・ループPLL回路(100)を含む。位相誤差モニター回路(102)は、位相誤差信号を論理的に結合し、論理的に結合された位相誤差信号のパルス幅を各基準クロック・サイクルにおいてプログラム可能な遅延時間と比較して瞬時位相誤差変化を決定することにより、瞬時ピーク位相誤差を決定するように構成される。記憶素子(124)は瞬時位相誤差変化をストアするように構成される。

(もっと読む)

時間デジタル変換装置およびデジタル位相同期ループ装置、受信機

【課題】広帯域の周波数範囲に対応可能で、量子化ノイズ成分を増大させることなく低消費電力化を図る。

【解決手段】時間デジタル変換器104は、発振周波数を制御する周波数制御信号16を用いて、入力周波数に応じて動作する遅延回路10−1〜10−nの段数を切り替えるスイッチング素子12−1〜12−nを備えている。入力周波数の周期に応じて必要な段数の遅延回路だけが動作することとなるため、広帯域の周波数範囲に対応しながらも系全体の低消費電力化を図ることが可能となり、特に高い入力周波数において低消費電力化を図ることができる。

(もっと読む)

クロックデューティ変更回路

【課題】PLL回路の構成に依存することなく汎用的に適用することができ、製造ばらつきによる出力クロック信号のデューティ比のずれを補償可能なクロックデューティ変更回路を提供する。

【解決手段】調整回路2は、デューティ比の目標値を指示する制御信号S[2:0]及び制御信号cntd[2:0]に基づいて決定される遅延時間だけ入力クロック信号PLLCKを遅延させた遅延信号lng及びshtを生成する遅延選択回路20及び21と、lng及びshtとPLLCKとを用いた論理演算により出力クロック信号PLLDを生成する演算回路23及び24とを有する。また、比較回路4は、PLLDのデューティ比が目標値と一致するか否かを判定する。さらに、補正回路3は、比較回路4による判定結果に応じて、PLLDのデューティ比と目標値とのずれを減少させるようlng及びshtに与えられる遅延時間の補正量を示すcntd[2:0]を生成する。

(もっと読む)

PLL回路

【課題】基準信号と分周信号の位相差によらず、両信号の位相差を精度よく検出して、その位相差に基づいて発振周波数を制御する。

【解決手段】PLL回路は、信号生成回路1と、位相検波器2と、検波フィルタ3と、周波数調整回路4と、電圧制御型発振器(VCO)5と、分周器&パルス生成回路6と、パルス幅整形回路7とを備えている。信号生成回路1は基準信号の各周期の中間点近傍で論理が変化する中間点信号を生成し、分周信号の論理変化タイミングと中間点信号の論理変化タイミングでそれぞれ論理が変化するようなパルス幅整形信号をパルス幅整形回路7にて生成して、このパルス幅整形信号に基づいてPLL検波電圧を生成するため、基準信号と分周信号が非同期であっても、基準信号と分周信号との位相差に応じたPLL検波電圧を精度よく生成できる。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、遅延時間及びデューティ比を選択可能にしたクロックを、ジッタ劣化させずに生成することができる技術を提供する。

【解決手段】DLL回路201から生成された2つのクロックを、生成クロックのライズエッジ及びフォールエッジを定めるために用いる。DLL回路201からの2つのクロックは遅延時間を選択可能とする。選択された2つのクロックを、クロック合成回路203の2入力に与える。このクロック合成回路203は位相周波数比較器と同様の回路であり、排他的論理和を用いない。この位相周波数比較器の機能により、出力クロックのライズエッジ及びフォールエッジのタイミングは、入力2クロックのライズエッジにより定まる。そのため、入力2クロックの位相(遅延時間)を任意に選択することにより、所望のデューティ比及び遅延時間を持った出力クロックが得られる。

(もっと読む)

181 - 200 / 296

[ Back to top ]