Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

101 - 120 / 296

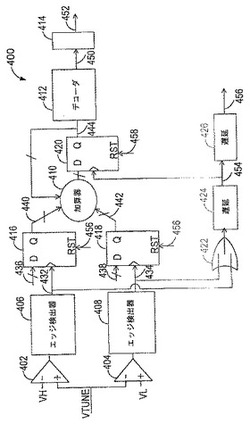

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

クロックデータリカバリ回路および逓倍クロック生成回路

【課題】データ入力の位相変化に対する受信マージンの減少を抑止でき、誤受信の確率の増大を抑止できるクロックデータリカバリ回路および逓倍クロック生成回路を提供する。

【解決手段】入力データと抽出クロックの位相差を検出して位相差に応じたアナログ量を出力する第1の位相検出器110と、ループフィルタ150と、第1の位相検出器の出力に応じてループフィルタから電流を充電または放電するチャージポンプ130,140と、VCO160と、入力データと抽出クロックの位相差の極性を検出する第2の位相検出器120と、第2の位相検出器の検出結果に応じて第1の位相検出器がもつ位相オフセットを相殺する補正位相情報を発生する補正位相情報発生部210と、補正位相をループ200に加算する補正位相加算部220と、を有し、補正位相加算部220は、チャージポンプの充電電流と放電電流を相対的に変化させる。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

改善された分解能を有する時間デジタル変換器(TDC:TIME−TO−DIGITALCONVERTER)

【解決手段】一つのインバータ遅延より小さいインバータ遅延の高分解能を含む時間デジタル変換器(TDC)が記載されている。デザイン例において、TDCは、第1及び第2の遅延パス、遅延ユニット、及び位相演算ユニットを含んでいる。第1の遅延パスは、第1の入力信号及び第1の参照信号を受信し、第1の出力を供給する。第2の遅延パスは、第2の入力信号及び第2の参照信号を受信し、第2の出力を供給する。遅延ユニットは、例えば半分のインバータ遅延によって、第1の入力信号に対して第2の入力信号を遅延する、または第1の参照信号に対して第2の参照信号を遅延する。位相演算ユニットは、第1及び第2の出力を受信し、入力信号及び参照信号間の位相差を供給する。構成は、前記第1及び第2の遅延パスについての正確なタイミングを得るために実行され得る。 (もっと読む)

位相同期回路

【課題】デジタル型の位相比較器だけで構成しつつ、不感帯の影響を排除して出力信号の位相雑音を低減する。

【解決手段】制御電圧Vcに応じた周波数の出力信号Soを出力する電圧制御発振器4と、位相比較対象信号Sdおよび基準信号Srを入力して、位相比較対象信号Sdの位相が基準信号Srの位相に対して遅れているときには両信号Sd,Srの位相差に応じたパルス幅の第1パルス信号S1を出力し、位相比較対象信号Sdの位相が基準信号Srの位相に対して進んでいるときには両信号Sd,Srの位相差に応じたパルス幅の第2パルス信号S2を出力する位相比較器2と、両パルス信号S1,S2を入力すると共に両パルス信号S1,S2の差分を積分して制御電圧Vcを出力するループフィルタ3とを備え、両パルス信号S1,S2のうちの一方のパルス信号の信号電圧を他方のパルス信号の信号電圧と異なる電圧に規定する電圧規定部6を備えている。

(もっと読む)

遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法

【課題】レイアウトの大きさを増大させず、速やかに位相を固定させることができる遅延固定ループ及び遅延固定ループにおけるクロック遅延固定方法を提供すること。

【解決手段】遅延ライン部は、第1の遅延時間d1を各々有する複数の第1の単位遅延セルを有し、クロック信号clkを遅延する第1遅延ラインと、第2の遅延時間d2を各々有する複数の第2の単位遅延セルを有し、第1遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第2遅延ラインと、第3の遅延時間d3を各々有する複数の第3の単位遅延セルを有し、第2遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第3遅延ラインとを備え、第1の遅延時間d1が第2の遅延時間d2より短く、第2の遅延時間d2が第3の遅延時間d3より短い。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

分周器

【課題】 動作周波数が高められた分周器を提供する。

【解決手段】 動作制御信号ENBが‘H’レベルに遷移し、クロック信号VCO,分周信号VCO_div2が‘L’レベル,‘H’レベルで停止した場合、3入力ナンドゲート14から出力された制御信号Aが‘L’レベルとなり、イクスクルーシブノアゲート10から出力されるトリガ信号VCO_delayが‘H’レベルとなる。トリガ信号VCO_delayはフリップフロップ11_1のトリガ端子Tに入力されており、フリップフロップ11_1から出力されている分周信号VCO_div2を‘H’レベルから‘L’レベルに遷移して、フリップフロップ11_1をリセット状態にする。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラを提供する。

【解決手段】PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL300)とを備えている。このPLL300は、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器312と、前記発振器312に結合され、前記基準信号341を受信し、且つ前記基準信号341と、フィードバック信号342との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD302)と、前記PFD302に結合され、周期的にPFD302が誤り訂正信号を生成することができるようにする抑制回路321とを備えている。

(もっと読む)

クロックデータリカバリ回路

【課題】簡単な回路で高データレートおよび低データレートに対応させる。

【解決手段】クロック信号CLK0、CLK1のエッジに係るタイミングt1、t2、t3(ただし、t2<t1<t3)でサンプリングした入力データ信号DATAINの論理値をそれぞれD1、D2、D3とする時、D1≠D2であるか、D1≠D3であるかを検出する検出回路11と、検出回路11の検出結果に基づいて、入力データ信号DATAINの論理値の遷移タイミングがタイミングt2、t3に一致するようにクロック信号CLK0、CLK1の位相を変化させるクロック発生回路14と、を備える。

(もっと読む)

クロック再生回路及びクロック再生方法

【課題】回路規模を大きくすることなく、広い範囲のクロック周波数を再生することが可能なクロック再生回路を提供する。

【解決手段】クロック信号を生成するクロック信号生成回路11と、入力データ信号とクロック信号との位相比較出力信号を出力する第1及び第2の位相比較器13,14と、位相比較出力信号に基づいて入力データ信号とクロック信号との周波数差信号を出力する周波数比較器15とを備える。クロック信号生成回路11は奇数個の論理反転回路を直列につないで位相の異なる2種のクロック信号を出力し、それぞれを別々の位相比較器13,14に入力して位相を比較して位相比較出力信号を出力し、周波数比較器15は第1及び第2の位相比較器13,14における各位相比較出力信に基づいて周波数を比較する。

(もっと読む)

位相同期回路、および通信装置

【課題】設定される動作モードに基づいて処理信号の処理クロック周波数を動作モードに基づいて切り替え、消費電力の低減を図ることが可能な位相同期回路、および通信装置を提供する。

【解決手段】デジタル値で表される発振制御信号に基づく発振周波数の発振信号を出力する発振回路と、搬送波周波数が基準周波数で除算された分周比と動作モードを規定する制御信号とが入力され、分周比を制御信号に基づいて設定された整数値で除算する第1ビットシフト部と、発振信号に基づく信号と制御信号とが入力され制御信号に基づいて設定された整数値により発振信号に基づく信号を分周する第1分周部と、基準周波数信号の各周期において第1累積加算値と第2累積加算値および累積位相の小数部とを比較し位相比較信号を出力する位相比較部と、位相比較信号を制御信号に基づく任意の収束値に収束させ発振制御信号を出力するデータ変換部とを備える位相同期回路が提供される。

(もっと読む)

適応的遅延調整を有する位相補間器

【課題】参照信号と補間信号間の位相関係を確実に保持し、より小さく、より簡単な構成の装置を実現するために応用可能な位相補間器を提供する。

【解決手段】位相補間器は、2つの可調整遅延器30及び31、可調整遅延器30で遅延された信号と可調整遅延器31で遅延された信号との位相差を検出する位相比較器32、位相比較器32の出力を積分する積分器33、可調整遅延器30及び31の制御電圧を設定する乗算器34−1、34−2を備える。位相比較器32と積分器33を備えるフィードバックループは、可調整遅延器30の遅延量を制御し、{ACK1、ACK2}及びICK間の位相関係を確実に保持し、安定なICK位相を実現する。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にし、同期クロックのずれを小さくしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力し、データ入力信号に特定期間変化がない場合に擬似信号を供給する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号の入力端子とVCXO109の入力端子との接続を、異常信号によりオンにするスイッチ104とを有するタイミングリカバリー回路である。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

101 - 120 / 296

[ Back to top ]