Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

281 - 296 / 296

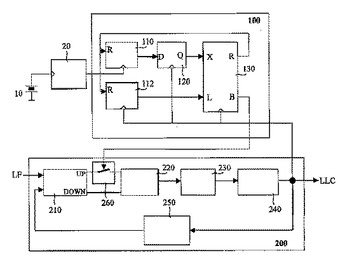

時間サイクルサプレッサを用いた低ロック時間遅延ロックループ

本発明は、クロック発生器を含む同期集積回路と共に使用するのに適した時間サイクルサプレッサ回路を有する遅延ロックループ(DLL)構造を開示している。ここに開示された時間サイクルサプレッサ回路を有する改良された遅延ロックループ構造を使用すると、同期回路のロック時間を減らすことができる。  (もっと読む)

(もっと読む)

非平衡型4相相関器を用いたPLL

4相相関器(2)を含む周波数検出器(10)を具備し、データおよびクロック再生で使用される位相ロックループ(1)であり、周波数検出器を構成する4相相関器(2)は、入力信号(D)と同じビットレートを有する信号によって制御される第1のマルチプレクサ(31)および第2のマルチプレクサ(32)に接続されたダブルエッジクロック式双安定回路(21,22,23,24)と、第1のマルチプレクサ(31)により供給される第1の信号ペア

【数1】

および第2のマルチプレクサ(32)により供給される第2の信号ペア

【数2】

によって制御される位相検出器(DFF)と、を含む。  (もっと読む)

(もっと読む)

平衡型4相相関器を備えたPLL

平衡型4相相関器(2)を含む周波数検出器(10)を具備する位相ロックループ(1)であり、ループ(1)は4相相関器(2)が入力信号(D)と同じビットレートを有する信号によって制御されるマルチプレクサ(31,32,33,34)に接続されたダブルエッジクロック式双安定回路(21,22,23,24,25,26,27,28)を具備することを特徴とする。  (もっと読む)

(もっと読む)

位相検出回路及び方法と、これを用いたクロックデータ復元回路及び方法

【課題】単位動作時間より長い幅を有するエラー信号と基準信号とを生成することでより高速動作が可能な位相検出器を提供する。

【解決手段】本発明のクロックデータ復元回路は電圧制御発振器、クオータレート線形位相検出器、電荷ポンプ及びフィルタを具備する。また、クオータレート線形位相検出器は第1貯蔵部と、第2貯蔵部と、エラー信号検出部と、基準信号検出部と第1スイッチング部と、第2スイッチング部とを含む。

(もっと読む)

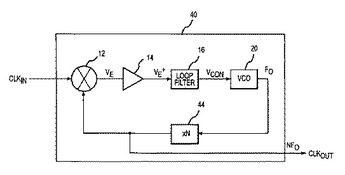

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

低ジッタのスイッチドキャパシタ周波数シンセサイザのための制御信号の生成

位相検出器および制御信号のジェネレータ(140)は、遅延されていないアップ信号(620)および遅延されていないダウン信号(625)を生成するために、基準信号(基準クロック)およびフィードバック信号(フィードバック信号)に応答する。プログラム可能な遅延ユニット(630,635)は、チャージポンプにアップ信号およびダウン信号を与えるために、遅延されていないアップ信号および遅延されていないダウン信号を遅延させる。アップ信号およびダウン信号に応答するよう構成される分周器(655)は、分周されたクロック信号(660)を与える。ノンオーバーラップクロック生成器は、スイッチドキャパシタリップル平滑フィルタのためにノンオーバーラップ保持偶数およびノンオーバーラップ保持奇数信号(hold_e,hold_o)を与えるために、分周されたクロック信号に応答するよう構成される。  (もっと読む)

(もっと読む)

クロック発生器及びその方法

複数の出力クロック信号を生成するクロック発生器において、PLLからクロック発生器へジッタ入力クロックが提供される場合、クロック発生器を入力基準クロックと同期させる装置及び方法が提供される。クロック発生器及びPLLは、それぞれ、同一の比を有する分周器を有する。前記装置は、同期装置(205)及び状態機械(210)を有する。同期装置は、入力基準クロック及びジッタ入力クロックを受信し、そしてそれらからジッタ入力クロックに対し同期入力クロック信号を生成する。状態機械は、同期入力クロック信号及びジッタ入力クロックを受信し、ジッタ入力クロックを用い同期入力クロック信号と同期し、そしてジッタ入力クロックが所定の最大数のクロック幅までのジッタを有する場合、再同期動作を自制する。  (もっと読む)

(もっと読む)

スイッチトキャパシタフィルタ及びフィードバックシステム

ループフィルタ(30)は、電流信号の入力端と基準電圧との間に設けられた第1の容量素子(31)と、上記入力端と第1の容量素子(31)との間に設けられたスイッチトキャパシタ回路(32)と、第1の容量素子(31)及び前記スイッチトキャパシタ回路(32)に並列に設けられた第2の容量素子(33)とを備えている。スイッチトキャパシタ回路(32)において、第3の容量素子(321)が第1の容量素子(31)側に接続されるとき、第4の容量素子(322)は第2の容量素子(33)側に接続される。上記構成のループフィルタ(30)において、第2の容量素子(33)の容量値を、第3及び第4の容量素子(321,322)の容量値よりも大きく設定する。 (もっと読む)

モノリシックなクロック・ジェネレータおよびタイミング/周波数リファレンス

電力節約モード、クロック・モード、リファレンス・モード、およびパルス化モードなどの複数の動作モードと共に、クロック・ジェネレータおよび/またはタイミングおよび周波数のリファレンスを提供する。共振周波数を有する第1の信号を供給するようになっている共振器と、増幅器と、温度に応じてこの共振周波数を修正するようになっている温度補償器と、製造プロセス変動に応じてこの共振周波数を修正するようになっているプロセス変動補償器とを含んでいる。さらに、実質的にこの共振周波数以下の対応する複数の周波数を有する複数の第2の信号に、この共振周波数を有する第1の信号を分周するようになっている周波数分割器と、これらの複数の第2の信号から1つの出力信号を供給するようになっている周波数セレクタとを含むことができる。  (もっと読む)

(もっと読む)

LC発振器を備えたPLLの粗チューニング時間の改良

LC発振器のチューニング方法と装置が開示されている。本発明の実施形態は、ビット比較時間を適応的に制御し、最少の粗チューニング時間が得られるようにすることを含んでいる。ビット比較時間は、LC発振器のキャパシタアレイ内の対応する加重キャパシタの冗長量に逆比例してスケーリングされる。 (もっと読む)

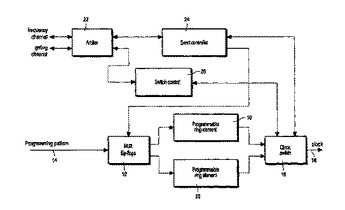

プログラマブルで一時停止可能なクロック発生ユニット

互いに排他的に動作するように配置構成された2つのプログラマブル・リング発振器(10、20)と、プログラマブル可変遅延要素(図示せず)とを含むクロック発生回路。入力プログラミング・パターン(14)が発振回路に入力として供給され、プログラミング・パターン(14)は、クロック信号を発生させる必要のある周波数のシーケンスを表すデータを提供する。2つの発振器(10、20)の出力端がクロック・スイッチ(16)に接続され、発生されたクロック信号(18)がこのスイッチから出力される。周波数変更を求める要求が受け取られたときは、まず現在アイドル状態の発振器(20)が必要とされる次の周波数で活性化され、次いで現在動作中の発振器(10)の出力が、そのクロック信号がローのときに、ゲート制御されるようになる。次に、前にゲート制御されていた発振器(20)の出力が、その出力がローのときに、ゲート制御されないようにされ、次いで発振器(10)が非活性化される。  (もっと読む)

(もっと読む)

PLL回路

本発明は、位相又は周波数検出回路(210)の出力信号に応じて制御される発振回路(240)を有する位相同期ループ装置に関し、切替制御手段(130)は、所定の閾値周波数が供給される第1のタイマ手段(110)及び発振回路(240)の出力周波数が供給される第2のタイマ手段(112)の出力に応答して遮断信号を発生するように設けられる。遮断信号に基づいて、遮断手段(260)は、発振回路(240)への出力信号の供給を抑制する。これにより、PLL装置の出力周波数は、周波数閾値を超えて変化することが回避可能となるとともに、唯1つのPLL回路だけで済むことになる。

(もっと読む)

(もっと読む)

位相スイッチングデュアルモジュラスプリスケーラ

デュアルモジュラス分周器を有する位相スイッチングデュアルモジュラスプリスケーラがもたらされる。前記分周器は第一及び第二の2分周回路(A;B)を有しており、前記第二の2分周回路(B)は、前記第一の2分周回路(A)の出力部に結合され、少なくとも前記第二の2分周回路(B)は各々90度で分離される四つの位相出力を有している。位相選択ユニット (PSU)が、第二の2分周回路(B)の四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の一つを選択するためにもたらされる。更に、位相制御ユニットが、制御信号(C0, NC0; C1, NC1; C2, NC2)を位相選択ユニットに供給するためにもたらされ、位相選択ユニットPSUは、制御信号(C0, NC0; C1, NC1; C2, NC2)による四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の選択を実行する。直接論理に基づく位相制御ユニット(PSU)の実現により、より高い速度が可能になり、チップ上の面積が節減される。  (もっと読む)

(もっと読む)

遅延ロックループのための起動回路

遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。  (もっと読む)

(もっと読む)

位相同期回路、および、それを用いたシンセサイザ、通信装置

【課題】位相同期回路における入力クロックの同期に必要なエッジのみを検出し、異常入力クロック入力時や電源投入時でも、同期時間が短く、また、安定した出力クロックを供給できる位相同期回路を提供すること。

【解決手段】位相同期回路において出力クロックを分周する出力分周カウンタの出力値から、エッジ検出パルスを生成し、入力クロックの位相同期に必要なエッジのみを検出した入力分周クロックと出力分周クロックを位相比較器に入力することを特徴とする。

(もっと読む)

位相周波数検出器およびそれが組み込まれた位相ロックループ回路

【課題】 位相誤差信号に周波数差を加味した変形を加えることにより、周波数が離れているときでも短時間で位相同期を達成する。

【解決手段】 周波数が離れているときに生じる位相誤差信号の不連続なジャンプをジャンプ検出部30において検出し、検出信号により状態記憶部32の状態を遷移させる。保持部34において、状態記憶部32の状態に応じて位相誤差信号を修正して周波数位相誤差信号とする。

(もっと読む)

281 - 296 / 296

[ Back to top ]