Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

201 - 220 / 225

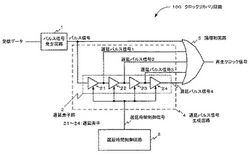

クロックリカバリ回路

【課題】 回路構成が簡単で、かつデータの伝送速度が高くてもデータ受信後直ちにクロックを再生することのできるクロックリカバリ回路を提供する。

【解決手段】 クロックリカバリ回路100は、受信データの遷移を検出してパルス信号を発生するパルス信号発生回路1と、受信データの最大無遷移期間数より1つ少ない数に相当する複数の遅延素子を直列に接続した遅延素子群2と、予め設定されている受信データの伝送速度に基づいて遅延素子群2のそれぞれの遅延素子の遅延時間が受信データの1データ期間分となるように遅延時間制御信号により制御する遅延時間制御回路3と、遅延素子群2にパルス信号を入力して受信データの1データ期間分ずつ順次遅延させた複数の遅延パルス信号を出力する遅延パルス信号生成回路4と、パルス信号および複数の遅延パルス信号の論理和をとって再生クロック信号として出力する論理和回路5とを有する。

(もっと読む)

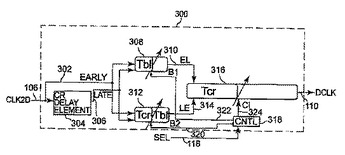

ライブ測定により基準が初期化される遅延ロックループ

【解決手段】遅延ロックループを動作する方法は、第1ロックポイントに応答して第1出力信号を生成することを含む。第1出力信号を生成し続けている間に、新しいロックポイントが測定、さもなければ決定される。その後、第2出力信号が、新しいロックポイントに応答して生成される。遅延ロックループが第1出力信号の生成を続けている間、新しいロックポイントが、遅延ロックループにロードされてよい。例えば(とりわけ)、オートリフレッシュコマンド、プリチャージオールコマンド、モードレジスタロードコマンド、パワーダウンエントリ、パワーダウンエクジットに応答し、タイマ、例えば(とりわけ)内部タイマに応答し、又は、環境状態信号、例えば(とりわけ)温度センサ出力信号に応答して、遅延ロックループは、第1ロックポイントに応じた第1出力信号の生成から、新しいロックポイントに応じた第2出力信号の生成に切り替わる。開示された方法を用いた回路及びシステム。要約書に適用される規則から、この要約書は、特許請求の範囲を解釈するのに用いられるべきではない。 (もっと読む)

タイミング発生回路

【課題】基準クロックを変更しても、高精度のタイミングクロックを即座に生成可能なタイミング発生回路を提供する。

【解決手段】遅延装置20に含まれる遅延回路21の入出力間に接続される遅延素子の数を変更可能にしておき、基準クロックck2の切り替えを指示する信号freqに応じてこの数を変更することで、遅延装置20全体の遅延時間を瞬時に変更する。

(もっと読む)

タイミングリカバリ回路及び間引きクロック生成方法

【課題】 本発明は、クロック信号の間引き処理にともなう特性劣化を防止したタイミングリカバリ回路及び間引きクロック生成方法を提供することを目的とする。

【解決手段】タイミングリカバリ回路は、第1のタイミング信号を出力端に出力する第1の発振回路と、第2のタイミング信号を出力端に出力する第2の発振回路と、第1のクロック信号の供給端と第1の発振回路の出力端とに結合され第1のタイミング信号に応じて第1のクロック信号のパルスを間引いた第2のクロック信号を出力端に出力する第1の間引き回路と、第1の間引き回路の出力端と第2の発振回路の出力端に結合され第2のタイミング信号に応じて第2のクロック信号のパルスを間引いた第3のクロック信号を生成する第2の間引き回路を含み、第1のタイミング信号及び第2のタイミング信号の何れか一方は固定の周期を有し他方はフィードバック制御に応じた周期を有することを特徴とする。

(もっと読む)

遅延ロックループを初期化する方法および装置

遅延ロックループは、遅延対制御電圧特性のどちらの端にも近くない動作点にDLLが初期化されることを保証する初期化回路を含む。初期化回路は、DLLをして最初にある初期遅延から出発してロック点を探索するよう強制し、遅延が一方向に変えられ、DLLをして第一のロック点をスキップするよう強制する。初期化回路は、動作点に到達するまで、DLLが電圧制御遅延ループの遅延を変えるのを初期遅延から一方向にのみ許容する。

(もっと読む)

(もっと読む)

PLL装置及び映像同期制御装置

【課題】 基準信号に同期した信号を高速かつ安定的に発生する。

【解決手段】 位相差カウント部15aは、基準信号f1と分周信号f2との位相差をカウントし、位相差カウント値Cを生成する。しきい値判定部15bは、位相差カウント値Cとしきい値を比較して、位相差カウント値Cがしきい値を超えたか否かを示す位相差判定信号D2を生成する。位相シフト処理部16は、位相差判定信号D2により、位相差カウント値Cがしきい値を超えた状態であるしきい値範囲外を認識した場合は、位相差カウント値Cにもとづいて、位相差がゼロになるように分周信号f2の位相を強制シフトする位相シフト処理を行って、位相差がゼロの状態からPLLフィードバック制御を開始させる。

(もっと読む)

タイミング発生回路

【課題】 微小遅延部で発生させる遅延量を精密に制御することができるタイミング発生回路を得る。

【解決手段】 直列接続した粗遅延部及び微小遅延部と、粗遅延部に電源電圧を供給する第1のDLLと、微小遅延部に電源電圧を供給する第2のDLLとを設ける。そして、第1のDLL内のモニタ回路として用いる遅延部を粗遅延部と同じ回路形式とする。また、第2のDLL内のモニタ回路として用いる遅延部を微小遅延部と同じ回路形式とする。

(もっと読む)

遅延安定化回路および半導体集積回路

【課題】遅延または周波数の安定度低下やコスト増加を抑えることができ、設計時間も短縮することが可能な遅延安定化回路および半導体集積回路を提供する。

【解決手段】キャパシタと抵抗からなるパッシブなノイズフィルタ13と、ノイズフィル13を経由して電源の電力が供給される論理ゲートを含む可変遅延回路111を含むリングオシレータ13と、外部から入力されたクロックを基準に用いて可変遅延回路111の遅延変動を抑えるための遅延制御信号DCTLを可変遅延回路111に出力するフィードバック制御回路12と、を有し、リングオシレータ13によりクロックCLKを出力する。

(もっと読む)

ロッキング速度が向上した内部クロック発生回路とこれに含まれるアナログシンクロナスミラーディレイ

【課題】外部クロック信号に対する内部クロック信号のロッキング所要時間を短縮させる内部クロック発生回路と、動作領域の幅が広くて、クロック信号の周波数変化に対処可能なアナログシンクロナスミラーディレイを提供する。

【解決手段】内部クロック発生回路は、第1遅延ミラー、巨視ロッキングブロック、電圧制御遅延ブロック、第2遅延ミラー、および微細ロッキングブロックを含む。第1遅延ミラーは、所定のバッファリングクロック信号を所定の第1ミラーリング遅延時間だけ遅延して遅延クロック信号として提供するために駆動し、第1ミラーリング遅延時間は、所定の第1〜第3遅延時間の和と同一であり、バッファリングクロック信号は、外部クロック信号に対して第1送信遅延時間で同期し、巨視ロッキングブロックは、前記バッファリングクロック信号と遅延クロック信号を用いて、所定のアナログ同期クロック信号を提供する。

(もっと読む)

ブレンダー遅延を2つ用いた可変遅延線

可変遅延線は、第1の信号を供給するように構成された第1のブレンダー遅延と、この第1の信号に相補的な第2の信号を供給するように構成された第2のブレンダー遅延と、偶数番号の粗遅延素子が選択された場合には上記第1の信号を遅延し、奇数番号の粗遅延素子が選択された場合には上記第2の信号を遅延するように構成された粗遅延とを有する。  (もっと読む)

(もっと読む)

補間遅延のための回路及び方法

補間遅延のための回路(100)及び方法を提供する。本回路には、補間遅延(120)を備えた遅延同期ループ(110)が含まれる。遅延同期ループには、差動インバータ(241)、補間回路(220)、及び差動比較回路(230、250)が含まれる。差動インバータは、差動クロック信号(140)を受信するように接続され、また、反転差動クロック信号を供給するように接続される。補間回路は、クロック信号及び反転クロック信号双方を受信するように、また、クロック信号に対して第1遅延を有する補間クロック信号を供給するように接続される。差動比較回路は、反転クロック信号を受信するように接続され、また、クロック信号に対して第2遅延を有する非補間クロック信号を供給するように接続される。第2遅延は、差動インバータの全遅延に相当し、第1遅延は、全遅延の所定の一部に相当する。  (もっと読む)

(もっと読む)

半導体装置

【課題】電源電圧の異なる複数の論理回路間において、クロック信号のスキューが大きくなっていた。

【解決手段】第1の論理回路部12は電源電圧が制御される。第2の論理回路部13は外部クロック信号に応じて動作する。調整回路17は外部クロック信号が供給される第1の遅延回路と、第1の論理回路部12から出力される第1のクロック信号と第2の論理回路部から出力される第2のクロック信号とのタイミングのずれ量を検出する検出回路を有し、前記検出回路の検出結果に応じて第1の遅延回路の遅延時間を調整し、第1の遅延回路の出力信号を第3のクロック信号として第1の論理回路部に供給する。

(もっと読む)

位相比較器、PLL回路、FLL回路、ビット同期回路、受信装置

【課題】 伝送信号のS/N比が低い場合であっても正確にビット判定を行うことができて、ビット誤りを低減可能な位相比較器、PLL回路、FLL回路、ビット同期回路、受信装置を提供する。

【解決手段】 位相比較器9は、積分器1〜3と、積分器1の出力と積分器2の出力との差を出力する加算器4と、積分器1の出力と積分器2の出力との和を出力する加算器5と、加算器4の出力の極性から各ビットを判定し、ビット判定結果を復調データSdとして出力するビット判定器6と、加算器5の出力の1/2(半値)と積分器3の出力との差を出力する加算器7と、加算器7の出力にビット判定器6の出力を乗じて位相誤差信号Spとして出力する乗算器8とから構成される。積分器1〜3は、前半積分区間信号Sa、後半積分区間信号Sb、中間積分区間信号ScがHレベルのときのみ積分動作を各々行う。

(もっと読む)

DLL回路

【課題】 位相が誤ってロックされるという誤ロック状態の防止が図られたDLL回路を提供する。

【解決手段】 フリップフロップ17_1,17_2,イクスクルーシブノア回路17_3からなるコースサーチ回路17で、リファレンスクロックCLKINとフィードバッククロックCLKFBとを比較しておおまかなロックポイントを求め、次いで、フリップフロップ18_1,18_2,18_5,切替回路18_3,遅延回路18_4からなるファインサーチ回路18で、リファレンスクロックCLKINの立ち上りと、二分周フィードバッククロックCLKFB2の立ち上りおよび立ち下り双方との位相を比較することによって、リファレンスクロックCLKINとフィードバッククロックCLKFBとの間の位相が所定の位相となるように可変遅延セル16の遅延量を制御回路19で制御する。

(もっと読む)

ギガヘルツ周波数に効率的な遅延同期ループを有する多重位相クロック発生器を備える光学駆動回路

【課題】800MHzまたはそれ以上の周波数を有する入力クロックから、32個の異なる位相を発生させうる遅延同期ループ基盤の多重位相クロック発生器回路を備える光学(ディスク)駆動システムを提供する。

【解決手段】Nで分周されたクロックを、フィードバックループ内のM個の電圧制御される第1遅延素子に出力するための周波数分周器を有する遅延同期ループを備え、分周されていないクロックを遅延させて、M個の多重位相クロックを出力するために、フィードバックループの外部に同じM個の電圧制御される遅延素子を更に備える多重位相クロック発生器。光学駆動システムの光学駆動回路と、光学ディスク上の隣接する溝に書き込まれるマークの重複を防止するための書き込みストラテジを行う方法とを提供し、該回路及び方法は、GHzの周波数範囲で高解像度(例えば、T/32)でスイッチングする多重の書き込みストラテジ波形(チャンネル)を生成する。

(もっと読む)

クォターレートクロック復元回路、及びクロック復元方法

【課題】 受信データレートの4分の1の周波数を有するクロックとして動作しかつ、四つの位相補間器を用いるクロックデータ復元回路を提供する。

【解決手段】 受信データレートの4分の1の周波数で0°、90°、180°および270°の位相差を有する第1クロック乃至第4クロックを生成するクロック生成部360と、制御信号に基づいて前記第1クロック乃至第4クロックを位相補間して受信データレートの4分の1の周波数で受信データの位相を追従する0°、45°、90°および135°の位相差を有する第5クロック乃至第8クロックを生成する位相補間部350と、受信データと前記第5クロック乃至第8クロックとの位相差に対応する信号を出力する位相検出部310と、位相検出部の出力信号を受信して位相補間部を制御するための制御信号を生成する位相補間部制御回路320とを含む。

(もっと読む)

アナログ遅延回路の同調範囲を設定する方法及び装置

アナログ遅延線、ハイブリッド遅延線及び遅延ロック・ループ(DLL)のための装置及び方法が記述される。DLLにおいて、粗位相検知器が、粗遅延線の遅延を増すか減らすかを示す粗位相調整信号を制御する際に基準信号とフィードバック信号とを比較する。同様に、微細位相検知器が基準信号とフィードバック信号とを比較してロック・バイアス信号を生成する。この信号はアナログ微細遅延線の遅延を増減する。アナログの微細遅延線及び粗遅延線は直列に接続され、粗遅延と微細遅延とからなる全遅延を有するハイブリッド遅延線を作る。更に、微細バイアス発生器はアナログ位相発生からの初期バイアス信号又はロック・バイアス信号に応答して微細遅延を制御する。  (もっと読む)

(もっと読む)

遅延回路、半導体集積回路、位相調整回路、DLL回路およびPLL回路

【課題】 大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することが可能な遅延回路を得る。

【解決手段】 インバータ1〜nを複数段直列接続して形成され、各P−chトランジスタ1a〜naの基板電極に電位VDDHを供給し、各P−chトランジスタ1a〜naのソース電極にスイッチ1c〜ncが接続され、そのソース電極に供給する電位として電位VDDHまたは電位VDDLを選択可能にされ、また、電位VDDHおよび電位VDDLのうちの少なくとも一方の電位は調整自在にされたものである。

電位VDDHまたは電位VDDLの電位調整、およびスイッチ1c〜ncによる電位選択に応じて、P−chトランジスタ1a〜naに逆バイアスまたは順バイアスをかけ、大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することができる。

(もっと読む)

クロック同期回路におけるクロック捕捉

クロック捕捉同期回路は、まず基準クロック信号から同期クロック信号を生成し、そして同期クロック信号を捕捉し、基準クロック信号が除かれた後も同期クロック信号を出力し続ける。クロック捕捉同期回路はまた、同期クロック信号の入力依存ジッタを低減する。本発明により、基準クロック信号が除かれた後、同期クロック信号を出力し続けるクロック同期回路が提供される。また、本発明により、同期クロック出力信号の入力依存ジッタをもし除去しないとしても低減はするクロック同期回路が提供される。  (もっと読む)

(もっと読む)

精密制御される遅延をもつ遅延ロックループ

本発明は遅延ロックループ回路(200)を開示し、その回路には遅延させられる信号のための入力手段(210)を有し、その入力手段は前記入力信号を第1と第2の分岐へとスプリットする手段を有している。第1の分岐における信号は、その信号を遅延させる部品(220)に接続され、第2の分岐における信号は、第1の分岐における遅延部品による遅延に対する遅延のない基準として用いられる。その遅延部品(220)は、受動調整可能遅延ラインであり、この回路はその調整可能遅延ラインのための調整手段(230)を有し、その調整手段は前記基準信号による影響が及び、第1の分岐には選択された位相遅延がある遅延信号を出力する出力手段を有している。その遅延部品(220)は、連続的に調整可能であることがふさわしく、例えば、調整可能な強誘電性の遅延ラインである。  (もっと読む)

(もっと読む)

201 - 220 / 225

[ Back to top ]