Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

161 - 180 / 225

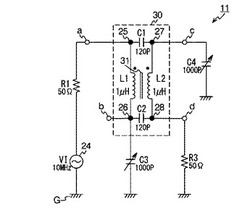

位相変調器及びルビジウム原子発振器

【課題】クワッドレチャ・ハイブリッドを使用して、進相端子と遅相端子に可変リアクタ

ンス素子を接続することにより、所望する位相に変調すると共に、出力レベルの変動を最

小限に抑えた位相変調器を提供する。

【解決手段】この位相変調器11は、発振信号VIを発振する発振源24と、発振源24

から発振された発振信号VIを入力する入力端子aと、発振信号VIの位相に対して位相

が進む進相端子cと、発振信号VIの位相に対して位相が遅れる遅相端子bと、進相端子

cに現れる位相と遅相端子bに現れる位相とを合成して出力する出力端子dと、を有する

クワッドレチャ・ハイブリッド30と、可変容量素子C3と、可変容量素子C4と、出力

端子dと、を備えて構成されている。

(もっと読む)

遅延同期ループ及びこれを備えた半導体メモリ装置

【課題】遅延同期ループ及びこれを備える半導体メモリ装置を公開する。

【解決手段】入力クロック信号と偶数個の遅延クロック信号のうちの1つの遅延クロック信号との位相を比較して第1アップ信号及び第1ダウン信号を発生し、入力クロック信号の上昇エッジと下降エッジのうちの1つのエッジを検出してパルス信号を発生し、第1アップ信号及び第1ダウン信号に応答して第1制御信号を変更する第1制御部、及びリング状に従属連結された偶数個の遅延セルを備え、第1制御信号に応答して偶数個の遅延セルの遅延時間が変更されて入力クロック信号の周期と同一の周期を有する偶数個の遅延クロック信号を発生し、偶数個の第1選択信号のうちの活性化された1つの第1選択信号に応答して偶数個の遅延クロック信号のうちの少なくとも1つの遅延クロック信号の遷移が制御され、残りの遅延クロック信号の遷移が少なくとも1つの遅延クロック信号の遷移に応答して遷移する遅延器を備えた周期同期部で構成されている。

(もっと読む)

主にデジタルな時間基準発生器を使用する信号完全性測定のシステム及び方法

1以上の被テスト信号のサンプリングを制御するための、独自の時間基準発生技法を利用する信号完全性測定のシステム及び方法である。本開示に従い作成した時間基準発生器は、位相フィルタ及び変調回路を備えており、これらは、シグマデルタ変調器の出力の関数として、高速に変化する位相信号を発生させるものである。この位相フィルタは、該高速に変化する位相信号から所望でない高い周波数の位相成分をフィルタする。フィルタされた該信号は、1以上のサンプラをクロックするために使用され、それによって上記の被テスト信号のサンプリングの事例を生成する。次に、これらサンプリングの事例を、被テスト信号の種類に適した何らかの1以上の様々な技法を使用して分析する。 (もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

CDR回路およびデューティ比制御回路

【課題】入力データのデューティ比が崩れている場合であっても、正規のデータを再生できるようにしたCDR回路を提供する。

【解決手段】データ入力端子10より入力された入力データからクロックを再生するクロック再生手段50と、制御電圧入力端子60に入力された電圧によって前記入力データの遅延時間を可変して出力する可変遅延手段30Aと、クロック再生手段50から出力されるクロックを用いて可変遅延手段30Aの出力データを保持し再生データ出力端子20に出力するデータ保持手段40と、を有する。

(もっと読む)

DLL回路

【課題】ジッタを小さくすることが可能なDLL回路を提供する。

【解決手段】各遅延回路UDCM0〜UDCMn+1を、第1及び第2インバータ15a,15b、第1及び第2ナンド回路16a,16b、スイッチングトランジスタ17及びトランスファーゲート18で構成するとともに、その第2ナンド回路16bを介して前段の遅延回路と後段の遅延回路とを接続するようにした。つまり、各遅延回路にて、1つの第2ナンド回路16bを介して、後段の遅延回路からの出力クロック信号を反転させて前段の遅延回路に出力した。詳述すると、各遅延回路は、その第2ナンド回路16b中の1個のトランジスタを駆動させて後段の遅延回路からの出力クロック信号を反転させて前段の遅延回路に出力する。

(もっと読む)

信号受信装置

【課題】小型化および低消費電力化が可能な信号受信装置を提供する。

【解決手段】本発明の信号受信装置は、N個の信号受信ブロック(Nは2以上の整数)を備え、N組のシリアル信号とサイクル数がそれぞれ等しいN個のクロックとを受信する。第1の信号受信ブロックは、第1のクロックと第1の内部クロックとの位相差を表す位相差信号を生成する位相差検出回路と、位相差信号の値に応じて第1のクロックの位相を遅延させた第1の内部クロックを生成する第1の位相遅延回路と、第1の内部クロックに基づいて第1組のシリアル信号を変換するシリアル−パラレル変換回路とを有する。他の第nの信号受信ブロックは、第1の信号受信ブロックからの位相差信号の値に応じて第nのクロックの位相を遅延させた第nの内部クロックを生成する第nの位相遅延回路と、第nの内部クロックに基づいて第n組のシリアル信号を変換するシリアル−パラレル変換回路とを有する。

(もっと読む)

信号送信回路

【課題】 チップ間で送受信される複数のデータ信号間の位相差を補正する信号送信回路および信号送信方法を提供することを目的とする。

【解決手段】 本発明の信号送信回路は、データ信号を出力する出力端子101〜103と、複数の出力端子から出力される各データ信号の位相を遅延させる第1〜第3の遅延部11〜13と、第1〜第3の遅延部11〜13に遅延値を設定する遅延値設定部14と、第1〜第3の遅延部11〜13から出力される各データ信号間の位相差を計測して、位相差情報を出力する位相差検出部15と、位相差情報に基づいて、第1〜第3の遅延部11〜13がデータ信号の位相を遅延する際に用いる遅延値の補正値を算出する補正値算出部16とを備え、遅延値設定部14は、前記補正値に基づいて第1〜第3の遅延部の各遅延値を補正する。

(もっと読む)

位相シフト回路

【課題】入力信号の位相をほぼ入力信号の1周期において任意に遅延させると共に、安定した出力信号を得ることが可能な位相シフト回路を構成する。

【解決手段】D端子の最初の立上りのタイミングでローレベルの信号を出力するDFF8と、D端子の立上りのタイミングでハイレベルの信号を出力するDFF9と、DFF8またはDFF9の出力信号がハイレベルのときハイレベルの信号を出力するOR回路10と、OR回路10の出力信号に応じてオン、オフするMOSFET11と、MOSFET11がオフのとき出力信号のレベルを上昇させ、MOSFET11がオンすると出力信号のレベルを低下させるコンデンサ13と、出力信号のレベルが低下するとローレベル、出力信号のレベルが上昇するとハイレベルの信号をDFF9のR_端子に出力するためのコンパレータ3とを備える。

(もっと読む)

PLL装置

【課題】極めて高い周波数安定度が得られるPLL装置を提供すること

【解決手段】恒温槽付き水晶発振器(OCXO)から40MHzの矩形波である周波数信号によりA/D(アナログ/ディジタル)変換部により標準信号をサンプリングし、そのディジタル信号を直交変換部により直交変換処理し、標準信号とOCXOからの周波数信号との位相差に相当する位相のベクトルを複素表示したときの実数部分(I)及び虚数部分(Q)を取り出す。このベクトルの角速度を検出し、この角速度に対応する直流電圧をPWM制御部を介して生成し、OCXOに供給する。

(もっと読む)

DLL回路

【課題】Delay Locked Loop回路(DLL回路)の源クロック停止、動作中の源クロック周波数変化などの異常動作時にも、自動的にリセットを行い、正常ロックさせることが可能な擬似ロック防止回路を提供することを目的とする。

【解決手段】1はチャージポンプ回路、2は位相遅延回路、3は位相比較器、4は位相制御回路、5はリセット回路、8はチャージポンプ電圧比較回路、9は擬似ロック基準電圧発生回路である。ロック周波数による必要電圧は1のチャージポンプの電圧によって決定されるため、このチャージポンプ電圧を8のチャージポンプ電圧比較回路によりモニターし、9の擬似ロック基準電圧発生回路によって生成される、周波数ごとに変化する擬似ロック判定電圧レベル、源クロック停止判定電圧レベルと比較することで擬似ロック、源クロック停止、源クロック周波数変動を認識する。

(もっと読む)

デジタルDLL回路

【課題】位相比較回路等を用いることなく、簡単な構成で遅延フィードバック値を容易に得ることができ、複雑な制御を容易に行うことができるデジタルDLL回路を提供する。

【解決手段】遅延目標値を保持するレジスタ11、リングオシレータ12、測定周期を決めるために、外部の基準クロックRCLKをカウントする第1カウンタ13、第1カウンタ13で決まる測定周期ごとにリングオシレータ12の発振出力クロックCLKをカウントする第2カウンタ14、デジタル制御の可変遅延回路15、および第1カウンタ13のカウント値C1を基に、第1カウンタ13および第2カウンタ14のリセット、起動、さらに必要に応じて停止の制御を制御信号CTL1、CTL2に基づいて行い、第2カウンタ14のカウント値C2とレジスタの遅延目標値DVをデジタル演算して、この演算結果を可変遅延回路15に遅延制御値DCVとして与える制御回路16を有する。

(もっと読む)

遅延固定ループ装置

【課題】 1つのレプリカ遅延部を採用して外部クロックとデータまたは外部クロックと内部クロック間のスキューを補償する。

【解決手段】 遅延固定ループ装置は、レファレンスクロックをそれぞれ遅延させライジングクロックとフォーリングクロックとを生成し、レプリカディレイされたライジングクロックをレファレンスクロックに同期させ、フォーリングクロックをレファレンスクロックに同期されたライジングクロックに同期させる遅延手段と、レプリカディレイされたライジングクロックを提供するレプリカ遅延部と、ライジングクロックの同期を制御し、フォーリングクロックの同期を制御する制御手段と、遅延手段のライジングクロックをレプリカ遅延部へ伝達し、遅延手段で相互に同期された前記ライジングクロックとフォーリングクロックのパルス幅を調節して出力パルスを生成するDCC出力部とを含む。

(もっと読む)

パワーダウンモードの間、周期的にロッキング動作を実行する機能を有するDLL及びそのロッキング動作方法

【課題】本発明は、パワーダウンモードの間、周期的にロッキング動作を実行する機能を有するDLL及びそのロッキング動作方法に関する。

【解決手段】DLLはグローバルクロック発生器、クロック遅延部、及びパワーダウン制御部を含む。パワーダウン制御部は、複数のグローバルクロック信号中の一部と、上記位相検出信号、及びパワーダウン信号に応答し、上記入力クロック信号を上記グローバルクロック発生器と上記クロック遅延部にそれぞれ出力する。パワーダウンモードの間、クロック遅延部は周期的に入力クロック信号を受信するごとにイネーブルされてロッキング動作を実行する。従って、パワーダウンモードの間、DLLの消費電力が減少することができ、クロック遅延部の周期的なロッキング動作により、パワーダウンモードの間、外部クロック信号と内部クロック信号の間の位相差が減少するため、パワーダウンモード以後にDLLが高速で動作することができる。

(もっと読む)

検証回路

【課題】クロック周波数が高くてもクロック復元回路(検証回路)を作る回路素子の最大動作速度の境界で幾つかの設計上の問題の克服を図る。

【解決手段】検証回路80は,循環制御レジスタ(32)の2個以上連続する記憶素子の第1セットに接続され,第1セット記憶素子のいずれかが第1値のときに第1状態を持ち,第1セット記憶素子の全てが第2値のときに第2状態を持つ第1チェック信号を生成する第1チェック手段82と、レジスタの2個以上の連続する記憶素子の第2セットを形成する残りの記憶素子に接続され,第2セット記憶素子のいずれかが第1値のときに第1状態を持ち,第2セット記憶素子の全てが第2値のときに第2状態を持つ第2チェック信号を生成する第2チェック手段84と、第1および第2チェック手段に接続され第1および第2チェック信号が同じ状態を持つとき制御パターンが不正であることを示す検出信号を生成する同一状態検出手段86とを備えるように構成する。

(もっと読む)

タイミング補正装置、遅延レンジ検出回路及び遅延ゲイン検出回路

【課題】動作条件の影響を受けにくく、安定したデータ受信を可能とするタイミング補正装置を提供する。

【解決手段】タイミング補正装置であって、制御信号と制御電圧とに応じて第1の信号を遅延させて、得られた遅延信号を出力する可変ディレイラインと、第2の信号と前記遅延信号との間の位相を比較する第1の位相比較器と、前記位相比較器の位相比較結果に応じて、前記第2の信号と前記遅延信号との間の位相差が小さくなるように、前記制御電圧を生成して出力する遅延制御回路と、前記制御電圧を変化させて、前記第1の信号と前記遅延信号とに基づいて前記可変ディレイラインの特性を検出し、前記制御電圧を所定の初期値にしたときに必要な特性が得られるように、前記可変ディレイラインの初期設定を行うための信号を、前記制御信号として求め、出力する可変ディレイライン制御回路とを備える。

(もっと読む)

位相制御回路

【課題】経時変化や温度変化に拘らず、常に最適なタイミングの調整をすることが可能な位相制御回路を実現する。

【解決手段】位相を制御する位相制御回路において、クロック信号を遅延する可変遅延回路と、遅延されたクロック信号がクロック入力端子に入力され、データ信号がデータ入力端子に入力される第1のフリップフロップ回路と、データ信号がクロック入力端子に入力され、遅延されたクロック信号がデータ入力端子に入力される第2のフリップフロップ回路と、第2のフリップフロップ回路の出力信号に基づいて可変遅延回路の遅延量を制御する積分回路とを備える。

(もっと読む)

遅延を選択可能な遅延ロック・ループ

【課題】改良された遅延ロック・ループを提供する。

【解決手段】DLLは、位相検出信号と結合された制御モジュールを含む。制御モジュールは位相検出信号を用いてフィードバック選択信号及び出力選択信号を生成する。フィードバック選択信号及び出力選択信号はマルチプレクサに結合される。各マルチプレクサはマルチタップ遅延ライン(MTDL)に結合される。MTDLは、2つのマルチプレクサによって選択可能な複数の遅延された信号を提供する。フィードバック選択信号に結合された第1マルチプレクサは、フィードバック・クロック信号を選択する。出力選択信号に結合された第2マルチプレクサは、DLL出力信号を選択する。制御モジュールは、出力信号の遅延をプログラム又は設定するために使用できる遅延選択信号などのような、他の信号を受け取ることができる。更に、複数の出力信号をDLLから得ることができる。

(もっと読む)

適応的遅延調整を有する位相補間器

【課題】 参照信号と補間信号間の位相関係を確実に保持し、より小さく、より簡単な構成の装置を実現するために応用可能な位相補間器を提供する。

【解決手段】 位相補間器は、2つの可調整遅延器30及び31、可調整遅延器30で遅延された信号と可調整遅延器31で遅延された信号との位相差を検出する位相比較器32、位相比較器32の出力を積分する積分器33、可調整遅延器30及び31の制御電圧を設定する乗算器34−1、34−2を備える。位相比較器32と積分器33を備えるフィードバックループは、可調整遅延器30の遅延量を制御し、{ACK1、ACK2}及びICK間の位相関係を確実に保持し、安定なICK位相を実現する。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

161 - 180 / 225

[ Back to top ]