Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

101 - 120 / 225

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

位相同期回路及び半導体チップ

【課題】 複数のチップ内の内部回路に供給される動作タイミング用のクロック信号の位相を正確に同期させることができる位相同期回路を提供する。

【解決手段】 第1チップ内において第1クロック信号を遅延させて第2クロック信号を生成し、2クロック信号を第1内部回路の動作タイミング用として第1内部回路に供給する第1遅延手段と、第2クロック信号を遅延させて第3クロック信号を生成する第2遅延手段と、第2チップ内において第1クロック信号を第1チップとの間の第1配線を介して入力し、その入力した第1クロック信号を第2内部回路の動作タイミング用として第2内部回路に供給する入力手段と、第1入力手段によって入力された第1クロック信号を第2配線を介して帰還クロック信号として第1チップに帰還させる帰還手段と、第3クロック信号と帰還クロック信号との位相差が減少するように第1及び第2遅延手段各々の遅延時間を制御する位相比較手段とを備える。

(もっと読む)

PLL回路およびディスク再生装置

【課題】簡易な演算処理にて、適時かつ迅速に、周波数誤差を検出でき、これにより、サンプリングクロックの位相誤差を円滑に補正できるPLL回路を提供する。

【解決手段】再生信号の立ち上がり時に検出された位相誤差量が、遅延回路115と減算回路116に供給される。減算回路116は、供給された位相誤差量と一回前に供給された位相誤差量(遅延回路115からの出力)とを減算する。この減算結果をもとに、時間軸上における位相誤差量の傾き値Kp(周波数誤差)が傾き値算出回路117にて算出される。同様に、再生信号の立ち下がり時に検出された位相誤差量から傾き値Knが傾き値算出回路120にて算出される。制御回路121は、傾き値Kp,Knの何れかが閾値を超えると制御信号を出力する。セレクタ111は、制御信号が入力されると位相誤差量に替えてグランド信号をLPF112に供給する。

(もっと読む)

バーニア遅延回路、それを用いた時間デジタル変換器および試験装置

【課題】高精度にキャリブレーションが可能なバーニア遅延回路を提供する。

【解決手段】リングオシレータ10は、入力されたバイアス信号SbiasGに応じた周波数で発振する。バイアス信号調節部12は、リングオシレータ10の発振周波数が、所定の基準周波数と一致するように、帰還によりリングオシレータ10に対するバイアス信号SbiasGを生成する。個別バイアス回路14は、N個の第2可変遅延素子D21〜D2Nごとに設けられた複数のバイアス回路BIAS1〜BIASNを備える。各バイアス回路BIAS1〜BIASNは、バイアス信号Sbias2A1〜Sbias2ANを個別に調節可能に構成される。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

フレームパルス信号ラッチ回路および位相調整方法

【課題】フレームパルス信号とクロックとの位相調整を自動化する。

【解決手段】フレームパルス信号ラッチ回路は、パルス幅をmクロック周期より長くしたフレームパルス信号FPINを出力するパルス幅伸張部1と、位相を調整した出力クロックCLK’を生成する位相調整部3と、フレームパルス信号FPINをラッチするフリップフロップ4と、フレームパルス信号FPOUTに対して、1〜mクロックシフトした各信号を生成し、フレームパルス信号FPOUTとクロックシフトした各信号との論理積の結果に基づいてレーシング状態を検出するレーシング検出部5と、位相調整部3に対して異なる位相調整量を順次選択して指示し、レーシング状態が検出された際の最悪位相調整量に基づいて、最適位相調整量を決定して位相調整部3へ指示する制御部6とを備える。

(もっと読む)

クロック再生回路

【課題】短いビット同期時間、クロックワンダー追随性能、高い高周波ジッタ耐性、を同時に満たすクロック再生回路を提供する。

【解決手段】入力データ信号101と再生クロック102との位相差を検出する位相差検出回路103、位相差検出回路103の出力を平均化する平均化回路104、位相差検出回路103の出力をサンプル/ホールドするリセット付サンプル/ホールド回路105、平均化回路104の出力の積分値とリセット付サンプル/ホールド回路105の出力値との和に相当する位相の再生クロック102を生成する再生クロック生成回路106を備える。リセット付サンプル/ホールド回路105は、バースト伝送開始信号110を受けて位相差検出回路103の出力をサンプル/ホールドし、バースト伝送終了信号111を受けてホールドしている値を初期値にリセットする。

(もっと読む)

パルス位相調整方法および装置

【課題】事前に位相ずれの評価や調整を行うことなく、フレームパルスとクロックとの間の位相変化を自動調整することができる。

【解決手段】位相制御部30により、位相調整部10での入力クロックCLKinに対する位相調整量を変化させて、レーシング検出部20により、このような危険なレーシング状態を検出し、位相制御部30により、その時の最悪位相調整量に基づいて、入力フレームパルスFPinを安定してラッチできる最適位相調整量を決定する。

(もっと読む)

DLL回路及びこれを用いた半導体装置、並びに、DLL回路の制御方法

【課題】チップ上における占有面積が小さく、広範囲なクロック周波数に対応可能なDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させるディレイライン210と、ディレイライン210による遅延量を制御する制御回路とを備える。ディレイライン210は、従属接続された複数の可変遅延素子500を有し、可変遅延素子500は、バイアス電流量によって遅延量が変化する差動回路構成であり、制御回路は、バイアス電流量を設定する第1の制御部300と、複数の可変遅延素子500のうち出力を取り出す可変遅延素子を選択する第2の制御部400とを有している。本発明によれば、可変遅延素子によってディレイラインが構成されていることから、少ない段数にて広範囲なクロック周波数に対応することが可能となる。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティー比特性を有するクロックを生成し、半導体集積回路の動作をより安定的に支援するDLL回路およびその制御方法を提供する。

【解決手段】本発明のDLL回路は、基準クロックを所定の分周比で分周して分周クロックを生成するクロック分周手段;前記分周クロックに対する遅延固定動作を行って遅延クロックを生成するフィードバックループ;前記遅延クロックを前記基準クロックの半周期だけ遅延させて半周期遅延クロックを生成する半周期遅延手段;および前記遅延クロックと前記半周期遅延クロックを組み合わせ演算して出力クロックを生成する演算手段;を含むことを特徴とする。

(もっと読む)

位相差平滑化装置

【課題】多相クロック生成及び伝送の過程において発生した多相クロックの位相誤差を低減する。

【解決手段】入力多相クロックのうち所望の位相関係にある複数のクロックを入力して各クロックの位相に所望の重み付けをする重み付け手段と、重み付けされたクロックを加算する加算手段と、を有する位相フィルタ回路を前記多相クロックの位相数と同数備え、位相フィルタ回路から出力されたクロックを出力多相クロックとして出力する。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティ比特性を有するクロックを生成する。

【解決手段】本発明は、デュアルループタイプ(Dual Loop Type)のDLL回路であって、第1位相検知信号に応答し、第1遅延制御信号を生成して第1遅延ラインの遅延量を制御し、第1遅延量情報信号を出力する第1遅延制御手段と、第2位相検知信号に応答し、第2遅延制御信号を生成して第2遅延ラインの遅延量を制御し、第2遅延量情報信号を出力し、前記第1遅延制御信号と半周期情報信号に応答して前記第2遅延ラインの遅延量を再び制御する第2遅延制御手段と、前記第1遅延量情報信号と前記第2遅延量情報信号の入力を受け、基準クロックの半周期情報を抽出して前記半周期情報信号を生成する半周期検知手段と、前記第1遅延ラインの出力クロックと前記第2遅延ラインの出力クロックを組み合わせてデューティ比補正クロックを出力するデューティーサイクル補正手段とを含む。

(もっと読む)

信号生成回路

【課題】基準クロックの周期より細かい周期で制御された複数の出力信号を出力する信号生成回路を提供する。

【解決手段】本発明にかかる信号生成回路は、基準クロックを出力する状態と、基準クロックに基準クロックの1周期より短い第1時間の遅延を持たせた信号を出力する状態と、を切り換え可能な入力段遅延回路10と、入力段遅延回路10の出力が変化した時点から入力段遅延回路10の出力を基準クロックの1周期より短い第2時間保持するゲート回路33を有し、ゲート回路33の出力に対応する信号を出力する制御部30と、制御部30の出力信号に第2時間の遅延を持たせた信号を出力する出力段遅延回路20と、を備え、入力段遅延回路10は、制御部30の出力信号の変化に応答して出力状態の切り換えを行う。

(もっと読む)

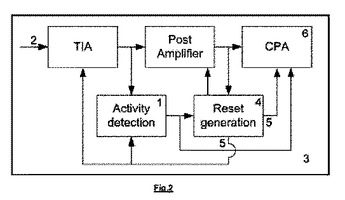

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

遅延固定ループ

【課題】ノイズの干渉、PVTの変動、及び頻繁に起こるパワーダウンモードへの進入・脱出など、半導体メモリ素子の最悪の状況でも安定的に動作できる遅延固定ループを提供すること。

【解決手段】遅延固定をなすために、ソースクロックの第1のクロックエッジ及び第2のクロックエッジに対応する第1の遅延クロック及び第2の遅延クロックを生成する遅延固定部と、前記第1の遅延クロックと第2の遅延クロックとの位相差を検出して加重値選択信号を出力する位相検出部と、前記第1の遅延クロックと第2の遅延クロックとの遅延固定時点から予定された期間に獲得した前記加重値選択信号を格納する加重値格納部と、該加重値格納部に格納された加重値選択信号に対応する加重値を反映し、前記第1の遅延クロックの位相と第2の遅延クロックの位相とを混合して遅延固定ループクロックとして出力する位相混合部とを備えることを特徴とする。

(もっと読む)

遅延ロックループ回路

【課題】クロック信号CKに対し、1周期Tだけ正確に遅れた出力信号OT、及び、可変遅延回路70に用いたn個の各遅延セルにて均等な遅延時間T/nの出力信号を得る。

【解決手段】DLL回路は、制御信号CTLに基づき遅延時間が変わる同一構成の遅延セル50−11,〜,50−3nにより構成される第1、第2の入力ゲート40−1,40−2及び可変遅延セル70と、遅延セル50−11と入力容量が同一の位相比較回路80内の第3、第4の入力ゲート82−1,82−2とを有している。位相比較回路80は、クロック信号CKが入力ゲート40−1を経た出力信号CK−Aと、クロック信号CKが入力ゲート40−2と可変遅延回路70とを経て遅延した出力信号OTとの各信号波形の位相を比較する。その比較結果は、負帰還を掛ける制御信号CTLとして、入力ゲート40−1、40−2及び可変遅延回路70へ与えるようにした。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】クロック生成回路が、ロック状態とは180°位相のずれた状態(擬似ロック状態)の出力クロックを出力する可能性がある。

【解決手段】遅延同期ループ型のクロック信号生成回路として、(a)第1のクロック信号を遅延して第2のクロック信号を生成する遅延線路と、(b)第2のクロック信号が第1のクロック信号に位相同期するように、遅延線路における遅延量を可変制御する遅延量制御部と、(c)第1のクロック信号と第2のクロック信号との擬似ロック状態を検出する擬似ロック検出部と、(d)擬似ロック状態の検出時、遅延線路の遅延量を変更する擬似ロック状態解除部とを有するものを提案する。

(もっと読む)

タイミング調整装置

【課題】温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

(もっと読む)

位相調整装置

【課題】設計時以降に生じる位相差の変動を内部で自動的に調整することで、予め設定された位相差を有する2つの信号を出力する。

【解決手段】2つのクロック信号の位相差を予め定められた位相差に調整する位相調整装置であって、第1クロック信号に対する第2クロック信号の遅延量を選択的に変更可能な遅延部11と、前記遅延量を制御する制御部12とを備え、前記制御部12は、準備モードにおいて、前記遅延量を第1の時間間隔で段階的に増加又は減少させ、遅れ期間、又は、進み期間を検出し、調整モードにおいて、前記遅れ期間又は前記進み期間と同じ長さの期間において第2の時間間隔で前記遅延量を段階的に変化させることで、前記第2クロック信号の位相差を予め定められた位相差に調整し、前記第2の時間間隔と前記第1の時間間隔との比は、180度と予め定められた位相差との比に等しい。

(もっと読む)

クロック生成回路及び電子機器

【課題】入力クロックから出力クロックまでの遅延時間のロックと出力クロックの精度の良い位相調整とを両立できるクロック生成回路、電子機器の提供。

【解決手段】クロック生成回路は、クロックCK1を受け、クロックCK2を出力するスキュー調整回路10と、クロックCK2を受け、クロック遅延時間がロックされた多相クロックRCK1〜RCKMを生成して出力するDLL回路40と、多相クロックのいずれかに対応するクロックを、出力クロックCKQとして出力するクロック出力回路70を含む。スキュー調整回路10は、クロックCK1を遅延させたクロックをクロックCK2として出力する遅延回路30と、多相クロックのいずれかに対応するクロックCK3を受け、クロックCK1とCK3の位相が一致するように、クロックCK1に対するクロックCK2の遅延時間を調整する遅延調整回路20を含む。

(もっと読む)

101 - 120 / 225

[ Back to top ]