Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

41 - 60 / 225

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

ジッタ除去回路

【課題】従来では、基準クロック生成回路が生成するクロックにジッタが発生するという問題があった。

【解決手段】本発明にかかるジッタ除去回路は、基準クロック51のジッタを除去するジッタ除去回路であって、サンプリングクロック52に同期して基準クロック51のエッジを検出するラッチ回路12と、基準クロック51のエッジ間隔をカウントするカウンタ13と、各エッジ間隔のカウント数に基づいて基準クロック51の位相を調整する位相調整回路14と、を備える。

(もっと読む)

クロックデータリカバリー回路およびその動作方法

【課題】回路規模および消費電力を削減すること。

【解決手段】クロックデータリカバリー回路3では、クロック発生器300のサンプリングクロックに応答してA/D変換器301がA/D変換し、順次生成の複数のデジタル出力信号はデータ補正部303に供給され、順次生成の複数の補正デジタル信号は位相比較器305に供給される。位相比較器305の出力はループフィルタ306を介してタイミング生成部304に供給され、複数の再サンプリングタイミングの情報Pvcoはデータ補正部303に供給される。検出回路302はアナログ入力信号の周期Tとサンプリングクロックの周期tの比T/tの誤差情報nvcoを生成して、タイミング生成部304は複数の遅延時間で複数の再サンプリングタイミングを生成して、データ補正部303は複数の補正率で複数の補正デジタル信号を生成する。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

半導体集積回路およびその動作方法

【課題】比較的小さな電源電圧による速度変動を高精度で抑制して比較的大きな電源電圧による速度変動を高速で抑制する。

【解決手段】半導体集積回路は、第1と第2の機能ブロックMOD00、01、クロック生成回路PLL、クロック供給回路CS0を具備する。第1と第2の機能ブロックMOD00、01には、電圧値の相違する第1と第2の電源電圧VDD00、1が供給される。MOD00は一方の電源電圧VDD01が供給可能な第1の内部回路BUF00と第1の論理回路MFF00を含み、MOD01は他方の電源電圧VDD00が供給可能な第2の内部回路BUF01と第2の論理回路MFF01を含む。クロック供給回路CS0は微調遅延段回路FC0と粗調遅延段回路CC0と位相差計測回路RSM0を含み、RSM0は第1と第2の動作クロック信号COUT00、01の位相差に応答してFC0の遅延時間TF0とCC0の遅延時間TC0を制御する。

(もっと読む)

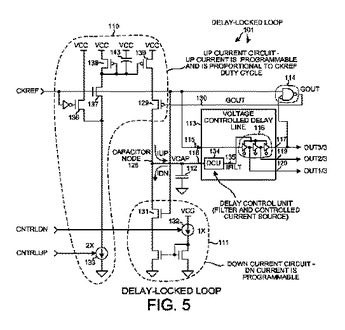

入力信号デューティサイクル変動に依存しない遅延を有する遅延ロックループ

遅延ロックループ(DLL)は、第1の信号を「遅延時間」だけ遅延させ、それによって第2の信号を生成するために、遅延線を使用する。キャパシタは、第1の信号の第1のエッジで開始して第2の信号のエッジまで続く第1の率で充電される。次いで、キャパシタは、第1の信号の別のエッジまで第2の率で放電される。制御ループは、キャパシタが充電される量が、キャパシタが放電される量と同じであるように、遅延時間を制御する。遅延時間は、一定であり、第1の信号のデューティサイクルの変動に実質的に依存しない。一例では、デューティサイクル歪み相殺(duty cycle distortion cancellation)は、第1の信号のデューティサイクルの変化に対して比例して第1の率を変更することによって達成される。別の例では、第1の率および第2の率は、第1の信号のデューティサイクルに依存しない。  (もっと読む)

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路は、補間信号の位相を精度良く制御することができないという問題がった。

【解決手段】本発明にかかる多相クロック生成回路は、クロック信号1,2に基づいて、クロック信号1,2に対応する出力クロック信号間の位相を補間する補間信号を生成し、出力する位相補間回路102と、補間信号の位相を調整する第1の制御信号を生成し、位相補間回路102に対して出力する制御回路103aと、を備えた多相クロック生成回路であって、制御回路103aは、補間信号の論理値変化のタイミングを検出するためのタイミング検出回路104と、タイミング検出回路104の検出結果に応じた第1の制御信号を生成する制御信号生成回路105と、を備える。このような回路構成により、補間信号の位相を精度良く自動で制御することができる。

(もっと読む)

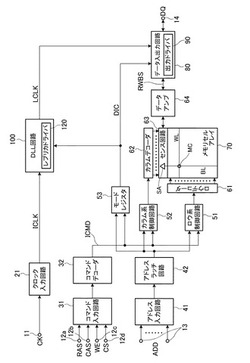

DLL回路

【課題】参照クロックの生成のために、360度の位相差の素子数が特定される際に、遅延素子の温度等が変化しても、特定時間が長くならないこと。

【解決手段】遅延素子の温度等の動作状況情報を取得する動作状況認識部110と、前記動作状況情報に対応する遅延制御情報を生成する初期遅延決定部120と、前記遅延制御情報による遅延クロックを生成する可変遅延回路130と、位相差を検出する位相比較回路140と、検出に応じ、360度の位相差の遅延制御情報を特定する遅延制御回路150とを含むDLL回路。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

位相調整装置及び方法

【課題】CCDを駆動するクロック信号を自動的に最適な位相に調整し、CCDからクロック信号成分が出力されない位相調整装置及び方法を提供する。

【解決手段】本発明の位相調整装置は、2相駆動型の電荷結合素子を用いたフィルタ回路に入力する第1の信号及び第2の信号の位相関係を調整する位相調整装置において、第1の信号に対して遅延を与える遅延付与手段と、遅延付与手段により遅延が与えられた第1の信号と、第2の信号とを加算又は減算する合成手段と、合成手段から出力する参照信号の電力値に基づいて、第1の信号と第2の信号とが逆位相となるように遅延付与手段の遅延設定量を制御する位相調整制御手段とを備えることを特徴とする。

(もっと読む)

遅延ロックループ回路、信号遅延方法

【課題】回路面積を大きくすることなく、遅延ロックループ回路を提供すること

【解決手段】逓倍PLL107は、基準クロックを逓倍して出力する。DLL211は、逓倍PLL107から出力されたクロックと、逓倍PLL107から出力されたクロックを遅延させたクロックと、を比較し、比較結果に基づいて所定の遅延量を持つ遅延信号を生成する。遅延制御信号演算回路108は、DLL211が生成した遅延信号に基づき、所望の遅延制御信号を生成する。第1の遅延回路102は、遅延制御信号演算回路108が生成した遅延制御信号に基づいて、入力信号を遅延させる。

(もっと読む)

異種周期クロックドメイン間の同期化システム、同期化装置、同期化失敗検出回路及びデータ受信方法

【課題】異種周期クロックドメイン間の同期化システム、同期化装置、同期化失敗検出回路及びデータ受信方法を提供する。

【解決手段】本発明の一様態による同期化システムは、異種周期の第1クロックと第2クロックとによってそれぞれ動作するセンダーとレシーバーを含む異種周期クロックドメイン間の同期化システムであって、第1クロックを第1時間遅延させた予測クロックを出力するセンダー及び予測クロックを利用して第1クロックと第2クロック間の同期化失敗が発生するか否かを予測し、予測結果によって選択的に第2クロックを第2時間遅延させて第1クロックと同期化させるレシーバーを含む。

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

遅延固定ループ回路

【課題】外部電源電圧のレベル変動とは関係なく安定的に遅延固定動作を行う遅延固定ループ回路を提供する。

【解決手段】外部電源電圧のレベルを検出する電圧レベル検出部280と、ソースクロック及びフィードバッククロックの位相を比較する位相比較部200と、電圧レベル検出部280の出力信号に応じて、第1および第2遅延ユニット単位のうち何れか一方を開始遅延ユニット単位として、他方を連結遅延ユニット単位としてそれぞれ指定し、位相比較部200の出力信号に応答して、遅延量が、所定の遅延量までは前記開始遅延ユニット単位で、前記所定の遅延量以後には前記連結遅延ユニット単位で前記ソースクロックを遅延させ、遅延固定クロックDLLCLKとして出力するクロック遅延部220と、前記遅延固定クロックに前記ソースクロックの実際の遅延条件を反映して、前記フィードバッククロックとして出力する遅延複製モデル部240とを備える。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】DLL回路のロックに要する時間を短縮する。

【解決手段】外部クロック信号CLKとレプリカクロック信号RCLKの位相差量を検出する位相差量検出回路100と、位相差量に基づいて外部クロック信号CLKを遅延させることにより内部クロック信号LCLKを生成する可変遅延回路21と、内部クロック信号LCLKを遅延させることによりレプリカクロック信号RCLKを生成するレプリカバッファ24とを備える。本発明によれば、外部クロック信号CLKに対してレプリカクロック信号RCLKの位相が進んでいるか或いは遅れているではなく、その位相差量に基づいて可変遅延回路21が制御されることから、位相差量が大きい場合であっても、高速にDLL回路をロックさせることが可能となる。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

位相補正装置、位相補正方法

【課題】無線送信用の電力増幅器の出力をフィードバックする位相補正装置及び位相補正方法において、フィードバック系の安定性を向上させたものを提供すること。

【解決手段】位相検出器10により検出された位相誤差(電圧CV)に対して、想定される位相誤差の全範囲でスイープさせた位相量(スイープ信号の電圧VSWP)を付加して、位相補正の目標値(電圧CV’)とする。これにより、位相補正処理の初期において、PLLのロックレンジへの引き込みを素早く行う。

(もっと読む)

遅延信号生成回路、及び、遅延回路

【課題】入力された信号に所定の遅延時間を安定的に挿入し得る遅延信号生成回路及び遅延回路を提供する。

【解決手段】遅延信号生成回路は、供給される電源の電圧によって、その遅延時間が変化する、1又は複数の第1遅延回路と、前記第1遅延回路と同一の回路構成を有しており、供給される電源の電圧によって、その遅延時間が変化する第2遅延回路と、前記第1遅延回路と前記第2遅延回路に電源を供給する、制御電源回路とを有する、電源供給回路と、を備えるとともに、前記制御電源回路は、入力クロック信号と遅延クロック信号との間の位相差を検出し、前記位相差に基づいて、前記入力クロック信号と前記遅延クロック信号との間の位相差が解消されるように、前記第1遅延回路と前記第2遅延回路に供給する電源の電圧を制御する。

(もっと読む)

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

41 - 60 / 225

[ Back to top ]