Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

81 - 100 / 225

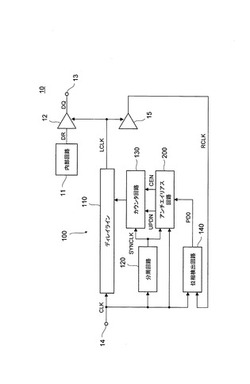

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

情報システムおよび半導体装置とその制御方法

【課題】周期の小さいジッタに対する低減効果を向上する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路14を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路14における遅延量を制御する。位相補正回路21は、入力クロック信号CLKiおよび出力クロック信号CLKoを入力とし、DLL回路がロック状態に入った後に、入力クロック信号CLKiおよび出力クロック信号CLKoの位相がずれた場合に、出力クロック信号CLKoの位相に基づいて入力クロック信号CLKiの位相に補正を加え、電圧制御遅延回路14に出力する。

(もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

DLL回路とその制御方法

【課題】安定的にジッタを低減する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路12を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路12における遅延量を制御する。位相比較結果判定回路15は、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果を所定の期間に亘って積算し、積算結果の分布に基づいて遅延量を制御する。

(もっと読む)

位相補間制御装置

【課題】位相補間制御装置中のノイズフィルタ帯域幅を動的に調整し、位相補間制御装置を広く応用することができる上、CDRのロック時間を短縮させることができる位相補間制御装置を提供する。

【解決手段】位相補間制御装置400は、第1の信号と第2の信号との位相関係を表す指示を受信し、複数の双方向シフトレジスタを含む。複数の双方向シフトレジスタは、互いに直列接続され、位相補間制御装置が受信した指示が、第1の信号の位相が第2の信号の位相より進んでいることを表すとき、直列接続された複数の双方向シフトレジスタをそのうちの1方向でシフトさせる。位相補間制御装置400が受信した指示が、第1の信号の位相が第2の信号の位相より遅れていることを表すとき、直列接続された複数の双方向シフトレジスタを他の方向でシフトさせる。

(もっと読む)

DLL回路

【課題】本発明は、電圧制御発振部を用いて多相クロックを生成し、そのうちで基準クロックに同期されるクロックを選択して、遅延クロックとして提供するDLL回路を提供する。

【解決手段】本発明は、基準クロックを単位時間だけ遅延させて複数の多相クロックを生成し、複数の多相クロックの何れか一つと基準クロックとの周波数が一致する時にイネーブルされるイネーブル信号を生成するように構成される多相クロック生成部;及び、イネーブル信号がイネーブルされると、制御信号により複数の多相クロックの何れか一つを所定時間遅延させて基準クロックの位相と比較し、複数の多相クロックのうち、基準クロックと位相が一致する多相クロックを遅延クロックとして生成するように構成される多相クロック選択部を含むことを特徴とする。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

同期周波数合成器

【課題】同期周波数合成器によるクロック生成装置を提供する。

【解決手段】クロック生成装置において、2つの入力クロックに関連付けられた基準位相の範囲内の位相値を有する出力を生成する位相補間器121を有する。ロジック・ユニット130は、位相補間器121の複数の位相設定を決定するために結合され、分周器122は位相補間器121に結合され、変更可能な分周設定に基づき出力クロックを生成する。

(もっと読む)

信号再生装置

【課題】受信したDVB−ASI信号からジッタなどによる位相変動を抑制したクロックを再生可能とする。

【解決手段】47コード検出器4で受信信号のTSパケットから検出される47hコードパルスEは、分周器14でn分周された後、位相差検出回路15に供給され、PLL回路の分周器8からのクロックF1との位相差K(=Δφ)が検出される。位相差分割・記憶回路16では、この位相差Kから分割位相差Lが生成される。位相代替処理回路17では、47hコードパルスEがクロックF1よりも位相の進みがあると、分割位相差Lにより、クロックF1よりΔφ/n進んだ位相代替パルスMを生成し、47hコードパルスEがクロックF1よりも位相の遅れがあると、分割位相差Lにより、クロックF1よりもΔφ/n遅れた位相代替パルスMを生成し、クロックF1とともに、夫々PLL回路の位相比較器5に供給する。

(もっと読む)

DLL回路及びその制御方法

【課題】クロックのパルス幅が狭い場合、及び広い場合において、合成回路の誤動作を回避し、動作周波数の高速化に対応可能とするDLLの提供。

【解決手段】外部クロック(CK)の第1遷移(Rise)に対応して互いに異なる遅延時間の信号を出力し、CKの第2の遷移(Fall)に対応して互いに異なる遅延時間の信号を出力する第1の可変遅延回路20と、第1の可変遅延回路からの信号をそれぞれ受ける第2の可変遅延回路10R、10Fからの出力信号を合成して出力する第1の合成回路30とを備え、第2の可変遅延回路は第1の可変遅延回路からの信号からワンショットパルスを生成するワンショットパルス生成回路と、リセット端子を備えるラッチ回路と、ラッチ回路のセット出力の遷移エッジを受け、所定の比率で合成した信号を出力する第2の合成回路と、を備え、第2の合成回路の出力がラッチ回路のリセット端子に入力される。

(もっと読む)

DLL回路

【課題】高精度な同期特性を有するDLL回路を提供する。

【解決手段】第1クロック信号CLK1が入力され、第1クロック信号CLK1を遅延した第2クロック信号CLK2を出力するとともに、制御信号Vcにより遅延時間が可変される可変遅延回路11と、第1クロック信号CLK1および第2クロック信号CLK2が入力され、第1クロック信号CLK1と第2クロック信号CLK2との位相を比較して、その位相差ΔΦに応じた信号を出力する位相検出回路12と、位相検出回路12の出力V1を積分する積分回路13と、積分回路13の出力V2を予め定めた基準値Vrefと比較し、比較結果を出力する比較回路14と、比較回路14の出力V3を平均化し、高周波成分を除去した信号を、制御信号Vcとして可変遅延回路11に出力するローパスフィルタ15と、を具備する。

(もっと読む)

DLL回路

【課題】LSIを使用するユーザに制約を課すことなく、LSIを使用するユーザ毎に異なる様々なEMI防止機能の要求に対応するために、電磁放射が生じる周波数とその周波数における電磁放射強度を制御する。

【解決手段】DLL回路は、入力信号に基づいて同期基準信号を生成する入力回路101と、同期基準信号を遅延する第1遅延部102と、第1遅延部102によって遅延された同期基準信号の同期位置を調整し、同期対象信号を生成するタイミングオフセット回路103と、同期基準信号と同期対象信号との位相差を比較する位相比較回路105と、位相比較回路105の比較結果に基づいて第1遅延部102の出力信号を選択する第1制御回路106と、同期基準信号又は同期対象信号を遅延する第2遅延部104と、所定の設定情報を記憶する設定情報記憶回路108と、位相比較回路105の比較結果が所定の範囲内である場合に、設定情報記憶回路108に記憶された設定情報に基づいて第2遅延部104の出力信号を選択する第2制御回路107と、を備えている。

(もっと読む)

半導体集積回路及びその制御方法

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

PLL回路、並びに通信装置及びその折り返し試験方法

【課題】SSCのジッタを抑制し、SSCの変調度を滑らかに遷移させることが可能なSSC生成機能を有するPLL回路を提供する。

【解決手段】SSCコントローラ18は、SSCの変調プロファイルに応じて予め定められたタイミングで位相シフト量を変更するよう位相補間器15を制御し、出力クロック信号C_OUTの変調度を周期的に変更させる。さらに、SSCコントローラ18は、帰還クロック信号C_FBの一周期内において位相補間器15より出力される位相シフト信号C_PSに与える総位相シフト量を、当該総位相シフト量と直前の一周期における総位相シフト量との差分が常に基本遅延量Δ以下となるよう制御する。ここで、基本遅延量Δは、出力クロック信号C_OUTの周期T_OUTを位相補間器15の位相分解能Nrで除算した値(つまり、T_OUT/Nr)である。

(もっと読む)

多相クロック生成回路、オーバーサンプリング回路及び位相シフト回路

【課題】より位相差の微小な多相クロックを生成しつつ、消費電流の増大を抑制した多相クロック生成回路及びオーバーサンプリング回路を提供する。

【解決手段】1対の入出力端子と、遅延量制御端子にバイアスした電圧に応じた遅延量を発生させる2つの遅延ラインの出力の位相差を検出する位相比較器13と、位相比較器13の出力を平均化する平均化フィルタ14とを備え、一方の遅延量制御端子に基準電圧を接続し、他方の遅延量制御端子に平均化フィルタ14の出力を接続し各遅延ラインの出力が所定の位相差を持つように制御する遅延量制御部11と、複数かつ同数個の遅延素子を直列に接続した複数の遅延ライン21を備え、各遅延ライン21は基準電圧を接続した遅延素子22の数及び平均化フィルタ14の出力電圧を接続した遅延素子の数の組み合わせを異ならせたクロック遅延部20とを備え、所定の位相差を持つ多相クロックを生成する。

(もっと読む)

デジタルDLL回路及び半導体装置

【課題】出力信号のジッターを低減可能としたデジタルDLL回路を提供する。

【解決手段】クロック信号CLKを1周期遅延させるための固定遅延素子の段数を選択する位相判定部1と、位相判定部1で選択した固定遅延素子の段数に基づいて、入力信号INを任意の位相量だけ遅延させて出力する固定遅延素子の段数を選択する位相調整部21とを備えたデジタルDLL回路において、位相調整部21は、選択信号に基づいて、複数段の固定遅延素子と、該固定遅延素子の1段当たりの遅延時間を1/2n刻みで調整する可変遅延部とで生成する遅延時間で、入力信号INを任意の位相量遅延させた出力信号OUTを生成する。

(もっと読む)

クロックデータ修復回路

【課題】本発明は、誤同期状態から正常な同期状態へ復帰することが可能なクロックデータ修復回路を提供することを目的とする。

【解決手段】本発明の1つの実施形態は、位相検出部2と、クロック信号生成部と、出力部と、追い越し検知部8とを備えるクロックデータ修復回路である。位相検出部2は、入力データから位相情報を取得し、クロック信号生成部は、位相情報に基づき、複数のクロック信号を生成し、出力部は、入力データと、クロック信号生成部で生成した複数のクロック信号のうち選択したクロック信号とを出力する。追い越し検知部8は、選択したクロック信号が入力データを位相的に追い越しているか否かを検知し、当該検知に基づき選択したクロック信号をクロック信号生成部で生成した他のクロック信号に切り替えるように制御する。

(もっと読む)

DLL回路

【課題】補間回路の最小動作周期を低減でき、DLLの最大動作周波数を向上させることができる、DLL回路を提供する。

【解決手段】位相検知回路21は、入力される基準クロック信号とレプリカ回路17から出力されるクロック信号との位相の差を検知し遅延制御回路22に出力する。遅延制御回路22は、位差の信号を基に、基準クロック信号の位相を調整する制御信号を出力する。そして、遅延制御回路22から出力される制御信号を基に、マルチプレクサ12、13は、粗調整遅延回路10からインバータ2段分の遅延差を有する信号を選択して出力し、第1の微調整遅延回路14は、マルチプレクサから入力した2段分の遅延差の信号を基に、インバータ1段分の遅延差を有する信号を出力する。第2の微調整遅延回路15は、この1段分の遅延差を有する信号に基づいてクロック信号の位相を調整する。

(もっと読む)

81 - 100 / 225

[ Back to top ]