Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

141 - 160 / 225

デューティサイクル補正機能を有する遅延ロックループ回路およびその制御方法

【課題】PVT変動が発生しても安定して正確な遅延ロックおよびデューティサイクル補正を可能とする。

【解決手段】外部クロックが入力されて第1内部クロックを生成し、前記第1内部クロックを内部の遅延手段によって遅延して複数の第2内部クロックを出力した後にフィードバックを受けて、前記第1内部クロックとの位相差によって前記遅延手段の遅延時間を調整することにより、前記第2内部クロックの遅延ロックがなされるようにする遅延ロックループブロックと、前記複数の第2内部クロックのデューティサイクルを補正したデューティサイクル補正クロックを出力するデューティサイクル補正ブロックと、前記複数の第2内部クロックの位相比較結果に応じてデューティ補正エラーの発生を判断して、前記デューティサイクル補正クロック又は前記複数の第2内部クロックのうちの1つを前記遅延ロックループブロックにフィードバックするエラー判断部とを備える。

(もっと読む)

クロック発生回路

【課題】 DLL回路を用いたクロック発生回路においては、活性化される半導体装置が切り替わる場合に、DLL回路のロック時間が長くなるという問題がある。

【解決手段】 DLL回路の遅延調整回路を固定長遅延回路と、N個の可変長遅延回路で構成し、N個の半導体装置に内部クロックを供給する。N個の可変長遅延回路の遅延差をN個の半導体装置に対する遅延差と同じくする。選択された半導体装置に対し、遅延差がなくなるようにN個の可変長遅延回路からの遅延クロックを選択する。

(もっと読む)

CASレイテンシを利用してロッキングレゾリューション調節が可能な遅延同期ループ回路

【課題】単位遅延器の数を増やさなくとも広いロッキング範囲を有し、またロッキングサイクル時間を減らせる遅延同期ループ回路を提供する。

【解決手段】遅延ライン、位相検出器、制御回路を備える。遅延ラインは、直列連結された多数の単位遅延器を含んで制御信号に応答して選択される単位遅延器を通じて外部クロック信号を遅延させる。位相検出器は、前記外部クロック信号の位相と前記遅延ラインから出力される内部クロック信号の位相とを比較し、外部クロック信号と遅延ラインから出力される内部クロック信号間の位相差を検出する。制御回路は、前記位相検出器の出力信号に応答して前記制御信号を発して遅延制御信号に応答して前記遅延ラインのロッキング位相ステップを可変にする。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。  (もっと読む)

(もっと読む)

クロック位相シフト回路

【課題】プロセス条件、電源電圧、温度等の変動によらず、入力クロックの位相シフトの調整ができ、かつ、従来のDLL回路を用いた場合と比較して占有面積の小さいクロック位相シフト回路を提供する。

【解決手段】入力クロックを遅延させる遅延回路の遅延セルと同一の遅延セルで構成されたリングオシレータを用いて、入力クロックのm周期分の発振出力をカウントし、入力クロックの1周期分の遅延セル段数を計算して位相シフト量分の遅延セル段数を設定する。

(もっと読む)

クロックデューティ変更回路

【課題】PLL回路の構成に依存することなく汎用的に適用することができ、製造ばらつきによる出力クロック信号のデューティ比のずれを補償可能なクロックデューティ変更回路を提供する。

【解決手段】調整回路2は、デューティ比の目標値を指示する制御信号S[2:0]及び制御信号cntd[2:0]に基づいて決定される遅延時間だけ入力クロック信号PLLCKを遅延させた遅延信号lng及びshtを生成する遅延選択回路20及び21と、lng及びshtとPLLCKとを用いた論理演算により出力クロック信号PLLDを生成する演算回路23及び24とを有する。また、比較回路4は、PLLDのデューティ比が目標値と一致するか否かを判定する。さらに、補正回路3は、比較回路4による判定結果に応じて、PLLDのデューティ比と目標値とのずれを減少させるようlng及びshtに与えられる遅延時間の補正量を示すcntd[2:0]を生成する。

(もっと読む)

半導体記憶装置の遅延ロックループ回路

【課題】遅延ロックループクロックが伝送される過程で発生するタイミングエラーを未然に防止できるようにした半導体記憶装置の遅延ロックループ回路を提供する。

【解決手段】内部クロックのデューティサイクルを補正して出力するデューティサイクル補正手段と、外部クロックのクロックパルス幅を検出してパルス幅検出信号を出力するクロックパルス幅検出手段と、前記デューティサイクル補正手段の出力の位相を分離し、前記パルス幅検出信号に相応するように前記位相分離された2つの信号のうち少なくとも1つのパルス幅を調節して、遅延ロックループクロックとして出力するドライブ手段とを備えている。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

PLL回路

【課題】帰還ループに遅延回路を挿入することなく、出力信号でのジッタの発生を抑制し得るPLL回路を提供する。

【解決手段】基準信号ref−CLKと帰還信号の位相を比較する位相比較器2と、チャージポンプ4と、ループフィルター5と、電圧電流変換器6と、電流制御発振器7aと、電流制御発振器の出力信号を分周して帰還信号を生成する分周器3とを備えた帰還ループにより、出力信号out−CLKの周波数を基準信号で設定される周波数に収束させるPLL回路であって、電流制御発振器7aから負荷回路8に出力される出力信号out−DLと位相比較器2に入力される基準信号の位相をずらす遅延回路11aを帰還ループ外に備えた。

(もっと読む)

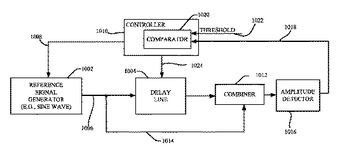

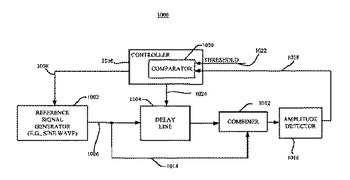

遅延線の較正

調整可能な遅延線は、目標値に、または希望の値の範囲内に遅延線の遅延を維持するように較正される。いくつかの態様において、遅延線を通った信号の累積的な遅延(例えばカウントにより示されるように)が、ある期間にわたって算定されるように、信号は遅延線を複数回通して渡される。前記カウントは、予定カウントと比較される。そして、この比較に基づいて、必要なときには、遅延線の遅延は調節される。いくつかの態様において、信号はデジタル信号を含み得る。いくつかの態様において、遅延線を通った遅延は、遅延線により信号に与えられた位相シフトにより引き起こされる信号における振幅変化の分析に基づいて算定され得る。いくつかの態様において、遅延線は、送信基準信号を生成する、および/または処理するように送信基準システムに組み入れられる。  (もっと読む)

(もっと読む)

遅延線の較正

調整可能な遅延線は、目標値に、または希望の値の範囲内に遅延線の遅延を維持するように較正される。いくつかの態様において、遅延線を通った信号の累積的な遅延(例えばカウントにより示されるように)が、ある期間にわたって算定されるように、信号は遅延線を複数回通して渡される。前記カウントは、予定カウントと比較される。そして、この比較に基づいて、必要なときには、遅延線の遅延は調節される。いくつかの態様において、信号はデジタル信号を含み得る。いくつかの態様において、遅延線を通った遅延は、遅延線により信号に与えられた位相シフトにより引き起こされる信号における振幅変化の分析に基づいて算定され得る。いくつかの態様において、遅延線は、送信基準信号を生成する、および/または処理するように送信基準システムに組み入れられる。  (もっと読む)

(もっと読む)

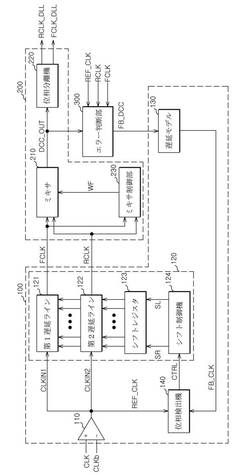

遅延同期ループ回路

【課題】遅延同期ループ回路を提供する。

【解決手段】入力された外部クロック信号を精密遅延量ほど遅延させて第1内部クロック信号として出力する第1遅延ライン、及び第2クロック信号を粗い遅延量ほど遅延させて第2内部クロック信号として出力する第2遅延ラインを具備する遅延同期ループ回路であり、該第1遅延ライン及び第2遅延ラインは順次に配され、第2クロック信号は、第1内部クロック信号を利用して生成される。これにより、粗い遅延調節と精密調節とをそれぞれ異なる形態の遅延セルを利用することによって、パワー消耗が少なく、かつジッタ発生及びPVT変数に強靭な特性を有する遅延同期ループ回路が得られる。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

移相回路

【課題】 移相量を常に一定に制御可能とし、電源電圧変動時等の影響の低減、素子バラツキの影響を低減する移相回路の提供。

【解決手段】基準周波数信号が入力されて2分配され一方の信号は位相比較器102の一方の入力となり、他方の信号は移相器101を介してその位相が移相された後に、前記位相比較器102の他方の入力となり、位相比較器102の出力はループフィルタ(LPF)103を介して差動増幅器104の一方の入力端子に入力され、差動増幅器104の出力信号により移相器101の移相量が制御されるPLLループを有し、差動増幅器104の他方の入力端子に印加される基準電圧により前記移相器101での移相量が定まる。

(もっと読む)

標準信号発生器及び標準信号発生システム

【課題】恒温設備を設けることなく位相ドリフトを低減させて、標準信号発生器のウォームアップ時間の短縮を図ること。

【解決手段】位相補正データ生成部4のA/D変換器41は、基準信号生成部1から出力された基準信号14aの周波数をサンプリング周波数として標準信号100aをA/D変換する。プログラマブル周波数ディバイダ42が分周した基準信号14aの周期で、データ間引き部43はA/D変換器41からのビート信号41aを間引き抽出する。補正量算出部40は、データ間引き部43からのビート信号43aの電圧値に基づいて、位相ドリフト量Δθdriftを算出する。その位相ドリフト量Δθdriftに基づいて標準信号100aの位相補正を行う。

(もっと読む)

数値制御型オシレータ(NCO)出力クロック位相平滑化

【課題】 入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを発生する形態とされている数値制御型オシレータ(NCO)を包含する位相平滑化回路が記載される。

【解決手段】 該複数個のNCOクロックパルスのエッジは該入力クロックのエッジに整合している。位相エラー計算モジュールが該NCOへ結合されており且つ該複数個のNCOクロックパルスの各々に対する対応する位相エラーを発生する形態とされている。クロック位相選択可能遅延が該位相エラー計算モジュールへ結合されており且つ該選択可能周波数において出力クロックを発生するために該対応する位相エラーに従って該複数個のNCOクロックパルスの各々を調節する形態とされている。

(もっと読む)

位相調整回路

【課題】システム高負荷動作中等における急激なPVT特性の変化による遅延量の変化に対応可能とする。

【解決手段】外部記憶手段とライトおよび/またはリードアクセスする際に、入力クロック信号の位相を調整して入力クロック信号に対して遅延された出力クロック信号を供給するクロック遅延調整回路100を利用して、外部回路から供給されるデータ信号およびデータストローブ信号の位相を調整する位相調整回路において、ライトデータおよび/またはリードデータを書き込む内部記憶手段と、ライトおよび/またはリードアクセスする際のタイミングマージンが確保されたときのクロック遅延調整回路の遅延パラメータの値を記録する内部記憶手段と、タイミングマージンの最適値を算出する最適値算出手段と、タイミングマージンの最適値を記録する最適値記憶手段と、を備えることを特徴とする。

(もっと読む)

ディレイ調整回路およびその制御方法

【課題】同一チップ上の半導体素子のばらつきによる遅延特性のばらつきを補正するディレイ調整回路を提供すること。

【解決手段】ディレイ調整回路は、9段のディレイ素子が直列接続されるディレイ部と、ディレイ部の7段目の信号の立ち上がりエッジである第1エッジが第1基準信号の立ち上がりエッジである第1基準信号エッジよりも進んでいるか否かを検知する第1カウンタ10と、ディレイ部の9段目の信号の立ち上がりエッジである第2エッジが第1基準信号エッジよりも遅れているか否かを検知する第2カウンタ11と、第1カウンタ10において第1エッジが第1基準信号エッジよりも進んでおり、かつ、第2カウンタ11において第2エッジが第1基準信号エッジよりも遅れるように、基準信号Vbを補正して、ディレイ部のディレイ素子の遅延時間を調整する出力電流Ib1を出力するディレイ素子調整部と、を備えている。

(もっと読む)

集積回路、表示装置及びそれを用いた電子機器

【課題】DLLに求められる保証動作周波数帯域を低め、基準クロック信号が二逓倍された周波数をそれぞれ有し、位相差のある2つのクロック信号を生成することができる集積回路、表示装置及び電子機器を提供する。

【解決手段】タイミングコントロールICは、一周期Tの基準クロック信号ICLKと同一周波数の第1〜第4のクロック信号CLK1〜CLK4であって、第N(N=1,3のいずれか)のクロック信号に対する第(N+1)のクロック信号の位相遅れが位相差T/4で、かつCLK1に対するCLK3の位相遅れが位相差α(0<α<T/4)であるCLK1〜CLK4のクロック信号を発生させるDLL40と、CLK1が二逓倍されたデータ生成用のCLK5を生成し、かつ、CLK3が二逓倍されて、CLK5に基づき生成されデータ信号に対して位相差αの遅れで同期したCLK6を生成する二逓倍回路50とを有する。

(もっと読む)

クロック生成回路

【課題】

要求されるデューティ比の同期クロック信号を生成できるか否かの判別が正確に行われるクロック生成回路を提供する。

【解決手段】

クロック生成回路100において、外部から入力されてきた外部クロック信号Sextclkを遅延することにより外部クロック信号Sextclkに同期した同期クロック信号Sclkを生成するDLL回路110と、DLL回路110のデューティ比劣化テスト用にパルス幅を変化させたテスト信号Stestを生成するテスト信号生成回路120と、外部クロック信号Sextclkおよびテスト信号Stestのうちの一方の信号を選択してDLL回路110に入力する選択回路130とを備えたことを特徴とする。

(もっと読む)

141 - 160 / 225

[ Back to top ]