Fターム[5J106SS03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 細部の構成 (94) | VCOの具体的回路が示されたもの (22)

Fターム[5J106SS03]に分類される特許

1 - 20 / 22

無線通信装置

【課題】周波数シンセサイザによる周波数信号を用いる無線通信装置の消費電力を低減する。

【解決手段】受信部が、受信した無線信号に基づく信号と周波数信号とを混合する第1ミキサと、当該第1ミキサの出力とローカル信号とを混合する第2ミキサと、当該第2ミキサの出力を復調して復調信号を生成する復調段とを含み、周波数シンセサイザが、制御入力電圧の変動に応じた周波数の周波数信号を生成するVCOと、当該VCOの出力周波数信号を分周して得られた信号と基準クロック信号との位相差に応じた電圧を制御入力電圧とするフィードバック回路と、からなり、当該VCOは、バイアス電流が大となるほど高い周波数で動作可能となる可変周波数発振器であって、当該バイアス電流が当該モード指定に応じて制御される無線通信装置。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

復調器および通信装置

【課題】高精度に復調処理を行う。

【解決手段】復調器30Aの局部発振器70は、変調器10から送信されて注入される変調信号SRFの局部発振周波数に局部発振信号SLOの周波数を同期させ、同期させた局部発振信号SLOをミキサ40に出力する。ミキサ40は、同期した局部発振信号SLOと変調器10から送信される変調信号SRFとを掛け算して復調信号SDMを生成する。このとき、局部発振信号SLOと周波数同期した変調信号SRFとの間の位相差に応じて復調信号SDMにDC成分が発生する。DC補正部50は、復調信号SDMのDC電圧Vdcを検出し、検出したDC電圧Vdcが予め設定されている基準電圧となるように補正する。

(もっと読む)

PLL回路

【課題】PLL回路の不安定状態や位相雑音特性の劣化を回避する。

【解決手段】

発振周波数が電圧制御発振器からのフィードバック信号と外部から入力される基準信号との位相差に応じて制御されるPLL回路において、前記フィードバック信号を分周する分周器と、前記基準信号を逓倍する逓倍器と、前記分周器からの出力信号と前記逓倍器からの出力信号とをミキシングし周波数変換するミキサと、前記ミキサからの出力信号を分周しデジタル分周信号を出力する第一のデジタル分周器と、前記基準信号を分周しデジタル分周信号を出力する第二のデジタル分周器と、前記第一のデジタル分周器からのデジタル分周信号と、前記第二のデジタル分周器からのデジタル分周信号とを、デジタル位相比較する位相比較器と、を備える。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

周波数シンセサイザ装置及びその制御値決定方法

【課題】特性に優れた発振出力を得る。

【解決手段】 発振周波数の粗調整のための第1の可変容量部及び前記発振周波数の微調整のための第2の可変容量部によって前記発振周波数が可変の電圧制御発振器14と、前記第1及び第2の可変容量部を制御して前記電圧制御発振器の発振周波数を所望の周波数にするPLL回路14と、前記粗調整時において前記第2の可変容量部の容量を制御するための制御値を記憶するメモリ13と、を具備したことを特徴とする。

(もっと読む)

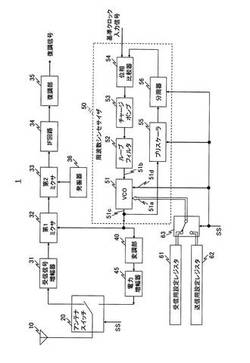

ローカル信号生成回路

【課題】従来のローカル信号生成回路は、回路面積と消費電力が大きくなる問題があった。

【解決手段】本発明にかかるローカル信号生成回路は、基準信号と帰還信号の位相差を検出し、誤差信号を出力する位相比較器21aと、誤差信号を受け昇圧電圧を生成するチャージポンプ回路22aと、昇圧電圧を整形してチューニング電圧Vtuを生成するループフィルタ23aと、チューニング電圧Vtuに基づき所定の周波数を有する第1の出力信号(I_high、Q_high)を生成する電圧制御発振器24aと、第1の出力信号(I_high、Q_high)を所定の周波数に分周した第2の出力信号(I_low、Q_low)として出力すると共に、第1の出力信号(I_high、Q_high)を前記所定の周波数に分周した分周信号を帰還信号を生成する分周器26aに出力するプリスケーラ25aと、を有するものである。

(もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

スペクトラム拡散クロック生成器

【課題】その設計の困難性を低減することができるスペクトラム拡散クロック生成器を提供する。

【解決手段】スペクトラム拡散させたクロック信号CLKOを生成するスペクトラム拡散クロック生成器1において、クロック信号CLKOを所定の分周比で分周して、分周信号を出力する分周器14と、入力される基準クロック信号CLKRと分周信号CLKFの位相差に応じてレベルが変化させた位相差信号Spを出力する位相比較器10と、位相差信号Spに応じた発振制御信号Scを生成する発振制御信号生成器11と、発振部を有し、発振制御信号Scのレベルに応じた電流を発振部に供給して、発振制御信号Scのレベルに応じた発振周波数で発振部を発振させ、クロック信号CLKOを出力する電圧制御発振器12と、発振部に供給する電流を増減させる変調電流Imを生成し、電圧制御発振器12へ供給する変調電流生成器15とを備える。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

フィードフォワード分割器を有する適応帯域幅位相ロックループ

【課題】位相ロックループを提供する。

【解決手段】一部の実施形態では、チップは、第1及び第2の電圧制御式発振器(VCO)出力信号を供給するための第1及び第2のVCOと、第1及び第2VCO出力信号の第1及び第2の周波数を第1及び第2の分周率によって分割するための第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)を含む。チップはまた、第1及び第2分周率を選択するための位相ロックループ制御回路を含む。他の実施形態も説明して特許請求する。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

周波数可変シンセサイザおよび周波数可変発振器

【課題】広帯域の周波数帯で発振可能で、所望の周波数帯域への切替え機能を有する周波数可変シンセサイザを提供する。

【解決手段】負性抵抗を発生する能動素子部3の動作と周波数切替え制御信号とにより可変共振器2で可変の共振周波数で発振した信号を、分周比制御信号により可変分周器8で可変に分周して出力信号端子6Aから出力する。可変共振器2は、1ないし複数のインダクタとキャパシタとスイッチ素子とからなり、スイッチ素子を切替えることにより可変の共振周波数で発振する。可変分周器8は、可変共振器2の共振周波数の(1/i)、(1/2i)、(1/2)iまたはそれらの組み合わせで分周した周波数を出力する。インダクタに厚膜の配線金属層、裏面研磨の基板、基板から浮かした配線層のいずれかを、また、スイッチ素子にMEMSスイッチ、機械的切替え形スイッチ、FETスイッチ、ダイオードスイッチのいずれかを使用する。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)。二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。  (もっと読む)

(もっと読む)

多重周波数源システム及び動作方法

多重周波数源システムが、既定の目標周波数に同調可能な少なくとも1つの周波数源と、目標周波数より高い、又は低い周波数の第2の信号を生成するように動作する少なくとも1つの追加周波数源を含む。同調可能周波数源を、第2の信号の同時生成の間に目標周波数に同調させる方法は、(i)第2の信号の周波数が目標周波数より高いときに、同調可能周波数源を、目標周波数より低い少なくとも1つの周波数点周波数に同調するように制御し、その後、発振器を目標周波数に同調するように制御すること、又は(ii)第2の信号の周波数が目標周波数より低いときに、同調可能周波数源を、目標周波数より高い少なくとも1つの周波数点に同調するように制御し、その後、同調可能周波数源を、目標周波数に同調するように制御することを含む。 (もっと読む)

通信用半導体集積回路

【課題】所定の周波数の局部発振信号を発生する発振器を含むPLL回路を内蔵し、温度が変化してVCOの発振周波数が変動してもPLLループのロックがはずれにくい高周波ICを提供する。

【解決手段】発振周波数帯を切り替え可能なVCO11と可変分周回路12と位相比較回路15とループフィルタ17とを含み、ループフィルタとVCOとの間を切り離した開ループ状態で、複数の所定の固定電圧のいずれかをVCOへ印加する切替えスイッチと、所定の周波数の基準信号に対する可変分周回路の出力の位相の進みまたは遅れを判別する判別回路22と、判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド切り替え回路23とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけ、さらにVCOへ印加する固定電圧を2分探査方式で切り替え最適な印加電圧を見つけPLLループをロックさせる。

(もっと読む)

1 - 20 / 22

[ Back to top ]