Fターム[5J500AA25]の内容

Fターム[5J500AA25]に分類される特許

1 - 20 / 114

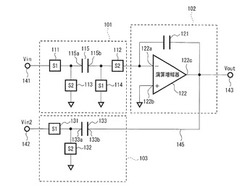

スイッチドキャパシタ積分器

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

電圧電流変換回路および電圧制御発振回路

【課題】入力電圧に正確に対応した値の出力電流を得ることができる電圧電流変換回路およびその電圧電流変換回路で生成した電流を用いて高精度な発振周波数を得ることができるようにした電圧制御発振回路を提供する。

【解決手段】3容量Csと、容量CBと、スイッチSW1〜SW4と、オペアンプOP1と、トランジスタM1,M2とを備え、スイッチSW1,SW2がオン/オフするときスイッチSW3,SW4がオフ/オンするようにスイッチSW1〜SW4を制御し、電圧入力端子1に入力した入力電圧Vinに比例した電流IREFをトランジスタM1のドレインから出力する。

(もっと読む)

スイッチトキャパシター積分回路、フィルター回路、多出力フィルター回路、物理量測定装置、及び電子機器

【課題】低周波数帯域の雑音の影響をより一層小さくすることができるスイッチトキャパシター積分回路等を提供する。

【解決手段】スイッチトキャパシター積分回路10は、第1の容量と第2の容量とを有する電圧電荷変換回路20と、第1の容量に充電された電荷を積分する電荷積分回路30とを含む。電圧電荷変換回路20は、第1の期間において、第1の容量に充電された電荷を転送すると共に入力信号に対応した電荷を第2の容量に充電し、第2の期間において、第2の容量に充電された電荷の一部を第1の容量に充電すると共に入力信号に対応した電荷を第1の容量に充電する。電荷積分回路30は、第3の期間において、演算増幅器の入力に接続されるオフセットキャンセル容量の他端と第1の容量の一端とを接続し、第4の期間において、オフセットキャンセル容量の他端と接地電位とを接続する。

(もっと読む)

サンプルホールド回路

【課題】サンプルホールド機能とマルチプレクサ機能とを具備したサンプルホールド回路を互いに位相が反転した2相信号のみでサンプルホールド機能とマルチプレクサ機能とを提供する。

【解決手段】2つのサンプルホールド回路10,11は、非反転入力端が基準電位に接続された差動増幅器A1,A2と、制御信号φ1に従ってオンオフするスイッチ及びサンプリング容量C1,C3と、制御信号φ1に従ってオンオフするスイッチ及びホールド容量C2,C4と、制御信号φ2に従ってオンオフするスイッチと、を備える。マルチプレクサ回路12は、非反転入力端が基準電位に接続された差動増幅器A3と、制御信号φ1,φ2に従ってオンオフするスイッチと、差動増幅器A3の出力端と反転入力端との間に接続されたホールド容量C5と、を備える。

(もっと読む)

演算回路、及びA/D変換器

【課題】所望の帯域幅を確保しつつ、所望の倍率を正確に得ることができる演算回路を提供する。

【解決手段】演算回路は、入力信号を入力する入力端子と、複数個のキャパシタと、増幅入力端子と出力端子とを備え、この増幅入力端子から入力される信号を増幅して前記出力端子から出力信号を出力する増幅回路とを備えている。第1スイッチ回路は、第1制御信号に基づき導通状態となり、複数のキャパシタを入力端子と第1電圧を供給する第1電圧端子との間に並列に接続する。また、第2スイッチ回路は、第2制御信号に基づき導通状態となり、複数個のキャパシタに含まれる第1のキャパシタを増幅入力端子と第2電圧を供給する第2電圧端子との間に第1の電流経路を形成するように接続すると共に、複数個のキャパシタに含まれる第2のキャパシタを増幅入力端子と前記出力端子との間に第2の電流経路を形成するように接続する。

(もっと読む)

半導体回路

【課題】安定した入出力特性を得られる半導体回路を提供する。特に、スイッチング素子のリーク電流に起因する不具合が抑制された半導体回路を提供する。

【解決手段】スイッチトキャパシタ回路に用いられるスイッチング素子に、酸化物半導体などのワイドギャップ半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタを適用する。このようなトランジスタは、オフ状態におけるリーク電流が小さい特徴を有し、当該トランジスタをスイッチング素子に適用することによりリーク電流に起因する不具合が抑制され、安定した入出力特性が得られる半導体回路を構成することが出来る。

(もっと読む)

液晶駆動用のソースドライバのオフセット低減出力回路

【課題】 出力アンプのオフセット電圧を適切に低減して表示品質の悪化を防止することができる液晶駆動用のソースドライバのオフセット低減出力回路を提供する。

【解決手段】 基準電圧がオペアンプの非反転入力端に印加されたオペアンプと、少なくとも通常出力動作時にオペアンプの反転入力端に接続される第1の接続点に各々の一端が接続された第1の入力コンデンサ及び第1の出力コンデンサと、リセット動作時に第1の入力コンデンサ及び第1の出力コンデンサ各々の両端を短絡してその両端に基準電圧を印加し、リセット動作後の通常出力動作時に第1の入力コンデンサの他端に階調電圧を印加しかつ第1の出力コンデンサの他端をオペアンプの出力端に接続する第1のスイッチ素子回路と、を備え、第1のスイッチ素子回路は、第1の接続点とオペアンプの出力端との間に接続され、リセット動作時にオンとなり、通常出力動作時にオフとなる直列接続の第1及び第2のスイッチ素子を有し、通常出力動作時には第1及び第2のスイッチ素子の直列接続点に基準電圧を印加する。

(もっと読む)

フィルタ回路

【課題】 歪特性に優れるフィルタ回路を得る。

【解決手段】 直列に接続された複数のLPFを有するフィルタ回路において、複数のLPFはそれぞれ、スイッチトキャパシタ回路SC、および、SCの出力信号を増幅して出力する全差動型増幅器AMPを有する。1ビットDAC40の出力信号が入力されるLPF1が有するAMP10のコモンモードフィードバック回路は離散時間型であり、フィルタ回路としての出力信号を出力するLPF2が有するAMP20のコモンモードフィードバック回路は連続時間型である。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】 仮想接地ノードの電位に誤差が生じた場合でも制御性良く動作する低消費電力のスイッチトキャパシタ型積分器を提供する。

【解決手段】 入力信号の電荷をサンプリングするサンプリングキャパシタC1と、サンプリングキャパシタC1の電荷を仮想接地ノード4を介して蓄積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1、MN1と、そのゲート端子と仮想接地ノード4との間に挿入された校正キャパシタC3,C4と、校正キャパシタC3,C4に対して、仮想接地ノード4が基準電位Vcmとなる電位差が生じるように電荷を供給する校正装置12と、仮想接地ノードの電位を増幅した電位を主トランジスタMP1,MN1に出力する増幅器とを備える。

(もっと読む)

電流電圧変換回路、物理量測定装置

【課題】 回路規模の増加を抑えつつ、高い精度の電流電圧変換を行い、低ノイズの電圧信号を出力する電流電圧変換回路等を提供する。

【解決手段】 電流電圧変換回路10であって、電圧信号101P、101Nを出力するオペアンプ20と、入力された電流信号100P、100NのDCオフセット電流に応じた電荷を充放電する第1のキャパシタ40P、40Nと、オペアンプのオフセット電圧に応じた電荷を充放電する第2のキャパシタ41P、41Nと、第1の期間においてオン状態となり第2の期間においてオフ状態となる第1のスイッチ30P、30Nおよび第3のスイッチ32P、32Nと、第1の期間においてオフ状態となり第2の期間においてオン状態となる第2のスイッチ31P、31Nとを含む。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器

【課題】所望の信号伝達関数でより一層の出力雑音成分を低減できるスイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等を提供する。

【解決手段】スイッチと、複数のサンプリング容量と、積分容量とを含んで構成されるスイッチトキャパシター積分回路10は、電荷充電期間T1の入力信号に対応した電荷をサンプリング容量の少なくとも1つに充電する。スイッチトキャパシター積分回路10は、電荷転送期間T2において、該電荷を積分容量に転送することで、該電荷に対応した信号を伝搬遅延させる。スイッチトキャパシター積分回路10は、例えばスイッチにより複数のサンプリング容量の接続を切り換えることにより、電荷充電期間T1にて決定される信号伝達関数と、電荷転送期間T2にて決定される雑音伝達関数とを異ならせる。

(もっと読む)

スイッチドキャパシター回路、検出装置及び電子機器

【課題】負荷電流による電圧ドロップを抑制するスイッチドキャパシター回路、検出装置及び電子機器等を提供すること。

【解決手段】スイッチドキャパシター回路は、出力用の演算増幅器OPBと、スイッチドキャパシター動作を行うための複数のスイッチ素子SB1〜SB8と、スイッチドキャパシター動作を行うための複数のキャパシターCB1,CB2と、スイッチドキャパシター回路の出力端子ノードNTと第1のスイッチ素子SB6との間に設けられる静電保護用の抵抗素子RB1と、を含む。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

スイッチトキャパシタ型回路及びそれを用いたAD変換回路

【課題】消費電力を増大させることなく、高精度な基準電圧の下で動作するスイッチトキャパシタ型回路を提供する。

【解決手段】(1)第1のスイッチトキャパシタ(スイッチ11〜13及び帰還容量Cf)とサンプリング容量Csと増幅回路100とを含むスイッチトキャパシタ型増幅回路110aと、(2)スイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給する基準電圧回路110bとを備え、基準電圧回路110bは、基準電圧Vrefを出力するバッファ回路1と、バッファ回路1の出力端子111とスイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給するための基準電圧入力端子112との間に接続された第2のスイッチトキャパシタ(スイッチ10及び容量Cc)とを有する。

(もっと読む)

抵抗の誤差訂正を用いるコンパレータベースのバッファ

【課題】スイッチトキャパシタの負荷を有する高利得増幅器の駆動容量を高めるコンパレータベースのバッファ方法及びシステムを提供することを目的とする。

【解決手段】電流源と、コンパレータと、スイッチと、サンプリングキャパシタと、オーバーシュート訂正抵抗を含む。充電経路内の抵抗及び訂正位相を使用する訂正の解決法は、電力消費を制約し、コンポーネントを最小化する一方で、出力電圧のオーバーシュートを低減する。Spectre(登録商標)シミュレーションは、本発明の効果を確証する。

(もっと読む)

サンプルホールド回路及びA/D変換装置

【課題】本発明は、サンプルホールド回路及びA/D変換装置に係り、ホールド出力を行ううえでオペアンプの入力オフセット分の除去性能を向上させることにある。

【解決手段】ホールド出力を行うオペアンプを備えるサンプルホールド回路において、所定複数の異なるタイミングで入力電圧をサンプリングするサンプリングキャパシタと、サンプリングキャパシタでサンプリングされた各入力電圧を加減算する加減算手段と、加減算手段により各入力電圧が加減算された後、該加減算により得られる電圧に含まれるオペアンプの入力オフセット電圧分を除去するオフセット電圧除去手段と、を備え、オペアンプは、オフセット電圧除去手段によりオペアンプの入力オフセット電圧分が除去された電圧をホールドして出力する。

(もっと読む)

スイッチトキャパシタアンプ回路

【課題】出力電圧に含まれる直流オフセット成分の増幅分の調整精度を確保しつつ、回路面積の増大を抑制可能な、スイッチトキャパシタアンプ回路の提供。

【解決手段】オペアンプ31の反転入力端子に一端が接続されたキャパシタ21と、反転入力端子に一端が接続されオペアンプ31の出力部に他端が接続されたキャパシタ22と、反転入力端子に一端が接続されたキャパシタ23とを備え、キャパシタ21が、入力電圧Vinに応じた電荷を第1の期間に蓄積し、アナログ電圧VDACに応じた電荷を第2の期間に蓄積するものであり、キャパシタ22が、第2の期間に蓄積した電荷を第1の期間に放出するものであり、キャパシタ23が、アナログ電圧VDACに応じた電荷を第1の期間に蓄積し、第1の期間に蓄積した電荷を第2の期間に放出するものであり、キャパシタ23の容量C3がキャパシタ21の容量C1よりも小さい、スイッチトキャパシタアンプ回路。

(もっと読む)

スイッチドキャパシタ利得段

【課題】出力電流を増やすことなくセトリング時間を短縮することが可能なスイッチドキャパシタ利得段、及び、これを用いたパイプライン型A/D変換器を提供する。

【解決手段】スイッチドキャパシタ利得段は、第1フェーズではサンプル/ホールド回路(キャパシタCf及びCs、並びに、スイッチSWa〜SWc)を用いて入力電圧Vinのサンプリングを行い、第2フェーズでは増幅器(AMP1及びAMP2)を用いてサンプリング済み入力電圧の増幅出力を行うスイッチドキャパシタ利得段において、入力電圧Vinのサンプリング動作時にのみ、前記増幅器のミラー補償を行うミラー補償部(Cm、SWg)を有する構成とする。

(もっと読む)

1 - 20 / 114

[ Back to top ]