Fターム[5J500AF10]の内容

Fターム[5J500AF10]に分類される特許

1 - 20 / 1,318

無線基地局装置及び無線基地局装置の送信増幅器消費電力制御方法

増幅器

スイッチングアンプ

スイッチングアンプの制御回路

パルス幅変調回路およびスイッチングアンプ

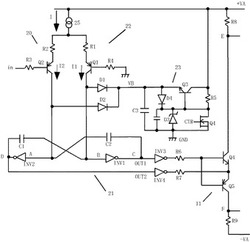

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

調整装置、通信装置の調整方法、プログラムおよび記録媒体

【課題】製造バラツキに関わらず、通信装置の電力効率を改善することができる調整装置を実現する。

【解決手段】本発明に係る調整装置1は、通信装置2のACLRを測定する測定装置11と、ワースト条件下での規定限界出力におけるACLRが許容値以下となる電源電圧を算出するVcc演算部123と、算出された電源電圧をDCDCコンバータ25の生成する電源電圧Vccの上限値として設定するテーブル更新部124とを備える。

(もっと読む)

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

増幅回路

【課題】ノイズフィギュアの劣化を抑制しつつ、過入力信号を調整可能な上限電圧および下限電圧の範囲内に制限する。

【解決手段】入力トランジスタと、第1端が前記入力トランジスタのゲートに接続され、第2端がバイアス電圧に接続される抵抗素子と、前記入力トランジスタのゲートに接続され、前記入力トランジスタのゲートへの入力を、前記バイアス電圧を基準とする(調整可能な)上限電圧および下限電圧の範囲内に制限する保護回路と、を備える、増幅回路。

(もっと読む)

増幅回路及び無線通信装置

【課題】NFを増大させること無く、CMOS LNA回路の非動作時に、CMOS LNA回路に電流を流さないような構成とすることが可能な、増幅回路を提供する。

【解決手段】ゲート電極に、受信された無線信号を入力する信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された入力トランジスタと、信号入力端子と入力トランジスタのゲート電極との間に設けられる第1スイッチと、電源端子と入力トランジスタのドレイン電極との間に設けられる第2スイッチと、を備え、入力トランジスタのゲート電極には所定のバイアス電圧が印加され、無線信号の受信時には、第1スイッチと第2スイッチとを同時にオンにして、無線信号の送信時には、所定のバイアス電圧を入力トランジスタのゲート電極に印加したまま、第1スイッチと第2スイッチとを同時にオフにすることを特徴とする、増幅回路が提供される。

(もっと読む)

電力増幅器

【課題】本実施例の一側面における電力増幅器はトランジスタの入力側と出力側の両方に高調波処理を行う整合回路を設けた場合でも発振が生じるのを抑止し、電力増幅器の安定動作を可能とすることを目的とする。

【解決手段】本実施例の一側面における電力増幅器は、基本波と高調波を含む入力信号を入力ノードで受けとり、入力信号の電力を増幅することにより出力信号を生成し、生成された出力信号を出力ノードから出力する増幅回路と、増幅回路の入力ノードに接続され、入力信号の高調波処理を行う入力整合回路と、増幅回路の出力ノードに接続され、出力信号の高調波処理を行う出力整合回路を含む。増幅回路は、入力信号の電力が所定値より大きい値からその所定値より小さい値に低下したとき、生成される出力信号に含まれる高調波の整合点における出力インピーダンスの位相を回転させる。

(もっと読む)

電力増幅器

【課題】広帯域に亘って高出力電力で高効率な電力増幅器を提供する。

【解決手段】電源電圧がVdc、増幅素子の従属電流源の最大電流がImax、流通角がθo、前記従属電流源から見た第n調波の負荷インピーダンスがZn=Rn+j・Xn(n=1, 2, 3,…)である電力増幅器において、

各抵抗値の関係が、Σn=1N Rn・[sin{(n−1)・θo/2}/{n・(n−1)}−sin{(n+1)・θo/2}/{n・(n+1)}]/[π・{1−cos(θo/2)}]=Vdc/Imax、各リアクタンス値の関係が、Σn=1N Xn・n・[sin{(n−1)・θo/2}/{n・(n−1)}−sin{(n+1)・θo/2}/{n・(n+1)}]/[π・{1−cos(θo/2)}]=0(Nは3以上の任意の整数)、かつ前記従属電流源の電圧の最小値が零である。

(もっと読む)

送信増幅器

【課題】低ひずみ、低雑音、且つ小形な送信増幅器を得る。

【解決手段】多段接続した増幅器のうちの少なくとも1段以上に、バイポーラトランジスタ3のコレクタ電極とベース電極との間に接続された抵抗9を備え、出力電源10からインダクタ8および抵抗9を介してバイポーラトランジスタ3のベース電極に入力バイアスを供給する増幅器を備える。

バイポーラトランジスタ3の動作条件を決める入力バイアスを、抵抗9と出力電源10とにより決定するので、バイアス回路によるひずみがバイポーラトランジスタ3に重畳されないため、低雑音な送信増幅器を実現することができる。

また、入力バイアスを供給するためだけにインダクタを設ける必要がないため、小形な送信増幅器を実現することができる。

(もっと読む)

高周波増幅回路及びそれを用いた移動体通信端末

【課題】バイアス電流の制御電圧の設定範囲を拡大させつつ、バイアス回路の構成の自由度を向上させ、簡単かつ小規模な構成で複数の通信方式への対応を実現する高周波増幅回路を提供する。

【解決手段】バイアス回路32を、入力されるベース電流に応じたバイアス電流を増幅器11に供給するトランジスタQ5、基準電圧Vrefに応じた電流を流すトランジスタQ3、トランジスタQ3に流れる電流に応じてトランジスタQ5のベース電流を補正することによりトランジスタQ5の温度特性を補償するトランジスタQ2、及びトランジスタQ5のベースに接続され制御電圧Vccの切り替えに応じてトランジスタQ5のベース電流量を切り替えるバイアス切り替え部(トランジスタQ4、Q6、及び抵抗R5〜R7、R9、R10)で構成する。増幅器11は、バイアス回路32から供給されるバイアス電流を用いて、入力される高周波信号を増幅する。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

電力増幅器における動的バイアス制御

【課題】平均電力効率(APE)が改良されることができるセルラ電話における電力増幅器を提供する。

【解決手段】RF出力電力増幅器(PA)は、第1および第2のAB級増幅回路を含んでいる。高電力オペレーティングモードにおいて動作する場合、第1の増幅器はPA出力端子を駆動する。第1の増幅器のパワートランジスタ(単数または複数)は、高い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。低電力オペレーティングモードにおいて動作する場合、第2の増幅器は出力端子を駆動する。第2の増幅器のパワートランジスタは、低い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。増幅器のパワートランジスタを適切にサイジングすることによって、エミッタ電流密度は、実質的に等しく維持されるので、PA電力利得は、2つのオペレーティングモードにおいて同じである。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の利得の温度依存性を抑制し、温度補償回路を有するバイアス回路を備えた電力増幅回路を提供する。

【解決手段】ドレインが高電位に接続され、ソースが接地された増幅用トランジスタを備え、ソースが接地され増幅用トランジスタGTrのゲートにゲートが接続されたカレントミラートランジスタCMTrによって増幅用トランジスタのバイアス電流を制御する電力増幅回路であって、アノードが制御電源端子に接続された第1のダイオードD1と、アノードが第1のダイオードD1のカソードに結合され、カソードがカレントミラートランジスタCMTrのドレインに接続された第2のダイオードD2と、一方の端子が第2のダイオードD2のカソードに接続され他方の端子が接地された第1の抵抗素子R1と、第2のダイオードD2と並列接続された第2の抵抗素子R2とを備える。

(もっと読む)

オーディオ機器の出力回路とその制御方法、及びそれを備えた電子機器

【課題】外部の負荷とDCカット容量とで決まる時定数が長くなるケースにおいてもポップ音を発生させないオーディオ機器の出力回路とその制御方法及びそれを備えたオーディオ機器を提供する。

【解決手段】出力アンプ1を備えたオーディオ機器の出力回路において、前記出力アンプ1の接地レベルへの遷移終了後に、前記出力アンプ1の出力端子1aを接地に短絡するスイッチ素子をさらに備える。ここで、前記スイッチ素子を前記出力アンプ1のNチャネルドライバトランジスタ5により代用した。

(もっと読む)

バイアス回路およびそれを有するアンプ回路

【課題】増幅トランジスタのトランスコンダクタンスgmの変動を抑制する。

【解決手段】バイアス回路は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有する。そして,抵抗回路の第1のノードの第1の電圧が第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が第2のトランジスタのゲートに印加され,第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

1 - 20 / 1,318

[ Back to top ]