Fターム[5J500AF19]の内容

Fターム[5J500AF19]に分類される特許

161 - 180 / 223

Dクラスアンプ

【目的】貫通電流低減回路を備えるDクラスアンプを提供する。

【構成】Dクラスアンプ10は、プシュプル型出力段スイッチングトランジスタQ1,Q2を備えるパルス変調出力のアンプであり、入力されるオーディオ信号の無信号入力状態、PCM信号などのデジタル信号のゼロ入力状態、または出力ボリューム位置のゼロレベル状態である無信号入力状態を検出する無信号入力状態検出手段7と、この無信号入力状態検出手段7で前記無信号入力状態を検出している場合にプシュプル型出力段スイッチングトランジスタQ1,Q2のデッドタイムDTが通常よりも大きくなるように自動的に出力段ドライバ回路2の出力のスイッチング信号SH,SLを制御するデッドタイム制御手段8と、を有してなる貫通電流低減回路9を備える構成であり、無信号入力時の貫通電流を低減して発熱を抑え、消費電力のロスを低減する。

(もっと読む)

アナログ入力信号処理回路

【課題】入力フィルタ特性と入力ゲインを個別に調整可能なアナログ入力信号処理回路を提供する。

【解決手段】可変アナログ信号源100a・100bが発生する信号電圧は、ゲイン調整回路10a・10bとスイッチドキャパシタフィルタ回路20a・20bとアナログ比較回路30a・30bを介してマイクロプロセッサ110に入力される。プログラムメモリ111と協働するマイクロプロセッサ110は、可変周期・可変デューティの制御信号パルス列CNTa・CNTbを発生し、該制御信号パルス列CNTa・CNTbの周期によりフィルタ特性が調整され、パルスデューティによってゲインが調整される。アナログ比較回路30a・30bの比較基準電圧31a・31bが固定値であっても、ゲイン調整回路10a・10bのゲインを調整することにより見かけ上の比較基準電圧の変更調整が行える。

(もっと読む)

信号加算回路

【課題】 I信号とQ信号に位相誤差や振幅誤差が含まれていてもこれらの影響を排除して加算できるようにした信号加算回路を提供する。

【解決手段】 少なくともグランドとの間が定電流状態にある接地端子21s,22sと位相の異なる入力信号(I信号,Q信号)が入力される入力端子21g,22gと互いに接続された出力端子21d,22dを介して電源電圧Vccが印加された一対の増幅素子21,22からなる加算部20Aと、前記増幅素子21,22の各接地端子21s,22sと前記グランドとの間に前記異なる入力信号間の振幅を調整するゲインコントロール部30と、位相を調整する位相コントロール部40を設けた。

(もっと読む)

高効率増幅器

【課題】 両経路の出力信号が合成する際に合成損失が発生せず高効率を実現する。

【解決手段】 入力信号を2つの経路に分配する入力分配回路2と、一方の経路に接続されたキャリア増幅器3及び90°の電気長を有するインピーダンス変換線路4と、他方の経路に接続された位相線路21及びピーク増幅器6と、両経路の出力合成点11に接続された90°位相線路とを備え、位相線路21の電気長φは、キャリア増幅器3の電気長θCA及びインピーダンス変換線路4の電気長90°の和と、位相線路21の電気長φ及びピーク増幅器6の電気長θPAの和が一致するように設定される。

(もっと読む)

負帰還増幅装置及び負帰還増幅伝送システム

【課題】伝送帯域幅の変化や環境変動に対して安定で歪の少ない負帰還増幅装置を提供すること。

【解決手段】入力信号を搬送波信号で変調する変調手段3と、変調手段で変調された変調信号を増幅する増幅手段4と、増幅手段の出力信号を復調する復調手段5と、被変調信号から復調手段の出力信号を減算して差信号を出力する減算手段6と、差信号の帯域制限を行い帰還信号を出力する、カットオフ周波数が可変のフィルタ手段7と、被変調信号に帰還信号を加算して変調手段に入力する加算手段2と、差信号の振幅に応じてフィルタ手段のカットオフ周波数を制御するフィルタ係数制御手段10とを備え、フィルタ係数制御手段がループフィルタのカットオフ周波数を変化させることができる。

(もっと読む)

電力増幅器およびそれを用いた送信機

【課題】 ドハーティ型電力増幅器の出力電力合成回路の電気長を可変にし、マルチバンドまたは広帯域に対して高電力付加効率を図る。

【解決手段】 キャリアアンプAmp1とピークアンプAmp2との入力側に、90度位相遅延電力分配部PSPDを接続し、出力側に可変電気長電力合成部VTL2を接続する。搬送波信号RFsの搬送波周波数帯域に応じて、その搬送波周波数帯域の中心周波数に対して可変電気長電力合成部VTL2の電気長がほぼ90度になるように、可変電気長電力合成部VTL2の制御端子Ctrlから制御信号Sigを印加することにより調整する。

(もっと読む)

2段のマイクロ波のE級電力増幅器

スイッチングモード回路50と共に使用する負荷回路40である。本発明の負荷回路40はスイッチングモード回路50の出力に結合されている直列の誘導性−容量性ネットワーク32、34と、スイッチングモード回路50の出力に結合されているキャパシタンスを提供するための回路42を含んでいる。例示的な実施形態では、キャパシタンスを提供するための回路42はスイッチングモード回路50中の固有のキャパシタンスを補償するように構成されている1以上の集中定数キャパシタを含んでいる。負荷回路40はスイッチングモード回路の出力に結合されているシャントインダクタンスを含むこともできる。例示的な実施形態では、負荷回路40はE級の負荷を2段のE級の高電力増幅器100に提供するように構成されている。増幅器100は駆動装置段102、本発明のE級段間整合ネットワーク(ISMN)104、優秀な負荷回路40を使用する高電力段106を含んでいる。 (もっと読む)

帯域選択型フィードフォワード増幅器

【課題】本発明の目的は、複数の無線システムが混在する環境で、周波数帯を適応的に選択できるフィードフォワード増幅器を提供することである。

【解決手段】本発明のフィードフォワード増幅器は、歪検出回路と歪除去回路を備え、歪検出回路の第1ベクトル調整経路14に挿入される動作周波数帯が異なるn個の第1ベクトル調整器4と、歪除去回路の第2ベクトル調整経路8に挿入される周波数帯が第1ベクトル調整器4と対応するn個の第2ベクトル調整器11を有する。1つの第1ベクトル調整器4を選択する第1切替手段3と、第2ベクトル調整器11を選択する第2切替手段10により、フィードフォワード増幅器で歪成分を補償する周波数帯を切替制御する。

(もっと読む)

ゼロ交差検出を用いたサンプル値回路

【課題】仮想接地ノードを適切なレベルに維持すること等ができるサンプル値回路を提供すること。

【解決手段】サンプル値アナログ回路はレベル交差検出手段(30)を含む。レベル交差検出手段はサンプリングスイッチ(s22n、s23n、s22p、s23p)を制御して、入力信号が所定レベルと交差したことがレベル交差検出手段により検出された際に、出力電圧の正確なサンプルを供給する。レベル交差検出はゼロ交差検出であり得る。任意の同相帰還回路(400)により、出力同相電圧を略一定に保つことができる。

(もっと読む)

増幅器

【課題】 従来のドハティ増幅器では、最適な整合がとれずに増幅効率が向上せず、また、周波数帯域を広くできないという問題点があったが、本発明は、増幅効率を向上させ、広い周波数帯域での使用を可能とする増幅器を提供する。

【解決手段】 AB級で動作する第1の増幅回路と、B級又はC級で動作する第2の増幅回路と、第1の増幅回路の出力と第2の増幅回路の出力をλ/4以外の電気長の伝送線路から成るインピーダンス変換器を介して合成する合成点とを備え、インピーダンス変換器が、それぞれ電気長の異なる複数の伝送線路を有し、入力信号の周波数に応じていずれかの伝送線路に接続を切り替え可能である増幅器としている。

(もっと読む)

スタガ出力を伴う多重チャネルパルス幅変調音響を提供するシステム及び装置

異なるチャネルにおけるパルス幅変調のタイミングをスタガさせることによって多数チャネルデジタル音響システムのノイズレベルを低減し、これによって、発生するスイッチングノイズの大きさを減らし、スイッチングノイズの周波数特性を上げるシステム及び方法。一の実施例は、複数チャネルデジタルPWM増幅チャネルをそなえ、各チャネルの変調器で用いられるタイミング信号を発生したPWM信号のスイッチングエッジに均等にスペースを空けるようにスタガする。更に、各チャネルに相補的遅延が実装され、各チャネルの全体遅延を均一にし、チャネルの出力を同期させる。別々のチャネルが別々のチップに実装することができ、この場合、各チャネルで処理する信号をスタガする前にチップを同期させるようにしてもよい。  (もっと読む)

(もっと読む)

アダプティブプリディストーション増幅回路

【課題】 増幅器にアダプティブディジタルプリディストーション(ADPD)を用いる際、ループ内時間を測定して、これにあわせて回路を調整する必要がある。そのために回路内の遅れ時間を測定する装置が必要であり、その付加回路の為に機器小型化が難しいという課題があった。

【解決手段】 ADPDループ内に基準信号発生手段18を設け、この信号を増幅器のループ内に巡回させる。遅延時間を測定すべき回路の入り口の基準点Aを信号が通過し始めた時点から、回路の出口の基準点Bに信号が至る間、カウント部21により信号のサイクル数をカウントする。また、時間を正確に計測するため、基準点A,Bの信号の位相差を位相判定部24により計測する。カウント数と位相差に基づいて回路の遅れ時間を演算し、帰還信号の遅れと参照信号の遅延量とを同じになるように調整する遅延時間調整部22を設ける。

(もっと読む)

高周波電力増幅装置

【課題】ドハティ機能を機構的にサイズが大きくなる伝送線路を用いずに実現することができ、ドハティ機能を備える増幅装置のサイズをさらに小型化して、機構的に容積の縮小化が要求される移動体通信機器にもドハティ機能を実装することができる高周波電力増幅装置を提供する。

【解決手段】キャリア増幅器102とピーク増幅器103をそれぞれトランジスタによる多段構成として、各増幅器102、103が90度の位相差で動作するように設計することにより、ドハティ機能を実現する場合に従来ピーク増幅器の入力側に用いていた1/4波長ネットワークを不要とする。

(もっと読む)

極座標変調回路、集積回路および無線装置

【課題】補償精度を確保しながら、メモリに格納するデータ容量を低減するとともに、歪補償に係る回路規模の増大を抑制することが可能な極座標変調回路を提供する。

【解決手段】増幅器の歪補償のもととなる、入力高周波信号の所定入力振幅における、制御電圧入力後の定常状態での制御電圧に対する出力信号特性を、所定の直流オフセット電圧を加算するためのデータを格納するオフセット記憶部101aと所定の係数を乗算するためのデータを格納する係数記憶部102に分割して記憶することで、補償精度を確保しながら、歪補償に係る回路規模を低減することができる。

(もっと読む)

増幅器

【課題】従来のドハティ増幅器を超えた高電力効率および低出力歪である増幅器を提供する。

【解決手段】本発明に係る増幅器は、複数の増幅回路の出力を合成して出力とする増幅器において、複数の増幅回路のうち、増幅素子をAB級で動作させる第1の増幅回路と、複数の増幅回路のうち、増幅素子をB級またはC級で動作させる第2の増幅回路と、第1の増幅回路の出力に接続されるλ/4以外の電気長を有する第1の伝送線路と、第2の増幅回路の出力に接続される任意の電気長を有する第2の伝送線路と、第1の伝送線路の出力と第2の伝送線路の出力とを合成する合成端と、を備える。更に、第1の伝送線路若しくは第2の伝送線路の少なくとも一方が、位相器を有する。更に、第1の増幅回路は、AB級で動作する第1のプリアンプを有し、第2の増幅回路は、A級からC級のいずれかを動作点とする第2のプリアンプを有する。

(もっと読む)

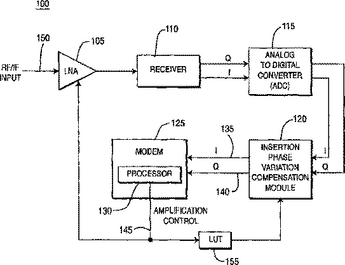

増幅器の位相オフセットを補償する方法およびシステム

増幅器(105)、受信機(110)、アナログ−デジタルコンバータ(ADC115)、および挿入位相変動補償モジュール(120)を含む通信システムを提供する。増幅器は、通信信号(150)を受信する。増幅器は、動作可能にされると、通信信号を増幅し、増幅した通信信号を受信機に出力する。増幅器は、動作不能にされると、通信信号を増幅せずに受信機に渡す。受信機は、ADCにアナログ複合信号を出力する。ADCは、デジタル複合信号を挿入位相変動補償モジュールに出力し、補償モジュールは、増幅器が動作可能にされ、または動作不能にされるときに通信信号に断続的に導入される位相オフセットの影響を打ち消す。  (もっと読む)

(もっと読む)

ゲートドライブ回路

【課題】主スイッチング素子を駆動するためのP型MOSFETおよびN型MOSFETが同時に導通してしまうおそれを排除する。

【解決手段】主スイッチング素子を駆動するためのP型MOSFETQ1及びN型MOSFETQ2の一方がONされ、他方がOFFされている時に主スイッチング素子をONし、一方がOFFされ、他方がONされている時に主スイッチング素子をOFFするゲートドライブ回路において、一方がOFFからONに切り換えられ、他方がONからOFFに切り換えられる場合に、一方がOFFからONに切り換えられる瞬間よりも先に他方をONからOFFに切り換え、一方がONからOFFに切り換えられ、他方がOFFからONに切り換えられる場合に、他方がOFFからONに切り換えられる瞬間よりも先に一方をONからOFFに切り換える。

(もっと読む)

高出力効率の集積ドハティ型増幅装置

本発明は、集積ドハティ型増幅装置及びそのような装置のための増幅方法であって、所定の位相シフトで且つ不均等分配率でメイン及びピーク増幅器段(20、30、40)の入力信号を分配するために集中素子ハイブリッド電力分配器(12)が設けられるとともに、第1の増幅信号を受信し且つ所定の位相シフトを第1の増幅信号及びその更に高い高調波に対して適用するために、広帯域補償回路と組み合わせられる少なくとも一つの広帯域集中素子擬似ライン(Z1、Z2)が設けられる、集積ドハティ型増幅装置及びそのような装置のための増幅方法に関する。これにより、ピーク増幅器の低い利得は、入力において不均等電力分配を行うことによって補償される。また、集中素子ハイブリッド電力分配器を使用することにより、メイン及びピーク増幅器の入力ポート間の絶縁が向上し、それにより、出力信号の最終的な歪みが低減される。  (もっと読む)

(もっと読む)

電力増幅器負荷切り替えのための動的利得及び位相補償

無線周波数(RF)送信器(108)において利得及び位相補償する方法及び装置が提供される。RF送信器(108)は、自身から信号電力を有する送信される信号を与える少なくとも1つの電力増幅器(PA)(205)を有する。RF電力検出器(208)は、少なくとも1つのPA(205)に結合されて、送信される信号の信号電力を検出する。アナログ/デジタル(A/D)変換器(210)が、RF電力検出器(208)に結合される。ヒステリシス・ユニット(214)が、A/D変換器(210)に結合され、或る電力スレッショルドを横切ることに応答して、パルス(222)を発生する。負荷スイッチ制御ユニット(218,232)が、ヒステリシス・ユニット及び少なくとも1つの電力増幅器に結合され、上記パルスに応答して利得及び位相補償を与える。  (もっと読む)

(もっと読む)

高周波増幅回路

【課題】簡単な回路構成で高周波増幅回路の歪み特性を向上させる。

【解決手段】高周波信号対S1(t),S2(t)の平均電力レベルが増幅器14−1,14−2の飽和出力レベル及び利得に基づく設定レベル以下になるように、可変移相器50−1,50−2による同相信号対Sp(t)/20.5の各々の移相量を制御する。この制御によって、出力高周波信号Sout(t)の振幅抑圧量を減少させることができる。その際には、同相信号対Sp(t)/20.5の移相量の制御に高い応答性を必要とせず、制御回路の複雑化やコスト高を招くことはない。

(もっと読む)

161 - 180 / 223

[ Back to top ]