Fターム[5J500AH16]の内容

Fターム[5J500AH16]に分類される特許

1 - 20 / 20

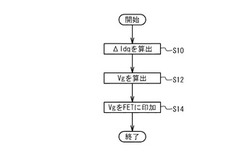

電子回路およびその制御方法

【課題】ドレインアイドル電流のドリフトを直接補償すること。

【解決手段】入力信号が入力するゲートと、出力信号が出力するドレインとを有するFETを含む電子回路の制御方法であって、前記FETのゲートに前記入力信号が入力してからの時間t経過後における前記入力信号x(t)に対応するドレインアイドル電流の変化量ΔIdq(t)を算出するステップS10と、前記変化量ΔIdq(t)を補償するためのゲートバイアス電圧Vgを算出するステップS12と、前記ゲートバイアス電圧を前記FETのゲートに印加するステップS14と、を含むことを特徴とする電子回路の制御方法。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

半導体装置及びその駆動方法

【課題】2つの電位の誤差を増幅して出力する半導体装置におけるスタンバイ状態からの復帰に際して生じる動作遅延を抑制する。

【解決手段】チャネルが酸化物半導体層に形成されるトランジスタによって、トランスコンダクタンスアンプの出力端子とキャパシタの一方の電極の電気的な接続を制御する。よって、トランスコンダクタンスアンプがスタンバイ状態となる場合であっても、当該トランジスタをオフ状態とすることでキャパシタの一方の電極において長期に渡って電荷の保持を行うことが可能となる。また、トランスコンダクタンスアンプをスタンバイ状態から復帰する際には、当該トランジスタをオン状態とすることで、キャパシタの充放電を早期に収束させることができる。これにより、早期に当該半導体装置の動作を定常状態とすることが可能となる。

(もっと読む)

差動信号発生回路および電圧制御ゲイン可変増幅器

【課題】電圧制御によりゲイン調整を行うゲイン可変増幅器制御用の制御電圧を、基準電圧を用いることなく生成し、電圧制御ゲイン可変増幅器全体の小型化および消費電力の削減を図る。

【解決手段】ゲイン可変増幅器制御回路を構成する差動対として、nチャネル型トランジスタTR11とpチャネル型トランジスタTR12とを用い、共通のゲイン制御電圧S1をこれらトランジスタTR11およびTR12のゲートに供給する。各トランジスタTR11、TR12を流れる電流は、ゲイン制御電圧S1が増加するにつれて一方は増加し、他方は減少する特性となり、基準電圧を用いたゲイン可変増幅器制御回路と同一特性のゲイン可変増幅器制御電圧を得ることができる。よって、基準電圧発生回路を設ける必要がないため、装置全体の小型化および消費電力の削減を図ることができる。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発生することのない接合形電界トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FETの封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できるので、定常状態での外部要因によるゲート電位の変動の影響を低減できる。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

ソースフォロア増幅器

【課題】 入力電圧レベルに関わらず、ソースフォロアトランジスタの閾値電圧を一定に保つことができるソースフォロア増幅器を提供すること。

【解決手段】 入力MOSFETの基板ノードと出力ノードとの間を、入力電位に関わらず、非零の一定電圧に保つ手段を有するソースフォロア増幅器において、上記手段は、入力MOSFETの出力ノードと第1の参照電圧源との間に設けられた第1のスイッチ素子と、該入力MOSFETの基板ノードと第2の参照電圧源との間に設けられた第2のスイッチ素子と、該入力MOSFETの基板ノードと出力ノードとの間に設けられた容量素子であって、入力MOSFETの動作時間の内の、校正時間には該第1及び第2のスイッチ素子を短絡し、使用時間には該第1及び第2のスイッチ素子を開放することを特徴とするソースフォロア増幅器。

(もっと読む)

増幅回路及びその増幅回路を含む送信回路

【課題】パワーアンプに含まれる信号増幅用のNMOSトランジスタのゲート・ソース間容量の変化を抑制し、隣接チャネル漏洩比率(ACPR)が改善されたパワーアンプを提供する。

【解決手段】第1相補信号を増幅して得た、第2相補信号を出力する第1増幅器と、前記第2相補信号を増幅して得た、第3相補信号を出力する第2増幅器と、前記第1相補信号と前記第3相補信号との位相差を検出し、前記第2相補信号の電圧に応じて、前記第2相補信号が伝搬する信号線に付加する容量の電圧依存性を、前記位相差が最小となるように制御する容量補正回路と、を備えることを特徴とする増幅回路が提供される。

(もっと読む)

スイッチング回路、分布定数型のスイッチング回路、及び包絡線信号増幅器

【課題】単一のスイッチング素子でインンダクタンス素子をスイッチングすることにより、半導体材料がシリコン又はガリウム砒素からなるスイッチング素子を用いたプッシュプルの増幅器よりも高周波且つ大電力の増幅が可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】スイッチング回路33aは、炭化珪素(SiC)を半導体材料とするn個のトランジスタ(FET)M1,M2,・・MnのゲートをコイルL1を介して縦続接続する入力側伝送線路と、各トランジスタM1,M2,・・MnのドレインをコイルL2を介して縦続接続する出力側伝送線路とを備える。入力端331から与えられて入力側伝送線路を伝播するPWM信号によってトランジスタMm(mは1からnまでの整数)を順次オンさせ、トランジスタMmのドレインに流入する電流と、出力側伝送線路を出力端332の方向に伝播する電流とを加算する。

(もっと読む)

アナログ回路及び半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることを課題の一つとする。

【解決手段】チャネル形成層としての機能を有し、水素濃度が5×1019(atoms/cm3)以下であり、電界が発生していない状態においては、実質的に絶縁体として機能する酸化物半導体を有する薄膜トランジスタを用いてアナログ回路を構成することで、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることができる。

(もっと読む)

線形化回路及び電力増幅のための方法

本発明の線形化回路は、電力増幅器コアを有する電力増幅回路に関連して使用する。例示的な線形化回路は、電力増幅器コアのレプリカを備える。線形化回路はその動作にあたり、RF信号からエンベロープ信号を生成する。このエンベロープ信号を使用して、レプリカを制御することによりアナログ出力信号を生成し、このアナログ出力信号は、電力増幅器コアにおけるAM‐AM変換歪みの反転を表す。その後、線形化回路は、レプリカにおける反転した非線形信号でRF信号をバイアスし、電力増幅コアを制御する。電力増幅器コア及びそのレプリカは、いずれも同一半導体のダイ上に配置することができるため、双方ともに、製造プロセス変動に対して同様の応答を示す。 (もっと読む)

差動増幅器回路、並びに、それを用いたデータ線ドライバ及び液晶表示装置

【課題】液晶表示パネルを駆動するデータ線ドライバの差動増幅器回路に望ましい振幅差偏差特性を実現する。

【解決手段】差動増幅器回路1が、正転入力端子9及び反転入力端子10にそれぞれに接続された一対のノンドープ型NMOSトランジスタMN1、MN2で構成されたNMOSトランジスタ対2と、正転入力端子9及び反転入力端子10にそれぞれに接続された一対のPMOSトランジスタMP1、MP2で構成されたPMOSトランジスタ対3と、ノンドープ型NMOSトランジスタMN1、MN2のドレインに接続されたフォールディッドカスコード型のカレントミラー4を含み、且つ、ノンドープ型NMOSトランジスタMN1、MN2及びPMOSトランジスタMP1、MP2を流れる電流に応答して出力電圧VOUTを生成する出力回路部(4、5、6、MP8、MN8)とを備えている。

(もっと読む)

差動増幅回路

【課題】回路規模の大型化を抑えながら、駆動用電圧の上昇に伴う消費電流の増大を抑制すると共に駆動用電圧の下降に伴う印加電圧不足を解消することができる差動増幅回路を提供する。

【解決手段】NMOSトランジスタ16のドレイン端子及びソース端子間を流れる電流の大きさを予め定められた大きさにする電圧Vref0がNMOSトランジスタ16のゲート端子に印加されるように、閾値電圧が異なるNMOSトランジスタ26,28が並列接続されると共にNMOSトランジスタ26,28の各ドレイン端子の共通接続点に駆動用電圧Vccが印加され、共通接続点Fと負荷との接続点GがNMOSトランジスタ16のゲート端子に接続された。

(もっと読む)

MOSFET及びデュアルゲートJFETを含む電子回路

信号増幅を含む種々の用途のための電子回路及び方法が提供される。模範的な電子回路はカスコード構成にされたMOSFET及びデュアルゲートJFETを備える。デュアルゲートJFETはチャネルの上及び下に配置されたトップ及びボトムゲートを含む。JFETのトップゲートはMOSFETのゲートを制御する信号に依存する信号で制御される。JFETのボトムゲートはトップゲートに依存して又は独立して制御することができる。MOSFET及びJFETは同じ基板上に個別の構成要素として、異なる寸法、例えばゲート幅で実装することができる。  (もっと読む)

(もっと読む)

基準回路

【課題】電源・温度の変動に対する感度を極めて低めた効率的に設計することが可能な基準回路の提供。

【解決手段】pMOS M6とpMOS M7とからなりpMOS M6,M7のソースが電源ノードに接続された第1電流ミラー回路と、pMOS M9とpMOS M8とからなり、pMOS M6,M7のドレイン側にカスコード接続された第2電流ミラー回路と、ソースが電源に接続されゲートがpMOS M6のゲートに接続されたpMOS M5と、飽和領域のnMOS M1及び三極管領域のnMOS M2,M3とを備え、M1,M2,M3はM5のドレインから接地にかけて直列に接続され、各々のゲートはM5のドレインに共通に接続されており、M8のソースはM1のソース及びM2のドレインとの共通接続ノードに接続されており、M9のソースは、M2のソース及びM3のドレインとの共通接続ノードに接続された構成とした。

(もっと読む)

静電誘導トランジスタを用いたパワーアンプ回路のバイアス電流設定回路

【課題】本発明の課題は、パワーアンプ、特に静電誘導トランジスタを最終段に用いたオーディオ用パワーアンプの最終段のトランジスタに流れる無信号時の電流(アイドリング電流)の電源電圧変動依存性を抑制するバイアス回路を提供することである。

【解決手段】本発明による静電誘導トランジスタを用いたパワーアンプ回路のバイアス電流設定回路では、電源電圧自体に比例した電圧を得る回路と、この比例電圧の一部を可変抵抗器で取り出し、この電圧で出力トランジスタのゲート・ソース間に接続したバイアス抵抗に流れる電流を決める回路を構成することで、電源電圧変動及びばらつきの影響を抑制したアイドリング電流を与えるようにしたバイアス電流設定回路となっている。

(もっと読む)

化合物半導体装置及びそれを用いたドハティ増幅器

【課題】 バックオフ領域で動作しているときの利得を抑制することができ、ピーク増幅器に好ましく適用され得る化合物半導体装置を提供する。

【解決手段】 化合物半導体材料からなる下側電子走行層(3)の上に、n型にドーピングされ、下側電子走行層よりも電子親和力の小さな化合物半導体材料からなる下側電子供給層(4)が配置されている。下側電子供給層の上に、該下側電子供給層よりもドーピング濃度が低いか、またはノンドープの化合物半導体材料からなる上側電子走行層(5)が配置されている。上側電子走行層の上に、該上側電子走行層よりも電子親和力の小さなn型化合物半導体材料からなる上側電子供給層(7)が配置されている。上側電子供給層の上に、相互に離隔して配置され、下側電子走行層及び上側電子走行層にオーミックに接続されるソース電極及びドレイン電極が配置されている。ソース電極とドレイン電極との間の、上側電子供給層の上に、ゲート電極が配置されている。

(もっと読む)

低電圧動作の基準電圧源回路

【課題】基準電圧源回路の電源(動作)電圧を1V以下にすることは困難である。

【解決手段】スレッシュホールド電圧Vtの温度特性が共に等しく、その温度係数の符号が互いに逆で、不純物濃度が互いに異なるゲートを有する2つのMOSトランジスタにおけるゲート・ソース間電圧の差を基準電圧Vrefとして出力する。両トランジスタのゲートを相互接続し、一方のトランジスタのソースを接地すれば、前記ゲート・ソース間電圧の差は、他方のトランジスタのソース電圧となり、このソース電圧がVrefとなる。

(もっと読む)

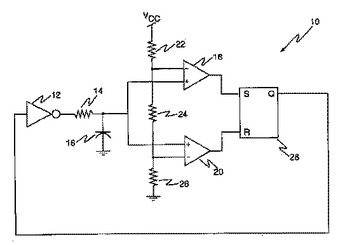

電圧補償及び温度補償されたRC発振回路

入力及び出力を有するインバータを具備する、温度補償された集積RC発振回路。RC網は、前記インバータと、比較器の対との間に接続されている。第1比較器は、第1基準電圧に接続された反転入力と、前記RC網に接続された非反転入力と、出力とを具備する。第2比較気は、前記RC網に接続された反転入力と、第2談笑電圧に接続された非反転入力と、出力とを具備する。セット・リセット・フリップフロップは、前記第1比較器の出力に接続されているセット入力と、前記第2比較器の出力に接続されているリセット入力と、前記インバータの入力に接続されている出力とを具備する。前記比較器の差動増幅器は、各々ミラー接続されたpチャネルMOSトランジスタを制御する、ダイオード接続されたpチャネルMOSトランジスタを具備し、前記pチャネルMOSトランジスタのチャネル幅は、前記ダイオード接続されたpチャネルカレントミラートランジスタの幅より狭い。  (もっと読む)

(もっと読む)

ドハティ増幅器および信号増幅方法

第1出力及び第2出力を有し、第1出力が90°だけ位相が異なる第1及び第2出力を有する主電力スプリッタ(332)と接続され、第2出力が90°だけ位相が異なる第1及び第2出力を有する補助電力スプリッタ(342)と接続されている電力スプリッタ(120)と、第1(334)及び第2(335)の主対増幅器の入力が主電力スプリッタ(332)の第1及び第2出力と接続されて成る主最終段階増幅器(234)と、第1(344)及び第2(345)の補助対増幅器の入力が補助電力スプリッタ(342)の第1及び第2出力と接続されて成る補助最終段階増幅器(244)であり、第1の主対増幅器(334)からの出力がインピーダンス変換器(250)によって第1の補助対増幅器(344)からの出力と接続され、第2の主対増幅器(335)からの出力がインピーダンス変換器(251)によって第2の補助対増幅器(345)からの出力と接続され、相対的な位相シフトがインピーダンス変換器の位相シフトをオフセットすべく主及び補助の電力スプリッタへの信号入力に与えられるように、主及び補助対増幅器を配置して成る。 (もっと読む)

1 - 20 / 20

[ Back to top ]