Fターム[5J500AK31]の内容

Fターム[5J500AK31]に分類される特許

1 - 20 / 193

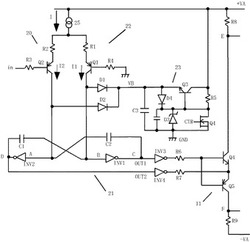

パルス幅変調回路およびスイッチングアンプ

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

可変利得増幅システム

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】本可変利得増幅回路は、入力信号から不要の相関ノイズ成分を除去する相関二重サンプリング回路1202と、相関二重サンプリング回路の下流側に位置する第1プログラマブル利得増幅器104と、入力が前記第1プログラマブル利得増幅器の入力に接続され、出力が相関二重サンプリング回路の入力に接続され、入力信号のオフセットおよび相関二重サンプリング回路のオフセットのうちの少なくともいずれか一方のために第1オフセット補正を提供する第1オフセット補正回路500と、第1プログラマブル利得増幅器の下流側に位置するアナログ/ディジタル変換器106と、第1プログラマブル利得増幅器の下流側に位置し、第2オフセット補正を提供する第2オフセット補正回路502と、相関二重サンプリング回路の下流側であって、かつ、第1プログラマブル利得増幅器の上流側に位置する画素利得増幅器1204を備えている。

(もっと読む)

スイッチドキャパシタ積分器

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

電子回路およびその制御方法

【課題】ドレインアイドル電流のドリフトを直接補償すること。

【解決手段】入力信号が入力するゲートと、出力信号が出力するドレインとを有するFETを含む電子回路の制御方法であって、前記FETのゲートに前記入力信号が入力してからの時間t経過後における前記入力信号x(t)に対応するドレインアイドル電流の変化量ΔIdq(t)を算出するステップS10と、前記変化量ΔIdq(t)を補償するためのゲートバイアス電圧Vgを算出するステップS12と、前記ゲートバイアス電圧を前記FETのゲートに印加するステップS14と、を含むことを特徴とする電子回路の制御方法。

(もっと読む)

増幅回路および帰還回路

【課題】反転入力容量Csinが異なる場合、帰還容量Cfが小容量の固定値であっても、周波数特性の肩特性の劣化やピークがほとんど生じない増幅回路および帰還回路を提供する。

【解決手段】個別に負帰還をかけるとともに直列に接続された複数の増幅器と、前記複数の増幅器に含まれる出力側の増幅器の出力側と入力側の増幅器の入力側に接続された帰還手段(帰還回路)とを備え、前記複数の増幅器は奇数個の反転増幅器を含む構成である。

(もっと読む)

電源発生システム

【課題】アンプが必要とする電源を提供するために用いられ、発生される電源は入力信号の大小に従い適切に変化し、これにより、大幅なエネルギーの損失を省くことができ、電池の作動時間を延長させることが可能なだけでなく、熱量の発生と排出を減少させることが可能な電源発生システムを提供する。

【解決手段】少なくとも一つの信号追跡ユニットは入力信号を受信し、これに基づき追跡信号を発生させ、前記追跡信号の波形は入力信号のピークを追跡する。少なくとも一つのDC−DCコンバータは前記追跡信号を受信し、これに基づき電源を発生させる。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

電力増幅器

【課題】 オフセット補正後の電力増幅器の動作開始時に電力増幅器に接続されたスピーカからポップ音が発生するのを防止する。

【解決手段】 直流電圧発生回路170は、D級増幅器内の差動増幅器のオフセットキャンセルを行わせるためにD級増幅器の出力端子T21およびT22に直流電圧を供給する。この直流電圧発生回路170の出力端子T30と接地線との間には放電用抵抗RDISとNチャネルトランジスタ183が介挿されている。オフセットキャンセルが終わった後、D級増幅器の増幅動作が開始される前の安定期間に、Nチャネルトランジスタ183はONとされ、出力端子T21およびT22に接続された容量C1およびC2の充電電荷が放電用抵抗RDISおよびNチャネルトランジスタ183を介して放電される。これによりポップ音の発生を防止することができる。

(もっと読む)

パルス幅変調回路およびスイッチングアンプ

【課題】 オーディオ信号の振幅が負側に過大になったときのパルス幅変調信号の応答性を安定させる。

【解決手段】 パルス幅変調回路10は、クロック生成回路11と、差動増幅回路12と、第1充電電流生成回路13と、第2充電電流生成回路14と、スイッチSW1〜SW4と、コンデンサC1,C2と、第1放電用定電流回路15と、第2放電用定電流回路16と、第1パルス生成回路17と、第2パルス生成回路18と、パルス合成回路19と、充電開始電圧維持回路20とを備える。充電開始電圧維持回路20は、コンデンサC1、C2の電圧が定電流Idによる放電動作によって電圧Vaよりも低下しようとするときに、電源電圧をコンデンサC1、C2に供給することによって、コンデンサC1、C2の充電開始電圧がVaよりも低下することを防止する。

(もっと読む)

電圧出力回路、及びアクティブケーブル

【課題】面積及び消費電力を低減し、高精度に単相差動変換をすることができる電圧出力回路を提供する。

【解決手段】電圧出力回路は、第1の電圧Vopが入力される一端、及び第2の電圧Vomを出力する他端を備える抵抗素子R1と、抵抗素子R1の他端に接続される反転入力端子、及び第3の電圧Vrefが入力される非反転入力端子を備える第1の増幅器121と、第1の増幅器121からの出力が入力される一端、及び抵抗素子R1の他端が接続される他端を備えるコンデンサC1と、を備え、第1の増幅器121の出力、または抵抗素子R1の他端に接続される第2の増幅器122の出力は、第1の電圧Vopの積分値である第4の電圧Vdcocであり、コンデンサC1、及び第1の増幅器121で構成されるミラー容量と、抵抗素子R1とによって、ローパスフィルタが構成される。

(もっと読む)

デジタルアンプ

【課題】デジタルパルス幅変調におけるパルスのデューティの補正範囲を広げることができ、歪率を改善することができるデジタルアンプを提供すること。

【解決手段】デジタルアンプ200は、デジタル変調ブロック210のデジタルパルス幅のデジタル値を電圧値に変換する電圧値変換ブロック220と、マスタークロックにより三角波を発生し、かつ、前記発生した三角波を、前記デジタルパルス幅変調の変調幅の値に応じた信号を基に変調する積分回路ブロック230とを備える。デジタルアンプ200は、駆動回路250により電力増幅された信号を低域濾波し、アナログオーディオ電圧を出力する低域濾波器265(低域濾波器<3>)と、低域濾波器280(低域濾波器<1>)の電圧と低域濾波器265(低域濾波器<3>)の差の電圧を演算して増幅する誤差増幅器290とを備える。上記各部は、全体としてアナログ局部帰還を持つ回路構成となっている。

(もっと読む)

オーディオミキシング装置及び方法並びに電子機器

【課題】従来技術に比較して構成が簡単であって、消費電力を軽減できるオーディオミキシング装置及び方法、並びに当該オーディオミキシング装置を備えた電子機器を提供する。

【解決手段】オーディオミキシング装置は、複数のディジタルオーディオ信号からそれぞれ変換された複数のPDM信号を加算するアナログ加算器と、上記アナログ加算器から出力されるディジタルオーディオ信号をアナログオーディオ信号にDA変換して出力するDA変換器とを備えた。

(もっと読む)

チャージアンプ

【課題】アナログスイッチとアナログスイッチ及びアナログスイッチと電荷信号を放電させるリセット回路とを備えることでオペアンプの入力端には流れこまないようにした、漏れ電流が信号に影響を与えないようにしたチャージアンプを提供する。

【解決手段】オペアンプ2の出力端子6とオペアンプ−入力端3に接続された積分コンデンサ7に、直列に接続したアナログスイッチS1とアナログスイッチS2を並列に接続し、更に前記アナログスイッチS1と前記アナログスイッチS2の接続点から接地点との間にアナログスイッチS3を接続し、前記積分コンデンサに充電した電荷信号を前記スイッチS1及びS2とで放電させるリセット回路とを備えたことを特徴とする圧電型センサの電荷信号を電圧信号に変換するチャージアンプにより提供される。

(もっと読む)

オフセット補正回路

【課題】オフセットを迅速に検出しつつ、低域信号のカットを防止する。

【解決手段】オフセット検出回路(22a,22b,24,26)は、利得可変アンプ18の出力を所定の時定数で平滑して、直流成分であるオフセットを検出する。検出されたオフセットは加算回路28において利得可変アンプの入力に加算して、利得可変アンプ18の出力におけるオフセットを補正する。オフセット検出回路における時定数は、可変抵抗22a,22bの抵抗値により変更される。そして、時定数は、利得可変アンプ18の利得が変更されたときに、小さな時定数、その後大きな時定数に変更される。

(もっと読む)

D級増幅回路

【課題】入力信号を適切に減衰させるとともに減衰時にも音量を変化させる

【解決手段】増幅部20は、入力端12pおよび12nの各々に互いに逆相で供給される入力信号SpおよびSnに応じてパルス幅変調された出力信号QpおよびQnを生成する。第1減衰部30は、トランジスタTR1と電圧印加回路32とを含む。トランジスタTR1は、入力端12pから増幅部20に至る入力経路16aと入力端12nから増幅部20に至る入力経路16bとの間に介挿される。電圧印加回路32は、入力信号SpおよびSnのレベルが所定値を上回る範囲で増加するほどトランジスタTR1の両端間に流れる電流が増加するように、所定値に対応する制御電圧VCをトランジスタTR1の制御端子に印加する。

(もっと読む)

信号増幅回路

【課題】入力電圧に比例した電流を出力するOTAの製造ばらつきおよび周囲温度の変化による利得の変化を抑制することが可能な信号増幅回路を提供する。

【解決手段】入力電圧Vinが入力される第1のOTA1、第1のコンデンサC1を有する第1の積分器10と、第1のコンデンサC1に並列接続された第1のアナログスイッチSW1と、入力電圧Vinの積分時間を調整する積分時間調整回路3とを備える。積分時間調整回路3は、第1の参照電圧Vref1が入力される第2のOTA2、第2のコンデンサC2を有する第2の積分器20と、第2のコンデンサC2に並列接続された第2のアナログスイッチSW2と、第2の積分器20の出力電圧と第2の参照電圧Vref2とを比較するコンパレータCP2とを備え、コンパレータCP2の出力に基づいて第1のアナログスイッチSW1、第2のアナログスイッチSW2それぞれを制御する第1の制御信号、第2の制御信号を出力する。

(もっと読む)

半導体装置及びこれを用いた電子機器

【課題】電源電圧のばらつきに依ることなく、入力信号を適切に電力増幅して出力信号を生成することが可能な半導体装置、及び、これを用いた電子機器を提供する。

【解決手段】半導体装置100は、VDDとGNDとの間でパルス駆動される入力信号Sinを増幅し、VCC(>VDD)とGNDとの間でパルス駆動される出力信号Soutを生成するドライバZ20と、VCCからVDDを生成するVDD生成部Z30と、を有するものであって、ドライバZ20は、VDDの入力を受けて動作し出力信号Soutの帰還経路となる1次積分器(AMP、R1、R2、C1)を含み、VDD生成部Z30は、VCCを分圧してVDDを生成する分圧器(R3、R4)を含む。

(もっと読む)

信号増幅回路、電流電圧変換回路、および光受信器

【課題】入力電流の大きさの変化に応じた出力電圧波形の歪みを抑えることができる信号増幅回路、電流電圧変換回路、および光受信器を提供する。

【解決手段】プリアンプ13は、トランジスタ21、及び該トランジスタ21と電源電位線18との間において出力信号を提供するノードAを有し、光電流Iinを受ける信号入力端13aにトランジスタ21のエミッタが接続され、ノードAにトランジスタ21のコレクタが接続されたベース接地回路20と、ノードAに接続され、出力電圧Voutの平均レベルから利得制御信号Vagcを生成する検知回路50と、ベース接地回路20に対して並列に接続されたトランジスタ31を有し、そのベースに利得制御信号Vagcを受ける分流回路30とを備える。検知回路50は、平均レベルの上昇に応じてトランジスタ31を流れる電流が大きくなるように利得制御信号Vagcを生成する。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

1 - 20 / 193

[ Back to top ]