Fターム[5J500AM21]の内容

Fターム[5J500AM21]に分類される特許

121 - 140 / 988

電気機器

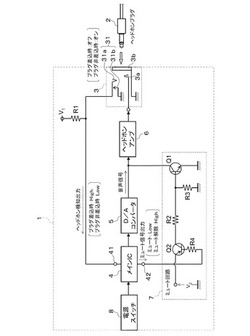

【課題】電気機器において、電源投入時に生じ得るヘッドホンからのポップ音出力を抑え、しかも、そのポップ音出力抑制に必要な電力を減らす。

【解決手段】電気機器1は、ヘッドホンプラグ2が抜き差しされるヘッドホンジャック3と、メインIC4と、ヘッドホンジャック3による音声信号出力をミュートするミュート回路7とを備える。メインIC4及びミュート回路7は電気機器1の電源が未投入であっても給電され、メインIC4は、ヘッドホンプラグ2が差し込まれているときにはミュート回路7を駆動し、ヘッドホンプラグ2が差し込まれていないときにはミュート回路7を駆動しない。ヘッドホンプラグ2差込時のミュート回路7の駆動により、電源投入時に生じ得るポップ音出力を抑えることができる。また、ミュート回路7はヘッドホンプラグ2が差し込まれていないときには駆動しないので、ポップ音出力抑制に必要とされる電力を低減することができる。

(もっと読む)

周波数変換回路

【課題】変換利得のばらつきを極めて小さく抑制された周波数変換回路を実現する。

【解決手段】入力電圧信号を電流信号に変換するGMアンプ10と、該変換して得られた電流信号をローカル信号でミキシングして周波数変換を行うスイッチング回路部(ミキサ)20と、該周波数変換によって得られた電流信号を電圧信号に変換するIV変換部(IV変換アンプ)30と、GMアンプ10へバイアス電圧を供給するバイアス回路(GM校正回路)40と、を備えGM校正回路40は、GMアンプ10に用いるトランジスタとそのサイズあたりの相互コンダクタンスを同一としたトランジスタを用いたレプリカアンプを内部に有し、該レプリカアンプに、抵抗と第1電流源からの電流との積に相当するDC電圧を入力し、該レプリカアンプからの電流出力が所定値になるように、該レプリカアンプの電圧バイアスを設定し、抵抗の分割点の電圧をGMアンプ10に供給する。

(もっと読む)

誤差増幅器

【課題】誤差増幅器における、受動素子の定数のばらつきに起因する帰還回路の定数のばらつきを抑制する。

【解決手段】誤差増幅器における帰還回路の定数が、受動素子の定数だけでなく、能動素子の利得にも依存して決定される構成にする。この誤差増幅器は、能動素子である電圧電流変換器20を含む構成である。また、第1の端子11、第2の端子13、オペアンプ16、第1の抵抗R1、第2の抵抗R2、第1乃至第5のトランジスタ、第1の電流源14および第2の電流源15を一体の集積回路とし、コンデンサC1を外付けしてもよい。

(もっと読む)

バースト光受信器

【課題】ATC回路を不要とし、かつ受信感度特性に優れたバースト光受信器を得る。

【解決手段】バースト光受信器1において、光バースト信号を電流信号に変換する受光素子2と、電流信号を電圧信号に変換する差動型トランスインピーダンスアンプ回路3と、差動型トランスインピーダンスアンプ回路3からの電圧信号を識別する差動型識別回路4と、一端が電源に接続され他端が受光素子2のカソードに接続された誘導性素子62と、一端が受光素子2のアノードに接続され他端がGNDに接続された誘導性素子61と、一端が誘導性素子62と受光素子2との接続端に接続され他端が差動型トランスインピーダンスアンプ回路3に接続された容量性素子52と、一端が誘導性素子61と受光素子2との接続端に接続され他端が差動型トランスインピーダンスアンプ回路3に接続された容量性素子51と、を備える。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

低ドロップアウト線形レギュレータ(LDO)、LDOを提供するための方法、およびLDOを動作させるための方法

【課題】PSRRが改良された低ドロップアウト線形レギュレータを提供する。

【解決手段】LDOは、差動増幅器と調整されたカレントミラーとを結合し、それぞれ差分信号を受信するように構成された2つのノードを有する。調整されたカレントミラーは、差分信号をシングルエンド信号に変換および増幅するように構成される。LDOは、周波数補償用に構成された第1のコンデンサを有し、第1のコンデンサは、第1の段と第2の段との間に結合される。LDOは、第1のカスコード回路の容量性負荷を平衡化するための第2のコンデンサを有し、第2のコンデンサは、第1の段と電源電圧との間に結合される。第1のカスコード回路は、電源電圧の変動によって生じるコンデンサの入出力間の差電圧を抑制するように構成される。LDOは、差動増幅器の電源の変動を抑制するように構成された第2のカスコード回路を有する。

(もっと読む)

差動信号生成回路及び周波数変換回路

【課題】差動信号生成回路におけるS/N比の改善を図ること。

【解決手段】差動信号生成回路31は、入力されたRF信号を増幅するソース接地回路311と、増幅されたRF信号の差動信号RF+,RF−を生成するドレイン接地回路312と、生成された差動信号RF+,RF−の位相差を調整する容量部313とを備えて構成される。また、ドレイン接地回路312における第1の抵抗R1及び第2の抵抗R2によって、差動信号RF+,RF−の振幅が同じとなるとともに、容量部313によって、差動信号RF+,RF−の位相差がほぼ180度となるように調整される。

(もっと読む)

電圧−電流変換回路

【課題】必要な線形性を満たし、電力消費を抑え、トランスコンダクタンスを任意の値に変更でき、高周波で動作し、低電源電圧で動作し、出力電流を独立に設定できる電圧−電流変換回路を提供する。

【解決手段】入力電圧を電流に変換すると共に出力電流を変化させる電圧−電流変換本体回路と、電圧−電流変換本体回路の出力電流を増幅する電流増幅回路と、バイアス電流及び増幅率に応じて適切な電流を出力から引く電流源と、GM及び電流増幅回路の出力を独立して設定可能なバイアス電流を生成するバイアス回路と、を備えた。

(もっと読む)

差動増幅器

【目的】高利得であり且つ高速動作が可能な差動増幅器を提供することを目的とする。

【構成】第1及び第2入力端子に夫々入力された信号同士の差分を表す信号及びその位相反転信号を夫々第1及び第2出力端子を介して出力する差動増幅器に、オン状態時に第1入力端子及び第2出力端子同士を短絡する第1スイッチング素子と、オン状態時に第2入力端子及び第1出力端子同士を短絡する第2スイッチング素子と、オン状態時に第1及び第2出力端子同士を短絡する第3スイッチング素子と、を設ける。この際、第1及び第2スイッチング素子を共にオフ状態に設定しつつ第3スイッチング素子を所定期間だけオン状態に設定した後、第3スイッチング素子をオフ状態に切り替えると共に第1及び第2スイッチング素子を共にオン状態に切り替える。

(もっと読む)

ダイナミックバイアスを有するRFバッファ回路

電圧制御発振器(VCO)に対するRFバッファ回路は、出力電圧波形の位相を選択的にフリップするために、ダイナミックバイアス回路を含んでいる。CMOSインプリメンテーションにおいて、PMOS/NMOSペアは、出力パス内に採用される。ハイ(電圧)スイングモード状態の最中に、出力の位相は、出力波形がPMOS/NMOSペアのゲートに出現する電圧に対して同相となるようにフリップされる。本技術は、それによって、ゲート−ドレイン間電圧を減少させ、低位相ノイズ及び低消費電力にしたがった構成内のMOSデバイスの改善された信頼性を許容する。  (もっと読む)

(もっと読む)

増幅器バイアス技術

第1及び第2のアクティブトランジスタを有するクラスAB増幅器に対してバイアス電圧を発生する技術。ダイオード結合された第1のトランジスタは第1の電流をサポートし、第1のトランジスタのゲート電圧は第1のアクティブトランジスタのゲート電圧に結合される。第1の電流は第2の電流及び第2のトランジスタによってサポートされる第1の補助電流に分割され、第2のトランジスタはクラスAB増幅器のコモンモード出力電圧でバイアスされる。第1の補助電流は第3のトランジスタによってサポートされる第3の電流に結合され、第3のトランジスタは第2のアクティブトランジスタの特性を複製する。第3のトランジスタのドレイン電圧をコモンモード出力電圧に近づけるように設定する技術が与えられる。技術は、クラスAB増幅器内のNMOS及び/又はPMOSアクティブトランジスタに対するバイアス電圧を与えるために用いられる。  (もっと読む)

(もっと読む)

信号増幅回路

【課題】安価な構成でフィードバック動作が行われる信号増幅回路を提供する。

【解決手段】本発明に係る信号増幅回路100は、入力信号DIN1を増幅してアナログの出力信号AOUTを生成する増幅部10と、入力信号DIN1に基づいて出力信号AOUTが基準値Vrefに到達すべき基準タイミングを特定し、当該基準タイミングにおいて、出力信号AOUTと基準値Vrefとを比較し、その比較結果に応じて、増幅部10のゲインを制御するゲイン制御信号Gを生成して増幅部10における入力信号補正部12へ帰還させるフィードバック部20と、を具備する。

(もっと読む)

差動増幅器

【課題】非反転入力端子の電圧が変化した場合でも、出力トランジスタに流れる電流を一定にすることができる、差動増幅器を提供する。

【解決手段】非反転入力端子143と、反転入力端子144と、P型MOSトランジスタ107及び108とN型MOSトランジスタ101及び102と定電流源121とからなる差動増幅回路と、P型MOSトランジスタ103及び104とN型MOSトランジスタ113及び114と定電流源122とからなる差動増幅回路と、P型MOSトランジスタ107及び108に電流を流す定電流源124とで構成される相補型フォールデッドカスコード増幅回路に、さらにP型MOSトランジスタ107及び108に電流を流す電流制御回路である、定電流源123とN型MOSトランジスタ105を備え、相補型差動対の負荷であるカスコード増幅回路に流れる電流を、非反転入力端子の電圧によって制御する構成とした。

(もっと読む)

スイッチング増幅器のためのパルス幅変調

本願では、スイッチング増幅器(120)のためのパルス幅変調を実施するための装置および方法が説明される。一実施形態において、装置は、サンプリング信号(208)を生成するためのサンプリング信号生成器(202)と、サンプリング信号生成器(202)に動作可能に結合された変調部(102)とを含む。変調部(102)は、サンプリング信号(208)と差動入力信号(220−1および220−2)とに基づいて、少なくとも1つの差動パルス幅変調波形が差動入力信号(220−1および220−2)のすべての値において所定の非ゼロの最小パルス幅に等しいデューティサイクルを有するように差動パルス幅変調波形を生成する。  (もっと読む)

(もっと読む)

D級増幅回路

【課題】簡易な構成で、D級増幅回路の出力電流を反転可能にする。

【解決手段】本発明に係るD級増幅回路100は、入力信号AINに応じて第1状態と第2状態とが切り替えられる。第1状態では、コイルLと負荷30とが電気的に切り離された状態で、第1ノードND1から第2ノードND2へ向かう電流がコイルLに流れた後、コイルLと負荷30とが電気的に接続されて、第1ノードND1から第2ノードND2へ向かう電流が負荷30を流れるとともに容量素子Cに充電される。第2状態では、コイルLと負荷30とが電気的に切り離された状態で、第2ノードND2から第1ノードND1へ向かう電流がコイルLに流れた後、コイルLと負荷30とが電気的に接続されて、第2ノードND2から第1ノードND1へ向かう電流が負荷30を流れるとともに容量素子Cに充電される。

(もっと読む)

スイッチトエミッタフォロワ回路

【課題】トラックモード時の歪み特性を悪化させることなくアクイジション時間を短縮する。

【解決手段】出力電圧を入力電圧に追従させるトラックモードと、出力電圧を保持するホールドモードとを切り替え可能なスイッチトエミッタフォロワ回路であって、ベースに入力電圧端子とスイッチを介して定電流源が接続され、エミッタに出力電圧端子と可変電流源とが接続され、コレクタに電源電圧が印加されるトランジスタと、一端に電源電圧が印加され、他端が出力電圧端子に接続された容量と、スイッチと可変電流源の電流値を制御する制御部とを備え、制御部は、ホールドモードからトラックモードへの切り替えの際に、スイッチをオフからオンに切り替えるとともに、可変電流源の電流値を0から第1に切り替え、所定の時間経過後に、電流値を第1の値よりも大きな第2の値に切り替える。

(もっと読む)

検出回路

【課題】プロセスミスマッチ等によるサンプルごとの検出電圧レベルのばらつきを低減させることができ、高速動作を行うことが可能な検出回路を提供する。

【解決手段】1対のシリアルデータ信号の一方が反転入力端に入力され、他方が非反転入力端に入力される第1検出用レシーバ回路と、1対のシリアルデータ信号の一方が非反転入力端に入力され、他方が反転入力端に入力される第2検出用レシーバ回路と、第1検出用レシーバ回路及び第2検出用レシーバ回路の各出力信号に基づいて、入力検出及び切断検出の少なくとも一方を行う検出回路とを備え、第1検出用レシーバ回路及び第2検出用レシーバ回路は、それぞれ第1差動入力回路及び第1負荷回路を含む差動増幅回路と、差動増幅回路の閾値に設ける第1オフセット制御回路とを有し、第1負荷回路はドレインが独立でゲートを共通とし、ゲートに所定の電圧が印加される1対のMOSトランジスタを含んで構成される。

(もっと読む)

増幅器回路、集積回路及び無線周波数通信ユニット

増幅器回路は、入力ノードを有し、入力ノードで受信される入力信号を増幅する。増幅器回路は、出力ノードと、入力ノードと出力ノードとの間に接続されるフィードバック抵抗と、フィードバック抵抗に沿った点で相互コンダクタンス電流を投入するよう配置される相互コンダクタンス回路とを更に有する。相互コンダクタンス回路は、相互コンダクタンス電流が投入されるフィードバック抵抗に沿った点を変更するよう構成される。

(もっと読む)

(もっと読む)

プッシュプル増幅回路およびこれを用いた演算増幅回路

【課題】回路規模、消費電流が大きかった。

【解決手段】第1の電流経路は入力信号に応じて第1の電流を流す第1のトランジスタを有し、前記第2の電流経路は前記第1の電流に応じて前記第1の電流と逆相の第2の電流を流す第2のトランジスタと第1の抵抗と前記第1の抵抗の一端に接続され前記第1の抵抗の他端が制御端子に接続される第3のトランジスタとを有し、前記第3の電流経路は出力端子と前記入力信号に応じて前記第1の電流と同相の電流を流す第4のトランジスタと前記第1の抵抗と前記第3のトランジスタとの間の第1のノードの電位に応じて前記第2の電流と同相の電流を流す第5のトランジスタと、を有するプッシュプル増幅回路。

(もっと読む)

共通のバイアス電流をシェアする複数の増幅ステージを用いて信号を増幅するシステム及び方法

装置は、共通のDC電流によってバイアスされ、入力信号から増幅された出力信号を発生するように適応されたカスケードの増幅ステージを含む。第1の増幅ステージは、入力電圧信号を実質的に2倍にするルーティングネットワークと、入力電圧信号から第1の電流信号を発生する第1の相互コンダクタンスゲインステージとを含む。第2の増幅ステージは、第1の電流信号を第2の電圧信号に変換する共振器と、第1の電流信号から第2の電流信号を発生する第2の相互コンダクタンスステージとを含む。第3の増幅ステージは、第2の電流信号から第3の電流信号を発生する電流ゲインステージと、第3の電流信号が流れて出力信号を発生する負荷とを含む。  (もっと読む)

(もっと読む)

121 - 140 / 988

[ Back to top ]