Fターム[5J500AM21]の内容

Fターム[5J500AM21]に分類される特許

101 - 120 / 988

シグナリングシステム、前置増幅器、メモリデバイスおよび方法。

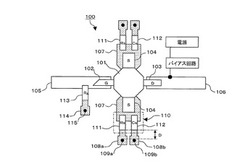

高周波増幅回路

【課題】略10GHz以上の準ミリ波帯、ミリ波帯以上で1つの電源を用いて安定的に動作する高周波増幅回路を提供する。

【解決手段】高周波トランジスタ101は、ゲート端子102側が入力端子105に接続され、ドレイン端子103側が出力端子106に接続されている。2つのソース端子104には、ランド107を介して抵抗111とコンデンサ112からなるセルフバイアス回路110が接続されている。抵抗111及びコンデンサ112の他端は、それぞれランド108a、108b及びスルーホール109a、109bを介して接地されている。ランド108(108a、108b)上における抵抗111及びコンデンサ112との接続点からスルーホール109(109a、109b)までの距離Dが好適に調整されている。

(もっと読む)

シングルサプライD級アンプ

高周波パワーアンプ

【課題】

高周波パワーアンプの試験工程のコストを低減する。

【解決手段】

高周波パワーアンプは,インダクタを有する入力整合回路と,前記入力整合回路を通過した入力信号を増幅する増幅トランジスタと,入力整合回路内のインダクタに第1の試験スイッチにより接続されるキャパシタと,インダクタに第2の試験スイッチを介して第1の基準電圧との間に設けられた負性抵抗用トランジスタと,第2の基準電圧とインダクタとの間に設けられた電流源トランジスタとを含む試験用回路とを有し,試験時に第1,第2の試験スイッチ及び電流源トランジスタが導通してインダクタと試験用回路とで高周波発振器が構成され,通常動作時に第1,第2の試験スイッチ及び前記電流源トランジスタが非導通になる。

(もっと読む)

クラス特性可変増幅器

差動増幅回路及びA/D変換器

【課題】電源電圧が比較的小さい場合においても、性能劣化を起こさず、かつオーバードライブリカバリ可能な差動増幅回路を得る。

【解決手段】第1の出力部であるノードN1と電源Vddとの間にPMOSトランジスタMP1及びMP3が互いに並列に介挿され、第2の出力部であるノードN2と電源Vddとの間にPMOSトランジスタMP2及びMP4が互いに並列に介挿される。レプリカ回路4及びコンパレータ5によって、入力電圧Vinと基準電圧Vrefとの入力電位差が“0”のバランス状態時の出力電圧Voutp及びVoutnは共に基準出力コモン電圧Voutcm_idealに設定される。電源電圧Vddと出力コモン電圧Voutcmとの電位差がダイオード接続されたPMOSトランジスタMP1及びMP2の閾値電圧Vthよりも低い値となるように、レプリカ回路4の基準出力コモン電圧Voutcm_idealを設定する。

(もっと読む)

半導体集積回路装置

【課題】入力容量および雑音を小さくした半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、入力信号が入力される入力端子と出力信号が出力される出力端子とを有する増幅器と、バイアス電流を生成する第1のトランジスタを有し、前記バイアス電流により動作し、前記出力信号を入力してフィードバック信号を前記入力端子に供給するフィードバック回路と、を備え、前記第1のトランジスタのゲートに、前記出力信号とは逆相の信号が入力されることを特徴とする。

(もっと読む)

電力増幅装置

【課題】高出力と専有面積の縮小とを両立させた電力増幅装置を提供する。

【解決手段】基板上に形成された電力増幅装置300であって、全体で環状の一次インダクタ1,2と、グランドパターン4〜8と、トランジスタ対(Q1p,Q1n)および(Q2p,Q2n)と、二次インダクタ3とを備える。グランドパターン4〜8は、基板に垂直な方向から見て、環状の一次インダクタ1,2の内側の領域の一部から外側の領域に及ぶように設けられ、外側の領域の複数箇所で接地される。各一次インダクタ1,2の両端には、対応のトランジスタ対を構成する第1および第2のトランジスタの第1の主電極がそれぞれ接続される。第1および第2のトランジスタの各第2の主電極は、一次インダクタの内側の領域でグランドパターンに接続されるとともに、上記の接地された複数箇所のいずれとも電気的に導通する。

(もっと読む)

クラスAB増幅器

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

RFダウンコンバージョンミキサのための共通ゲート共通ソース相互コンダクタンスステージ

【課題】RFダウンコンバージョンミキサのための共通ゲート共通ソース相互コンダクタンスステージを提供する。

【解決手段】無線デバイス受信機チェーンは、共通ゲート共通ソース(CGCS)入力ステージ312を有するミキサ314を含む。チップ303外マッチングネットワーク308からの差動信号310、311は、ミキサのCGCS入力ステージに入力されることができて、ミキサは、信号をベースバンドあるいはいくつかの中間周波数にダウンコンバートする。入力ステージは、共通ゲート構成における1ペアのNMOSトランジスタと、共通ソース構成における1ペアのPMOSトランジスタと、を含む。存在するCGO相互コンダクタンス入力構成に対する、CGCS入力ステージの潜在的な利点は、PMOS差動ペアを通して、共通のソースステージを加えることによって、相互コンダクタンス利得が、高いQマッチングネットワークからデカップルされる。

(もっと読む)

回路ユニット、回路ユニットを有するバイアス回路、並びに第1及び第2の回路ユニットを有する差動増幅回路

ヘテロ接合バイポーラトランジスタ及びロングゲート疑似格子整合高電子移動度トランジスタを備える回路ユニット(CU)。前記ロングゲート疑似格子整合高電子移動度トランジスタのソース(S)又はドレイン(D)が、前記ヘテロ接合バイポーラトランジスタのコレクタ(C)又はエミッタ(E)に電気的に結合される。 (もっと読む)

電流源、電流源回路、およびこの電流源回路の使用

【課題】MOS技術を使ったパワー素子を用いなくても、正確な負荷電流を供給しうる電流源を提供する。

【解決手段】電流源10が、制御端子および制御パスを有するバイポーラトランジスタ1と、バイポーラトランジスタ1の制御パス上にあって、電気負荷D1と接続される第1の端子と、抵抗器4経由で基準電源端子と接続される第2の端子と、バイポーラトランジスタ1の制御端子に接続され、この制御端子に送られる制御電流を測定する測定装置2と、バイポーラトランジスタ1の制御電流が制御パス上に位置する第1の端子において補償されるように、測定装置2およびバイポーラトランジスタ1に接続された補償電流源3とを備える。

(もっと読む)

高周波増幅回路及びそれを用いた移動体通信端末

【課題】バイアス電流の制御電圧の設定範囲を拡大させつつ、バイアス回路の構成の自由度を向上させ、簡単かつ小規模な構成で複数の通信方式への対応を実現する高周波増幅回路を提供する。

【解決手段】バイアス回路12を、入力されるベース電流に応じたバイアス電流を増幅器11に供給するトランジスタQ5と、基準電圧Vrefに応じた電流を流すトランジスタQ3と、トランジスタQ3に流れる電流に応じて、トランジスタQ5のベース電流を補正することにより、トランジスタQ5の温度特性を補償するトランジスタQ2と、トランジスタQ5のベースに接続され、制御電圧VSWの切り替えに応じてトランジスタQ5のベース電流量を切り替えるバイアス切り替え部(トランジスタQ4及び抵抗R5〜R7)とで構成する。増幅器11は、バイアス回路12から供給されるバイアス電流を用いて、入力される高周波信号を増幅する。

(もっと読む)

増幅回路

【目的】簡明な構成で、バイポーラトランジスタが飽和状態となるのを防止するとともに、当該バイポーラトランジスタを高速にオフすることも可能な増幅回路を提供する。

【構成】NPNトランジスタQ1のベース端子と入力信号Vinの間にNチャネルMOSトランジスタMN1を設け、NPNトランジスタQ1のコレクタ端子とNチャネルMOSトランジスタMN1のゲート端子を接続することにより、NPNトランジスタQ1のベース・コレクタ間電圧がNチャネルMOSトランジスタMN1の閾値電圧以上となるので、NPNトランジスタQ1が飽和状態になることを防止できる。また、常にNチャネルMOSトランジスタMN1がオンして入力信号VinがNPNトランジスタQ1のベース端子に印加されるので、NPNトランジスタQ1を高速にオフすることができる。

(もっと読む)

誘導コモンモード減結合のあるプッシュプル増幅器

増幅すべき入力信号(e)を出力信号(a)に増幅するためのプッシュプル増幅器が一つの第1の及び一つの第2の増幅素子(1、1’)有する。前記2つの増幅素子(1、1’)のそれぞれが一つの電流放出電極(2、2’)、一つの集電電極(3、3’)、及び一つの電流制御電極(4、4’)を有する。前記増幅素子(1、1’)の前記電流制御電極(4、4’)に、それぞれの入力端子(6、6’)を介して、及び、それぞれの前記入力端子(6、6’)とそれぞれの前記電流制御電極(4、4’)との間に配置されたそれぞれの入力インダクタンス(5、5’)を介して、前記入力信号(e)が供給される。前記集電電極(3、3’)は、それぞれの供給インダクタンス(7、7’)を介して一つの共通の供給電圧(V+)に接続される。前記増幅素子(1、1’)の前記電流放出電極(2、2’)は、それぞれのコンデンサ(8、8’)を介してそれぞれもう一方の前記増幅素子(1’、1)の前記集電電極(3’、3)に接続される。前記電流放出電極(2、2’)は、前記出力信号(a)をピックアップ可能である出力端子(9、9’)に接続される。前記電流放出電極(2、2’)は、それぞれの出力インダクタンス(10、10’)を介して基準電位に接続されている。前記増幅素子(1、1’)の前記供給インダクタンス(7、7’)は、それぞれもう一方の前記増幅素子(1’、1)の前記入力インダクタンス(5’、5)及び前記出力インダクタンス(10’、10)に誘導結合される。  (もっと読む)

(もっと読む)

高電圧伝送による共聴システム

【課題】 簡易高電圧アンプによる共聴システム

【解決手段】 音響共聴システムは多くのスピーカを同時に鳴らすため大容量で多くの機能を備えるために高価な装置となっている。このような問題を解決するために商用電力を直接整流し、外部の音響機器(パソコン・ラジカセ・その他オーディオセット等)の信号により、整流電流をスイッチング変調することにより電力をダイレクトに負荷に供給することが出来る。

この出力は電源電圧を維持した高電圧となるため、負荷スピーカは高インピーダンスとすることが必要となる。

発明に供するアンプは整流電流をスイッチングする機能のみにて形態をなすため、安価で取り扱いの簡単なため、通常の共聴システムをはじめ、非常放送機能等により防災機器として、多くの問題を解決できる。

整流方式は負荷容量により半端整流、全波整流、倍電圧整流など選択できる。

(もっと読む)

雑音除去を備える広帯域LNA

雑音除去を備える低雑音増幅器(LNA)を改善するための技術が説明される。LNAは、入力ステージ回路において生成された雑音を除去するために協働する第1及び第2の増幅器を含む。入力ステージ回路は、RF信号を受信し、第1のノード及び第2のノードによって特徴付けられる。第1の増幅器は、第1のノードにおける雑音電圧を、第1の増幅器の出力において第1の雑音電流に変換する。第2の増幅器は、第1の増幅器の出力に直接結合され、第2のノードにおける雑音電圧の関数として第2の増幅器によって生成された第2の雑音電流と第1の雑音電流とを加算することによって、雑音除去を提供する。提案された技術は、大きな交流結合コンデンサへのニーズを排除し、LNAによって占められるダイ・サイズを低減する。LNAの増幅ステージ間での交流結合コンデンサの排除によって、電流の再利用が可能になり、その結果電流の消費が低減される。  (もっと読む)

(もっと読む)

デュアルレート振幅制限増幅回路

【課題】高感度、低消費電力、低コストのデュアルレート振幅制限増幅回路を提供する。

【解決手段】入力バッファ120と10Gbps用のアンプブロック200と1Gbps用のアンプブロック210とを同一のチップ(LAIC)101に搭載する。入力バッファ120は、差動入力端子P1から入力される差動信号の正相を正相信号、差動入力端子P2から入力される差動信号の逆相を逆相信号として出力する。この正相信号および逆相信号をLAIC101上で分岐してともに10Gbps用のアンプブロック200と1Gbps用のアンプブロック210へ与える。10Gbps用のアンプブロック200を直列に接続された複数のアンプ(10Gbps用のアンプ)150で構成し、1Gbps用のアンプブロック210を直列に接続された複数のアンプ(1Gbps用のアンプ)160で構成する。1Gbps用のアンプ160では、10Gbps用のアンプ150に比べ回路電流I0,I1を小さく設定する。

(もっと読む)

エラーアンプの位相補償回路

【課題】 ICチップ上のコンデンサ面積を小さくすることができる位相補償回路を提供する。

【解決手段】 エラーアンプの出力端子に容量と抵抗を直列接続し、容量に流れる電流を抵抗の両端に接続したトランスコンダクタンスアンプにより増幅してフィードバックすることにより、エラーアンプの周波数特性の主要極の周波数を低くする。

(もっと読む)

101 - 120 / 988

[ Back to top ]