Fターム[5J500AM21]の内容

Fターム[5J500AM21]に分類される特許

61 - 80 / 988

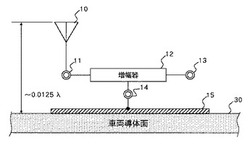

地上放送波受信用アンテナ装置及びその構成部品

【課題】FM帯以下の周波数帯域において、アンテナ素子長を55[mm]程度まで短縮しても、従来と同等以上の性能を有する地上放送波受信用アンテナ装置を提供する。

【解決手段】アンテナ素子10の受信波のうち当該アンテナ素子10の共振点以下の周波数の受信波を増幅する、受信周波数に対して等価雑音抵抗が2Ω以下となる化合物半導体HEMTとを含んで増幅器12−Aを構成し、雑音指数(NF)をFM帯以下の広い周波数帯域にわたってほぼ一定になるようにした。

(もっと読む)

受光回路、受光アンプ回路、フォトカプラ

【課題】従来技術では、回路規模の削減が難しかった。

【解決手段】反転増幅器の入出力間に帰還抵抗を接続した第1の増幅回路と、前記第1の増幅回路と実質的に同様な構成を備え、前記第1の増幅回路のバイアス電流を供給する第2の増幅回路と、アノードが前記第1の増幅回路の入力に接続され、カソードが前記第2の増幅回路の入力に接続されるフォトダイオードと、前記第2の増幅回路の出力と、前記第1の増幅回路の入力との間に接続される第1の抵抗と、を有する受光回路。

(もっと読む)

演算増幅器

【課題】少ない追加素子数で消費電流を増加させることなく出力ソース電流の出力能力の向上を図る共に、特に、出力ソース電流が出力される際の入力オフセット電圧の増加を抑制可能とする。

【解決手段】入力信号に対して差動増幅を行う差動増幅回路101と、この差動増幅回路101の出力を電圧・電流変換して出力するプリドライバ回路103と、このプリドライバ回路103の出力により駆動されるプッシュプル出力段106とを有してなる演算増幅器であって、プリドライバ回路103を構成するプリドライバ用トランジスタ3のベース電流を補償する補償電流供給回路104が設けられ、出力ソース電流の最大値の増加と共に、入力オフセット電圧の増加が抑圧されるものとなっている。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

バイアス発生器

【課題】トランジスタなどのデバイスにバイアス電圧を供給するバイアス発生回路であって、電流消費を最小化し、かつ、性能を最大化するバイアス発生器を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを備えたバイアス発生器であって、第2のトランジスタの制御ポートは第1のトランジスタの制御ポートと第2のトランジスタの入力ポートに接続され、第1のトランジスタを流れる第1の電流よりも第2のトランジスタを流れる第2の電流が大きい。同等のサイズを有する2つのトランジスタに異なる大きさの電流を供給することによって、バイアス発生器を流れる電流が最小化される。

(もっと読む)

全二重伝送回路、及び電子機器

【課題】消費電力を低減すること。

【解決手段】送信信号が入力される第1の内部入力端子と、送信信号に比べて振幅が1/2であり、かつ、送信信号と同相の信号が入力される第2の内部入力端子と、特性インピーダンスZを有する伝送路に接続された外部入出力端子と、外部入出力端子から入力された受信信号が出力される内部出力端子と、ソースが電流源及び外部入出力端子に接続され、ゲートが第1の内部入力端子に接続され、ドレインが第2のMOSトランジスタのソース及び内部出力端子に接続された第1のMOSトランジスタと、ソースが第1のMOSトランジスタのドレイン及び内部出力端子に接続され、ゲートが第2の内部入力端子に接続された第2のMOSトランジスタと、を備え、第1及び第2のMOSトランジスタのトランスコンダクタンスが1/Zとなる、全二重伝送回路が提供される。

(もっと読む)

低雑音増幅器

【課題】製造上の素子の特性ばらつきや電源電圧の変更やばらつきに対しても安定化させる。

【解決手段】入力端子2と、入力端子に入力された入力信号を増幅するトランジスタ1と、トランジスタの出力信号を出力する出力端子3と、トランジスタの出力信号の帰還量として振幅を調整して出力する帰還量調整回路10と、トランジスタに供給されるバイアス電流を生成するバイアス回路9と、帰還量調整回路の出力電圧と参照電圧とを比較して入力信号が前記トランジスタの利得抑圧を発生させることを判定したときトランジスタのバイアス電流を増加させるようにバイアス回路を動作させる差動電圧比較器11と、参照電圧を生成して差動電圧比較器の一方の入力端に印加させる第1の第1の入力バイアス回路12と、帰還量調整回路の出力電圧にバイアス電圧を付加して差動電圧比較器の他方の入力端に印加させる第2の第2の入力バイアス回路13と、を備える低雑音増幅器。

(もっと読む)

定電流回路

【課題】外付け抵抗の接続に不良が発生しても、正常な出力電流を得ることのできる定電流回路を提供する。

【解決手段】実施形態の定電流回路は、半導体集積回路に搭載され、出力電流を生成するカレントミラー回路103を備え、外部端子102に外付け抵抗Rextを接続することにより、カレントミラー回路103へ供給する基準電流Isが生成される定電流回路であって、オープン状態検出回路1が、外部端子102がオープン状態となったことを検出すると、代替回路2が、基準電流Isに相当する代替電流Iaをカレントミラー回路103へ供給する。

(もっと読む)

電流共有増幅器を用いた信号増幅

【課題】電流共有増幅器を用いた信号増幅を提供する。

【解決手段】電力増幅器は増幅段を有する。増幅段はトランジスターを有する。また少なくとも1つの増幅段は駆動段を有する。増幅段は、第1のトランジスターと有し及び第1の出力電力と関連付けられた第1の増幅段、並びに第2の出力電力と関連付けられた第2のトランジスターを有する第2の増幅段、を有する。電流共有結合は、第1の増幅段と第2の増幅段を結合する。第1の増幅段と第2の増幅段は、電流共有結合を通じて電流を共有する。電流共有結合は、第1の出力電力と第2の出力電力のスケーリングを助ける。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子及びアノードに接続されている端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子及びアノードに接続されている逆相信号処理回路と、を備える。正相信号処理回路は、正相信号Vinpに応じて、駆動電流を増加するように制御し、逆相信号処理回路は、逆相信号Vinnに応じて、駆動電流を減少するように制御する。

(もっと読む)

電圧電流変換回路

【課題】0VからVDDの範囲でダイナミックに変化する差動入力電圧の全ての入力電圧範囲において出力電流を変化させることができる電圧電流変換回路を提供する。

【解決手段】電圧電流変換回路は、第1および第2の負荷抵抗と第1の電流源との間に接続された第1および第2のMOSトランジスタと、第1および第2の負荷抵抗と第2の電流源との間に接続された第3および第4のMOSトランジスタとを備える。第1および第4のMOSトランジスタのゲートには差動入力電圧の一方および他方が入力され、第2および第3のMOSトランジスタのゲートにはバイアス電圧が入力される。バイアス電圧は、差動入力電圧のいずれかが電源電圧のときを除いて第2および第3のMOSトランジスタの両方がオンする電圧に設定されている。

(もっと読む)

増幅装置

【課題】直流電圧が含まれていることを検出する検出部がアンプ回路にとって負荷として機能しない増幅装置を提供する。

【解決手段】増幅装置1は、電圧源V1から供給される電源電圧に基づいて、スピーカーの負側入力端に供給するための基準電圧を生成する基準電圧生成部2と、入力信号を増幅して、スピーカーの正側入力端に出力するアンプ回路A1と、第1閾値電圧と第2閾値電圧とを生成する閾値電圧生成部4と、基準電圧が第1閾値電圧以上である場合、又は、基準電圧が第2閾値電圧以下である場合にアンプ回路からの出力電圧に直流電圧が含まれることを示す信号を出力し、基準電圧が第1閾値電圧よりも小さく、かつ、基準電圧が第2閾値電圧よりも大きい場合にアンプ回路からの出力電圧に直流電圧が含まれないことを示す信号を出力する検出部5とを備える。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

定電流回路

【課題】面積の小さい定電流回路を提供する。

【解決手段】高い抵抗値の抵抗によらず、強反転領域・非飽和領域で動作するNMOSトランジスタ23の高い抵抗値のオン抵抗により、定電流回路の定電流I1が少なくなる。よって、NMOSトランジスタ23の面積はこのトランジスタのオン抵抗の抵抗値と同じ抵抗値の抵抗の面積よりも小さいので、定電流回路の面積が小さくなる。

(もっと読む)

信号増幅装置、ブリッジ接続型信号増幅装置、信号出力装置、ラッチアップ阻止方法、及びプログラム

【課題】ラッチアップを阻止することができる信号増幅装置、ブリッジ接続型信号増幅装置、信号出力装置、ラッチアップ阻止方法、及びプログラムを提供する。

【解決手段】電源配線VDDに過電流が流れた場合、PMOSトランジスタ12を導通状態にすると共にNMOSトランジスタ14を非導通状態にするように制御してから反転増幅回路102をパワーダウンさせるように制御し、接地配線GNDに過電流が流れた場合、PMOSトランジスタ12を非導通状態にすると共にNMOSトランジスタ14を導通状態にするように制御してから反転増幅回路102をパワーダウンさせるように制御する。

(もっと読む)

電子回路

【課題】低電源電圧を用いて高性能な電子回路を提供すること。

【解決手段】信号が入力される制御端子と第1端子と第2端子とを有する第1トランジスタT1と、第1トランジスタの第2端子が接続された制御端子と第1端子と第2端子とを有する第2トランジスタT2と、第2トランジスタの第2端子が接続された制御端子と第1端子と第2端子とを有する第3トランジスタT3と、第2および第3トランジスタの少なくとも一方における第1および第2端子間を経由し、経由したトランジスタよりも前段に位置するトランジスタの第2端子に直流電流を供給する第1直流経路31と、第2および第3トランジスタの少なくとも一方における第1および第2端子間を経由し、経由したトランジスタよりも前段に位置するトランジスタの第2端子に直流電流を供給する第1直流経路とは異なる第2直流経路32と、第1および第2直流経路の間を共通に接続する共通接続点N1と、を具備する電子回路。

(もっと読む)

光受信回路用のトランスインピーダンスアンプ

【課題】電源電圧の変動に関わらず、クロスポイントのシフト幅を安定させることが可能な光受信回路用のトランスインピーダンスアンプを提供する。

【解決手段】TIA15は、互いに直列に接続された負荷抵抗23、入力FET22及びカスコードFET21を含み、入力FET22のゲート端子が入力端15aに接続された入力部20と、互いに直列に接続されたソースフォロワFET31及び電流源FET33を含み、ソースフォロワFET31のゲート端子にカスコードFET21のドレイン電圧を受けるとともに、ソースフォロワFET31のソース端子が帰還抵抗34を介して入力端15aに接続されたソースフォロワ部30と、電流源FET33のゲートバイアスを生成するバイアス生成部40とを備える。電流源FET33を流れる電流は、電源電位線18における電源電圧の大きさに基づいて可変とされている。

(もっと読む)

定電流回路

【課題】より低い電源電圧で動作できる定電流回路を提供する。

【解決手段】電源電圧VDDがディプレッション型NMOSトランジスタ10のドレイン・ソース間電圧Vds10とNMOSトランジスタ15のゲート・ソース間電圧Vgs15との加算電圧よりも高ければ、定電流回路は動作できる。定電流回路の電源電圧VDDとして、1つのドレイン・ソース間電圧と1つのゲート・ソース間電圧との加算電圧が必要になり、1つのドレイン・ソース間電圧と2つのゲート・ソース間電圧との加算電圧は必要ならないので、定電流回路の最低動作電源電圧が低くなる。

(もっと読む)

61 - 80 / 988

[ Back to top ]