Fターム[5J500AQ02]の内容

Fターム[5J500AQ02]に分類される特許

41 - 60 / 186

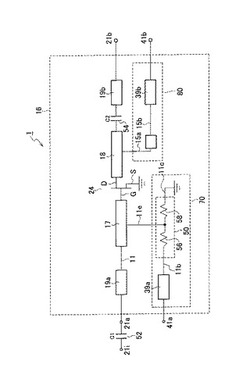

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

バイアス回路、電力増幅器及びカレントミラー回路

【課題】低電圧でも動作し、ドレイン電圧の変化を反映させた電流を制御できるバイアス回路を提供する。

【解決手段】オペアンプBIASの出力をゲート端子に入力するFETM3のドレイン端子電流をオペアンプBIASの入力端子に帰還する第1のカレントミラー回路CM1と第2のカレントミラー回路CM2を並列に接続する。第1のカレントミラー回路CM1には可変電圧を接続し、第2のカレントミラー回路CM2には固定電圧を接続する。可変電圧の値が、第1のカレントミラー回路CM1を構成するFETの閾値電圧以下となっても、第2のカレントミラー回路CM2により確実にオペアンプBIASの入力端子に電流を帰還する。

(もっと読む)

ソースフォロア増幅器

【課題】 入力電圧レベルに関わらず、ソースフォロアトランジスタの閾値電圧を一定に保つことができるソースフォロア増幅器を提供すること。

【解決手段】 入力MOSFETの基板ノードと出力ノードとの間を、入力電位に関わらず、非零の一定電圧に保つ手段を有するソースフォロア増幅器において、上記手段は、入力MOSFETの出力ノードと第1の参照電圧源との間に設けられた第1のスイッチ素子と、該入力MOSFETの基板ノードと第2の参照電圧源との間に設けられた第2のスイッチ素子と、該入力MOSFETの基板ノードと出力ノードとの間に設けられた容量素子であって、入力MOSFETの動作時間の内の、校正時間には該第1及び第2のスイッチ素子を短絡し、使用時間には該第1及び第2のスイッチ素子を開放することを特徴とするソースフォロア増幅器。

(もっと読む)

積層二重インダクタ構造

半導体素子の駆動回路、および駆動回路を有する半導体装置

【課題】本発明は、ゲート−ソース間において所定電圧を超えると急峻な電流が流れるダイオード特性を示す半導体素子の高負荷時の消費電力低減および駆動回路の低負荷時の損失低減を図るだけでなく、過電圧、過電流、過消費電力を防止する保護機能と、当該半導体素子の損失を低減する機能を有する駆動回路の提供を目的とする。

【解決手段】駆動回路におけるゲート制御手段(2,12,22,32)は、ゲート−ソース間において所定電圧を超えると急峻な電流が流れるダイオード特性を示す半導体素子(1)の動作状態を検出する動作状態検出手段(4,5,6)から入力された半導体素子の動作状態を示す信号に応じて、半導体素子のゲートに供給する電圧または電流を制御するよう構成されている。

(もっと読む)

電流センサを用いた平面オーディオ増幅器出力インダクタ

第1回路基板の層上に形成された第1複数巻線と、第2回路基板上の層に形成された第2複数巻線とを備えた平面インダクタ構造を有するオーディオ増幅器。前記平面インダクタ構造は、センサ巻線をさらに備えてもよい。  (もっと読む)

(もっと読む)

光増幅回路及びフォトカプラ

【課題】エピ−サブ構造のフォトダイオードを用いた受光増幅器において、寄生容量に起因する充放電電流による影響を除去する。

【解決手段】光増幅回路は、エピ−サブ構造のフォトダイオードPDと、前記PDから出力される電流を電圧に変換するI/V変換回路101と、前記PDと前記I/V変換回路101との間で、前記PDから出力される電流から前記PDの寄生容量に起因する充放電電流を除去する補正回路とを備える。前記補正回路は、前記寄生容量に対応する容量を有するコンデンサC101を備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法、及びヘテロ接合バイポーラトランジスタを用いた電力増幅器

【課題】InGaPをエミッタ層として有し、熱的安定性と通電に対する信頼性を両立することの出来るHBTを用いた電力増幅器を提供する。

【解決手段】InGaPエミッタ層を有するHBTにおいて、InGaPエミッタ層5とAlGaAsバラスト抵抗層7の間にGaAs層6を挿入し、ベース層4から逆注入された正孔がAlGaAsバラスト抵抗層7まで拡散、到達することを抑制する。

(もっと読む)

トランスインピーダンスアンプ

【課題】低容量でオン抵抗が低いMOSトランジスタを用いたトランスインピーダンスアンプを実現する。

【解決手段】トランスインピーダンスアンプの利得切替回路を構成するMOSトランジスタに、半導体基板に対して外部から任意の電位を印加するためのバックゲート端子を設け、MOSトランジスタの動作状態やそのときのドレイン電位やソース電位に応じた電位をバックゲート端子から半導体基板に対して任意の電位を印加する。

(もっと読む)

信号合成分配回路、電力増幅器および信号合成分配回路の製造方法

【課題】 簡単な構造で枝回路間の位相ずれによる利得低下を防止可能な信号合成分配回路を提供する。

【解決手段】 本発明の信号合成分配回路10は、基板11に、信号合成点または信号分配点14を有する複数の枝回路12a、12bおよび12cが配線され、前記複数の枝回路の少なくとも1本の枝回路12bが、他の枝回路12aおよび12cと異なる線路長であり、前記異なる線路長の枝回路12bの一部または全部15が、前記基板11中に配線されていることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】回路ゲイン切り替え時における入力端子の入力容量値の変動を低減し、周波数依存性を大幅に改善する。

【解決手段】スイッチ22(0〜N),23(0〜N),24(0〜N)におけるON/OFFの動作制御は、ロジックコントローラから出力される制御信号Ctrl0〜Ctrln,CtrlB0〜CtrlBnによってそれぞれ制御される。スイッチ24(0〜N)は、スイッチ22(0〜N)がON(トランジスタ19(0〜N)がバイアスオフ)する際に、同じタイミングでONとなり、スイッチ22(0〜N)がOFF(トランジスタ19(0〜N)がバイアスオン)する際には、同じタイミングでOFFとなる。トランジスタ24(1〜N)がバイアスオフのときに静電容量素子25(0〜N)が有効になり、回路ゲインを切り換えた時の入力端子INから見た入力容量値Cinの大きな変動を防止することができる。

(もっと読む)

参照電圧発生回路および受信回路

【課題】 電源電圧依存性および温度依存性の低い参照電圧発生回路を提供し、もって受信感度の良好な受信回路を実現する。

【解決手段】 受信回路は、AMI符号化された一対の信号を増幅する差動増幅回路(11)と、差動増幅回路の出力と所定の参照電圧とを比較して入力信号の論理レベルを判別する受信データ判定回路(12)と、前記参照電圧を発生する参照電圧発生回路(13)とを備え、参照電圧発生回路は電源電圧を基準にした温度依存性の低い参照電圧を発生するように構成した。

(もっと読む)

アナログ回路及び半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることを課題の一つとする。

【解決手段】チャネル形成層としての機能を有し、水素濃度が5×1019(atoms/cm3)以下であり、電界が発生していない状態においては、実質的に絶縁体として機能する酸化物半導体を有する薄膜トランジスタを用いてアナログ回路を構成することで、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることができる。

(もっと読む)

変圧器電力合成器

【課題】複数の入力ポートと少なくとも1つの出力ポートとを備え、高い変圧器結合効率及び高い電力合成効率を達成するオンチップ変圧器電力合成器を提供する。

【解決手段】変圧器電力合成器は、複数の一次巻線導体と複数の二次巻線導体とを含む。一次巻線導体は、入力ポートにそれぞれ電気的に接続される。加えて、各一次巻線導体は対応する入力ポートのプラス端子とマイナス端子との間に電気的に接続されている。二次巻線導体は、一次巻線導体にそれぞれ磁気的に結合される。二次巻線導体は、出力ポートのプラス端子とマイナス端子との間に直列接続及び並列接続を含むトポロジー構造を持つように構成される。

(もっと読む)

マイクロ波高調波処理回路

【課題】電力効率を向上できるマイクロ波高調波処理回路。

【解決手段】入力端子がトランジスタの出力端子に接続され、所定の電気長を有する直列伝送線路T11の出力端子に1点で並列接続され2次以上でn次(nは任意の整数)までの高調波に対してそれぞれが所定の電気長を持つ異なる長さの(n−1)個の並列先端開放スタブT21〜T26、直列伝送線路と(n−1)個の並列先端開放スタブの内の2つの並列先端開放スタブT25,T26が1つの接続点で接続されて構成された第1ストリップ導体7、(n−3)個の並列先端開放スタブT21,T22,T34,T24が1つの接続点で接続されて構成された第2ストリップ導体3、第1ストリップ導体と第2ストリップ導体との間に配置された接地層5、第1ストリップ導体の接続部20と第2ストリップ導体の接続部22とを電気的に接続するビア10を有する。

(もっと読む)

半導体装置

【課題】オッドモード発振を抑制し、またガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】第1の能動素子FET1と、第1の能動素子FET1に並列接続される第2の能動素子FET2と、第1の能動素子FET1のゲートG1と第2の能動素子FET2のゲートG2間に接続され、ゲートバイパス抵抗Rg0、ゲートバイパスキャパシタCg0、およびゲートバイパスインダクタンスLg0の並列回路からなる第1の安定化回路120とを備え、第1の安定化回路120の共振周波数は、オッドモード共振周波数に等しいことを特徴とする半導体装置。

(もっと読む)

高周波回路チップを実装した電子装置

【課題】広帯域に渡りインピーダンス整合する接続構造を実現すること。

【解決手段】高周波回路チップ100と伝送線路Fとの間に、高周波回路チップに対してワイヤボンディングされ、誘電体上に形成された第1信号線路61Lと、誘電体上において第1信号線路の両側に形成され、誘電体の裏面全体に形成された裏面接地導体と接続された、表面導体50Lの第1部分51Lから成る第1コプレーナ部Aと、第1コプレーナ部の第1信号線路に接続され、信号の伝送方向に沿った2辺に沿って、裏面接地導体と電気的に接続する複数のビアホールから成る側壁導体と、第1信号線路と連続する表面導体の第2部分と、裏面接地導体と、から成る集積導波管とを有する。第1信号線路と第2部分との接続点を、側壁導体間の幅の中点からずれた位置にすることで、この接続点から高周波回路チップ側を見たインピーダンスと集積導波管側を見たインピーダンスを等しくした。

(もっと読む)

半導体集積回路装置

【課題】面積の大幅な増大なくレファレンス電圧生成回路を低消費電流化するとともに通常動作モード時とスタンバイモード時においてレファレンス電圧精度の大幅な劣化を抑制する。

【解決手段】スタンバイモード時に、分周制御回路14は発振回路5が生成したクロックから、基準電圧発生回路3、基準電圧生成回路4、容量充電レギュレータ11のON/OFFを決めるイネーブル信号VREFONと基準電圧発生回路3、基準電圧生成回路4、ならびに容量充電レギュレータ11がONの際に、保持容量回路6内の保持容量CHに充電し、OFF期間に保持容量CHに対してリーク電流パス以外は存在しないように制御するサンプリング/ホールド信号CHOLDSWを生成する。消費電流の大きい基準電圧発生回路3、基準電圧生成回路4、容量充電レギュレータ11を間欠動作させて低消費電流化を図る。

(もっと読む)

高周波電力増幅回路およびその設計方法

【課題】高周波電力増幅回路の信頼性を向上させ、より大きな出力電力が取り出し、消費電力を減少させ、効率を向上させ、放熱コストを低減し、製品開発の時間短縮を可能とする。

【解決手段】トランジスタの中核的な部分である真性領域における負荷線(真性領域負荷線123)は、最適負荷線118と一致している。図6では見やすいようにわずかにずらしてある。つまり、真性領域負荷線123は、最適負荷線118と電流電圧の各軸を辺とする三角形の領域内にある。この領域では、トランジスタに対するバイアスストレスが少なく、トランジスタの信頼性向上等が可能となる。

(もっと読む)

41 - 60 / 186

[ Back to top ]