Fターム[5J500DN22]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | エミッタ(ソース)回路構成 (671) | エミッタ(ソース)直結構成 (199)

Fターム[5J500DN22]に分類される特許

1 - 20 / 199

半導体装置

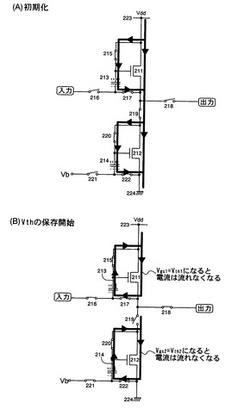

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

演算増幅器

【課題】消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転を防止する。

【解決手段】入力部10の反転入力端子100と第2のトランジスタ2のコレクタとが第1のダ入力部用イオード11を介して、非反転入力端子200と第1のトランジスタ1のコレクタとが第2の入力部用ダイオード12を介して、それぞれ接続される一方、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と反転入力端子100とが第5のダイオード15を介して、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と非反転入力端子200とが第6のダイオード16を介して、それぞれ接続されて、消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転が防止されるようになっている。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

信号平均化回路

【課題】信号の平均化値のずれを抑制した信号平均化回路を提供する。

【解決手段】キャパシタCa1の正端子に接続され、キャパシタCa1への信号の入力を制御するスイッチング素子S9と、キャパシタCa2の正端子に接続され、キャパシタCa2への信号の入力を制御するスイッチング素子S10と、キャパシタCa1とキャパシタCa2の正端子同士とを接続する平均化スイッチ素子S13と、を備え、パワーオフ期間後にキャパシタCa1に信号を入力することにより充電を行うプリチャージ期間と、プリチャージ期間後に、キャパシタCa2に信号を入力することにより充電を行う第1サンプリング期間と、第1サンプリング期間後にキャパシタCa1に信号を入力することにより再充電を行う第2サンプリング期間と、前記第2サンプリング期間後にキャパシタCa1,Ca2の正端子同士を接続した状態とする平均化期間と、を設ける。

(もっと読む)

増幅器

【課題】増幅器の出力雑音電圧を抑制する。

【解決手段】正転入力電圧と反転入力電圧の差分を増幅する差動入力回路1と、差動入力回路1の出力信号を増幅して出力端子に出力する出力回路2と、差動入力回路1の電流源MP3と出力回路2の電流源MP4にバイアス電圧を出力するバイアス回路5を備えた増幅器である。差動入力回路1の正転入力電圧と反転入力電圧が共に接地電圧のときに出力端子に現れる出力雑音電圧を検出し、該雑音電圧のレベルが高いほど、バイアス回路5が、電流源MP3,MP4の電流を増大させるバイアス電圧を出力するようにした。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

差動増幅回路及びコンパレータ

【課題】オフセット電圧の変動を低減した差動増幅回路及びコンパレータを提供する。

【解決手段】実施形態によれば、差動回路と、出力回路と、クリップ回路と、を備えたことを特徴とする差動増幅回路が提供される。前記差動回路は、一対の入力信号の電位差に応じた一対の差動電流を生成する。前記出力回路は、前記一対の差動電流を受けて、電流差に応じた出力電圧を生成する。前記クリップ回路は、前記出力電圧に応じてオンし、前記出力電圧をしきい値電圧を含みローレベルまたは前記ローレベルよりも高いハイレベルに変換できる範囲に抑制するクリップ素子を有する。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

電子回路及び光受光回路

【課題】 入出力信号のオフセットを補償して、入力電流が増大しても増幅動作を行うことができる電子回路及び光受光回路を提供する。

【解決手段】 本発明の電子回路30は、相補的な入力電流を、相補的な電圧信号に変換して出力する差動トランスインピーダンスアンプ10と、出力を入力し、出力が差動トランスインピーダンスアンプ10の入力に接続される差動回路18であって、差動回路18の電流源Is5が入力電流の平均値I2に基づいて制御される差動回路18と、を備えることを特徴とする。

(もっと読む)

オフセット調整差動増幅回路

【課題】オフセット調整差動増幅回路において、オフセット調整値を温度に対して安定して維持することを提供する。

【解決手段】オフセット調整差動増幅回路は、差動対を構成する第1、第2のMOSトランジスタM1、M2と、第1のMOSトランジスタM1のソースに一端が接続される第1の抵抗R1と、第2のMOSトランジスタM2のソースに一端が接続され、第1の抵抗R1の他端に他端が接続される第2の抵抗R2と、第1、第2の抵抗R1、R2の接続点と第1の電源端子との間に接続され、差動対の動作電流を供給する電流源M6と、第1のMOSトランジスタM1のソースにソースが接続され、第2の電源端子にドレインが接続され、ゲートにオフセット調整電圧VTが与えられ、第1の抵抗R1の両端に生じる電圧を調節するオフセット調整電流I7をオフセット調整電圧VTに応じて制御する第3のMOSトランジスタM7と、を有する。

(もっと読む)

差動信号発生回路および電圧制御ゲイン可変増幅器

【課題】電圧制御によりゲイン調整を行うゲイン可変増幅器制御用の制御電圧を、基準電圧を用いることなく生成し、電圧制御ゲイン可変増幅器全体の小型化および消費電力の削減を図る。

【解決手段】ゲイン可変増幅器制御回路を構成する差動対として、nチャネル型トランジスタTR11とpチャネル型トランジスタTR12とを用い、共通のゲイン制御電圧S1をこれらトランジスタTR11およびTR12のゲートに供給する。各トランジスタTR11、TR12を流れる電流は、ゲイン制御電圧S1が増加するにつれて一方は増加し、他方は減少する特性となり、基準電圧を用いたゲイン可変増幅器制御回路と同一特性のゲイン可変増幅器制御電圧を得ることができる。よって、基準電圧発生回路を設ける必要がないため、装置全体の小型化および消費電力の削減を図ることができる。

(もっと読む)

利得可変差動増幅回路

【課題】広いダイナミックレンジを確保しつつ利得を変化させることが可能な利得可変差動増幅回路を提供すること。

【解決手段】この利得可変差動増幅回路12は、差動対トランジスタQ1,Q2,Q3,Q4とそれらのトランジスタのそれぞれのコレクタに接続された負荷抵抗14,15,18,19とそれらのトランジスタのエミッタに共通に接続された電流源16,20とをそれぞれ含む差動増幅回路17,21を有し、次段差動増幅回路21の出力を、帰還トランジスタQ5,Q6を介して初段差動増幅回路17に帰還させる利得可変差動増幅回路において、該初段差動対トランジスタQ1,Q2を流れるべき電流を分岐させる電流分岐回路部12Cと、差動対トランジスタQ1,Q2に電流を供給する電流供給回路部12Bとを備える。

(もっと読む)

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

受信回路並びにそれを備えた半導体装置及び情報処理システム

【課題】 本発明は、低速信号よりも高速信号を増幅し、かつ、消費電力を抑える受信回路並びにそれを備えた半導体装置及び情報処理システムを実現することを目的とする。

【解決手段】 本発明の受信回路並びにそれを備えた半導体装置及び情報処理システムは、第1の増幅器と、第1の増幅器よりもカットオフ周波数の低い第2の増幅器とを有し、第1の増幅器及び第2の増幅器に受信信号を入力し、第1の増幅器の出力から第2の増幅器の出力を減じて出力する。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

電流源回路

【課題】回路面積が小さな電流源回路を提供する。

【解決手段】この電流源回路では、直流電圧V1に応じた値の参照電流I1を生成し、その電流I1のうちの電流IrをダイオードD1に流し、残りの電流I1−IrをダイオードD2に流し、ダイオードD1,D2のアノードの電圧VR1,VR2を差動増幅回路のトランジスタQ1,Q2のベースに与える。また、直流電圧V2に応じた値の参照電流I2を生成し、その電流I2を差動増幅回路の駆動電流とする。トランジスタQ1のコレクタに流れる定電流Io=Ir・(V2/V1)が電流源回路の出力電流Ioとなる。したがって、外付け用の端子および外部抵抗器が不要となる。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

1 - 20 / 199

[ Back to top ]