Fターム[5K029DD04]の内容

直流方式デジタル伝送 (8,390) | 伝送システム構成 (1,787) | 伝送路の位置の特定 (385) | ユニット間インタフェース (383) | 基板間、IC間インタフェース (103)

Fターム[5K029DD04]に分類される特許

1 - 20 / 103

半導体システムのための無線信号送受信装置、無線信号送信方法、及び無線信号受信方法

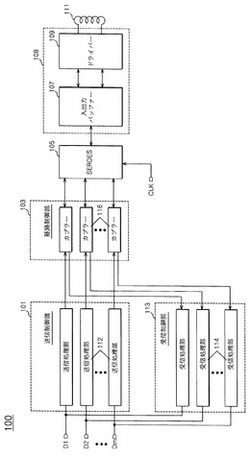

【課題】本発明は、制限された面積から充分なインダクタンスを確保して安定的に送受信できる半導体システムのための無線信号送受信装置を提供することを目的とする。

【解決手段】無線信号送受信装置100は、並列入力信号を直列信号に変換して出力し、直列入力信号を並列信号に変換して出力するサーデス信号およびサーデス回路105から出力される直列信号によりインダクタンスを発生し、外部装置と誘導結合現象によって発生した信号をサーデス回路105の直列信号に提供するカップリングパッド111を備える。

(もっと読む)

半導体集積回路及びそれを備えた駆動装置

【課題】絶縁素子を介した信号伝達に誤動作を生じさせ得る異常を検出して制御対象に停止信号をすることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、外部から供給される送信データVINに応じた送信信号を生成し出力する送信回路Tx1と、受信信号に基づいて送信データVINを再生する受信回路Rx1と、送信回路Tx1と受信回路Rx1とを絶縁するとともに、送信信号を受信信号として伝達する絶縁素子ISO1と、絶縁素子ISO1を介した信号伝達に誤動作を生じさせ得る異常を検出する異常検出部DT1と、異常検出部DT1により異常が検出された場合には、外部から送信回路Tx1に供給される送信データVINに関わらず停止信号を出力する制御部CT1と、を備える。

(もっと読む)

電子機器

【課題】基板接続用のスロット位置の変更等によって伝送距離が変わった場合でも、必要なパラメータ設定を比較的簡単に判別し再設定する。

【解決手段】電子回路基板13iがマザーボード10の任意のフリースロットに装着された初期状態で、電子回路基板13iは、監視制御部B4にて送受信回路部B1の受信状態を監視して、当該受信状態が規定状態となるようにパラメータ設定部B3に送受信回路部B1の受信パラメータを変更させ、受信状態が規定状態とならない場合にはその旨をホスト制御基板11に通知する。当該ホスト制御基板11は、スイッチ処理基板12に、電子回路基板13iの受信状態が規定状態となるように送信パラメータの変更を指示する。スイッチ処理基板12の監視制御部C4は、ホスト制御基板11からの指示に応じてパラメータ設定部C3に送受信回路部C1の送信パラメータを変更させる。

(もっと読む)

データ送信機,データ受信機およびデータ送受信システム

【課題】消費電流および占有面積の増加を抑えて、設計自由度の向上および高速データ伝送を行うことができるデータ送受信システムを提供する。

【解決手段】予め特定の位相ずれた2ビットのパラレルデータD0,D1を排他的論理和演算してシリアルデータを出力する送信データ生成部10を有する。受信部は、データ送信機から排他的論理和演算して送られたシリアルデータにおける任意の第1データと、該第1データの1ビット直前に排他的論理和演算を行った第2データとの排他的論理和演算を行って受信データを生成する受信データ生成部を有する。

(もっと読む)

1線式シリアルインターフェース

【課題】入力逆流防止回路の寄生抵抗成分による電圧降下により入力電圧識別回路の誤動作を減少させ、メモリ回路へのメモリ誤書き込みを減少させる1線式シリアルインターフェースを提供する。

【解決手段】 1線式シリアルインターフェースは、1本の信号線によりシリアルデータの受信を可能とし、入力端子1に接続された2つのPMOSトランジスタから構成された入力逆流防止回路2と、抵抗分圧器5及び電圧比較回路6から構成された入力電圧識別回路3と、1端が電源に接続されたプルアップ抵抗R1が設けられた電源供給線4とを有する。入力逆流防止回路2の2つのPMOSトランジスタは、ゲート同士が接続され、一方のソースが他方のドレインに接続されている。即ち、入力端子1、入力電圧識別回路3、入力逆流防止回路2、プルアップ抵抗R1の順に配列されている。

(もっと読む)

信号伝送回路

【課題】低コストかつ実装密度が高い回路基板を用いて、信号線間のクロストークノイズを低減するとともに、スタブによる反射ノイズを低減することのできる信号伝送回路を提供する。

【解決手段】本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品を接続する第2配線間に、第1電子部品を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

(もっと読む)

差動伝送回路、光送受信モジュール、及び情報処理装置

【課題】差動伝送線路が屈曲領域を有する場合にも、2つの差動信号に生じる遅延時間差が抑制されるとともに、高密度な実装を可能とする、差動伝送線路、並びに、それを用いた光送受信モジュール及び情報処理装置の提供。

【解決手段】本発明に係る差動伝送線路は、1対の伝送線導体と、1対の伝送線導体と対向する領域を含んで外方に広がる接地導体層とを備える、差動伝送線路であって、1対の伝送線導体は、第1の幅で互いに平行して第1の方向に延伸するとともに第1の一層上に形成される、第1の直線領域と、1対の伝送線導体の一方は第1の層上に形成され、他の一方は第2の層に形成され、1対の伝送線導体が立体的に交差するとともに、第1の直線領域の前方に配置される第1の交差領域と、を含み、第1の交差領域における1対の伝送導体の幅それぞれは、ともに前記第1の幅より小さい、ことを特徴とする。

(もっと読む)

通信システム及びそのデバイス

【課題】1本の信号線を用いて双方向のシリアル通信を行う通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11と第2デバイス12間を1本の信号線で接続し、互いにレベルの異なる第1レベルと第2レベル、及び前記第1レベルと第2レベルの中間レベルを用いてシリアル通信を行う通信システムであって、第1デバイスは、第1レベルと中間レベルを繰り返すことで第2デバイスにクロックを送信し、第2デバイスは、受信したクロックの中間レベルの期間に第2レベルを出力するか否かで第1デバイスに情報を送信し、第1デバイスは、第2デバイスが情報を送信していない場合に、クロックの中間レベルの期間に第2レベルを出力するか否かで前記第2デバイス12に情報を送信する。

(もっと読む)

電子回路

【課題】簡易な構成でありながら正確に同期したクロックを各基板に分配することができる電子回路を提供すること。

【解決手段】第1コイルL1と第1キャパシタC1による第1共振回路を含む第1発振器21を有する第1基板11と、第2コイルL2と第2キャパシタC2による第2共振回路を含む第2発振器22を有する第2基板12とを備え、前記第1コイルL1と第2コイルL2が誘導結合して前記第1発振器21と第2発振器22が結合共振することを特徴とする電子回路。

(もっと読む)

伝送回路、プリント回路基板

【課題】搭載する部品を回路毎に変更することなく、伝送経路の特性に合わせて回路の周波数特性を平滑化することのできる、低消費電力の伝送回路を提供する。

【解決手段】本発明に係る伝送回路は、信号伝送線に並列接続されたインダクタを有するパッシブイコライザを備え、インダクタは回路基板のスルーホール側面に形成された導体部分を用いて構成されている。

(もっと読む)

メモリ制御回路及びそれを用いたデータ伝送システム

【課題】送信機、受信機の双方において新たな入力端子を設ける必要がないデータ伝送システムを提供すること。

【解決手段】本発明に係るメモリ制御回路は、それぞれが第1及び第2の入力端子を備え、各前記第1の入力端子に外部メモリから受信したデータ信号が入力される複数のコンパレータと、前記外部メモリから受信した差動ストローブ信号の正相及び逆相の双方から、各前記第2の入力端子に入力される複数の基準電圧を生成する基準電圧発生回路と、を備えるものである。

(もっと読む)

判定帰還型波形等化器

【課題】直前ビットの受信判定データを利用することなく、第1ポストカーソルのISIを補正する判定負帰還型波形等化器を提供する。

【解決手段】判定帰還型波形等化器は、受信データを入力する増幅回路と、フリップフロップを含み、増幅回路の出力がフリップフロップに入力され、フリップフロップにより増幅回路の出力を判定するデュオバイナリ信号判定器と、フリップフロップに保持された判定結果を逐次シフトさせるシフトレジスタと、シフトレジスタの各出力を入力とし、出力を増幅回路の出力に帰還し、その電位を制御する複数の電流制御ブロックとを有し、フリップフロップに保持された判定結果をシフトレジスタでシフトさせることなく増幅回路の出力の出力に帰還しない。

(もっと読む)

受信装置

【課題】イコライザ内に設けられた複数の経路の遅延量を稼働時の条件に合わせて最適化可能な受信装置を提供する。

【解決手段】伝送路を介して入力される受信信号を複数の経路に分岐する分岐部と、分岐された複数の経路を介して入力される受信信号に対してそれぞれ異なる演算処理を適用する演算処理部と、各経路に対応して設けられ、対応する演算処理が為された信号をそれぞれサンプリングしてデジタル信号に変換するアナログ/デジタル変換部と、各経路に対応するアナログ/デジタル変換部で得られたデジタル信号を合成する信号合成部と、信号合成部で合成されたデジタル信号から受信信号で表されるデータを復元するための処理を行うデジタル信号処理部と、デジタル信号処理部で得られる復元データを最適化するように、各経路に対応するアナログ/デジタル変換部のサンプリングタイミングをそれぞれ調整するタイミング調整部とを備える。

(もっと読む)

バッファ回路およびそれを用いた半導体装置、出力回路および電子機器

【課題】高速信号を確実に伝送可能なバッファ回路を提供する。

【解決手段】電流源312は、定電流Icを生成する。第1トランジスタM1は、その一端が電流源312と接続され、その制御端子に入力信号SINが入力される。反転回路314は、入力信号SINを反転および遅延させ、反転入力信号SIN#を生成する。第2トランジスタM2は、その一端が電流源312と接続され、その制御端子に反転入力信号SIN#が入力される。バッファ回路310は、第1トランジスタM1および第2トランジスタM2の、電流源312と共通に接続された一端に生ずる信号SOUTを出力する。

(もっと読む)

半導体集積回路装置、インタフェース回路

【課題】EMIを低減する半導体集積回路、インタフェース回路を提供する。

【解決手段】半導体集積回路装置(100)は、抵抗値を切り替え可能な可変抵抗部(10)と、可変遅延部(20)と、データ取り込み部(26)とを具備する。抵抗値を切り替え可能な可変抵抗部(10)は、入力されるデータ信号(DT)をダンピングする。可変遅延部(20)は、データ信号(DT)の入力タイミングを示すクロック信号(CLK)に変更可能な遅延を与える。データ取り込み部(26)は、可変抵抗部(10)によってダンピングされた信号から可変遅延部(20)によって遅延された遅延クロック信号によって示されるタイミングでデータを取り込む。

(もっと読む)

伝送回路

【課題】近端クロストークノイズによる伝送品質劣化の影響を軽減する。

【解決手段】近接して配設される複数の伝送路50〜54のそれぞれを駆動するそれぞれのドライバ30〜34と、一のドライバの入力信号と他のドライバの入力信号とのそれぞれのレベル変化を検知する信号論理変化検知回路20〜24と、信号論理変化検知回路が検知したレベル変化に応じて一のドライバにおける駆動能力を変更するように制御するインピーダンス調整回路40〜44と、を備える。

(もっと読む)

通信インターフェース回路

【課題】本発明は、スレーブとマスターを容量結合しても、過渡応答の影響が少なく、データの判別の誤りが少ない、通信インターフェース回路を提供することを目的とする。

【解決手段】インターフェース部16に過渡応答補正部17を設ける。この過渡応答補正部17によって、容量結合に用いられるコンデンサによる過渡応答が軽減でき、誤りの少ないデータ通信を実現する。

(もっと読む)

送信回路、受信回路、送信方法、受信方法及び信号伝達システム

【課題】従来の信号伝達システムは、動作環境により論理判定に誤りが生じる問題があった。

【解決手段】本発明にかかる信号伝達システム1は、一次側コイル11、二次側コイル12、送信回路2、受信回路3を備える。一次側コイル11と二次側コイル12とは磁気的に結合される。送信回路2は、送信データに基づいて生成される送信信号の立ち上がりエッジ又は立ち下がりエッジに応じてドライブ回路21に駆動制御信号を出力するプリドライバ回路22と、駆動制御信号に応じて一次側コイル11に増加率と減少率とが非対称になる正の駆動電流又は負の駆動電流を供給するドライブ回路21とを有する。受信回路3は、送信信号により二次側コイル12に生じる受信信号の正の振幅と負の振幅との絶対値の差に応じた検出電圧を出力する受信信号検出回路31と、検出電圧と基準電圧との電圧差に基づいて送信データを再生するヒステリシスコンパレータ32とを有する。

(もっと読む)

バッファ回路

【課題】 消費電力を抑制することができるバッファ回路を提供すること。

【解決手段】 検波回路11が、入力信号IDのレベルに応じた入力レベル判定信号SWを制御回路9へ供給し、入力信号IDの振幅が比較的小さい場合には、制御回路9が、低レベル入力用回路6を選択して、トータルゲインを十分に上げ、入力信号IDの振幅が比較的大きい場合には、制御回路9が、高レベル入力用回路5を選択して、無用な消費電流の増大を抑制する。

(もっと読む)

半導体装置

【課題】動作用クロックの周波数にかかわらず、所要のビットレートに近いビットレートでシリアル通信を行えるようにする。

【解決手段】半導体装置は、所定の動作用クロックに従って動作するシリアルコミュニケーションインタフェース(109)を含む。上記シリアルコミュニケーションインタフェースに、上記動作用クロックをカウントし、それに基づいて、上記単位転送時間を規定するための基本クロックを生成するボーレートジェネレータ(202)と、生成された基本クロックに従って送受信制御を行うための送受信コントローラ(201)とを設ける。さらに上記シリアルコミュニケーションインタフェースに、上記動作用クロックの上記ボーレートジェネレータへの供給を部分的にマスクすることで所望のビットレートを実現可能なビットレートモジュレータ(203)を設けることで、所要のビットレートに近いビットレートでのシリアル通信を実現する。

(もっと読む)

1 - 20 / 103

[ Back to top ]