Fターム[5M024PP08]の内容

Fターム[5M024PP08]に分類される特許

1 - 20 / 46

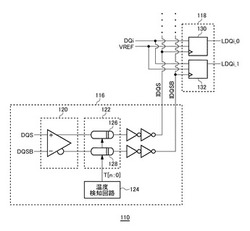

半導体装置およびそれを利用した情報処理システム

【課題】半導体装置において、温度変化によるデータのラッチタイミングの調整によって生ずるシステムのビジー期間を抑制しなければならない。

【解決手段】タイミング制御回路116は、任意の温度でデータDQiとストローブ信号がキャリブレーションによってマッチングされたストローブ信号DQS,DQSBを受信し、内部ストローブ信号IDQS、IDQSBを生成し、ラッチ回路118に出力する。ラッチ回路118は、内部ストローブ信号IDQS、IDQSBのエッジのタイミングでデータDQiをラッチする。タイミング制御回路116は、温度検知回路124と内部ストローブ信号IDQS、IDQSBの伝送経路に間挿され、温度検知回路124からの温度信号Tにしたがって、前記マッチングを維持するように内部ストローブ信号IDQS、IDQSBの時間変動を抑制する可変遅延回路122を含む。

(もっと読む)

温度情報出力装置の温度情報出力方法

【課題】温度情報出力装置の面積を増やさなくとも動作可能な温度範囲を増やすことができる、温度情報出力装置の温度情報出力方法を提供する。

【解決手段】温度を感知し、当該温度に対応する第1の電圧VTEMPを出力するステップと、第1の電圧VTEMPと第2の電圧DACOUTとを比較するステップと、この比較結果に基づいて、デジタルコードDIGITAL_CODEを加減するステップと、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTを生成するステップとを含み、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTの変化幅が温度区間別に異なる。

(もっと読む)

記憶素子の駆動方法及び半導体装置の駆動方法

【課題】記憶素子(DRAM)の保持情報の多値化を簡便に行うこと。

【解決手段】記憶素子(DRAM)が有するトランジスタがオン状態の期間において、当該記憶素子(DRAM)に対して情報の書き込みを行う配線(ビット線)の電位を変動させることで、当該記憶素子(DRAM)が有する容量素子に蓄積される電荷量を制御する。これにより、当該記憶素子(DRAM)を有する半導体装置の構造を複雑化せずとも記憶素子(DRAM)の保持情報を多値化することが可能である。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、ソース及びドレインの一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される第3の電界効果トランジスタと、を備える。

(もっと読む)

半導体装置

【課題】特定のトランジスタのゲートの電位に応じて記憶情報の判別が行われる半導体装置において、当該トランジスタのしきい値電圧のばらつきの低減と、長期間に渡る情報の保持とを両立することで情報の保持特性に優れる半導体装置を提供すること。

【解決手段】チャネル領域が酸化物半導体によって形成されるトランジスタのソース又はドレインのみに電気的に接続されるノードにおいて電荷の保持(情報の記憶)を行う。なお、当該ノードにソース又はドレインが電気的に接続されるトランジスタは、複数であってもよい。また、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

半導体装置

【課題】内部電源発生回路から生成される内部電源を受けて安定動作を図りつつ、消費電力を抑制する半導体装置を提供する。

【解決手段】制御回路12、ロウカラムデコーダ13およびセンスアンプ15は、アレイ電圧VddTで駆動する。一方、消費電力の大きいデータパス14は、外部電源電圧VddLで駆動する。そして、レベル変換回路17は、外部電源電圧VddLの電圧レベルをもつアドレス信号またはコマンド信号を受けて、その電圧レベルをアレイ電圧VddTに変換し、制御回路12へ出力する。また、レベル変換回路18は、制御回路12からアレイ電圧VddTの電圧レベルをもつ制御信号を受けて、その電圧レベルを外部電源電圧VddLに変換し、データパス14へ出力する。

(もっと読む)

半導体装置

【課題】オフリーク電流の温度特性が互いに異なる複数の回路ブロックに対して電源制御を行うことにより、消費電力を低減する。

【解決手段】オフリーク電流が第1の温度特性を有するトランジスタによって構成された第1のXデコーダ12と、オフリーク電流が第2の温度特性を有するトランジスタによって構成されたプリデコーダ13及び周辺回路14と、スタンバイ時において温度が第1のしきい値を超えている場合、Xデコーダ12を非活性化させる電源制御回路16と、スタンバイ時において温度が第2のしきい値を超えている場合、プリデコーダ13及び周辺回路14を非活性化させる電源制御回路17とを備える。本発明によれば、複数の回路ブロックに対する電源制御の有無を、互いに異なる温度を基準として判断していることから、各回路ブロックに対して最適な電源制御を行うことが可能となる。

(もっと読む)

半導体装置

【課題】相補電界効果トランジスタのオフ電流の周囲温度の変動に伴う変動を抑制する。

【解決手段】CMOSを構成するNチャンネルMOSトランジスタの基板電圧VPWを生成する基板電圧生成回路31と、上記NチャンネルMOSトランジスタのレプリカであり、かつダイオード接続されたレプリカトランジスタ32と、レプリカトランジスタ32のアノード−カソード間に所定の電圧値VFの電圧を印加する電圧印加部33とを備え、レプリカトランジスタ32の基板電圧は基板電圧生成回路31が生成する基板電圧VPWであり、基板電圧生成回路31は、レプリカトランジスタ32に流れる電流の電流値が所与の目標値となるよう、生成する基板電圧VPWを制御する。

(もっと読む)

半導体装置

【課題】MOSトランジスタのしきい値を調整するために基板電圧を制御しつつも、基板電圧を適切な範囲内に維持することを可能にする。

【解決手段】半導体装置1は、半導体基板に形成されたしきい値調整対象のMOSトランジスタと、該MOSトランジスタのレプリカトランジスタと、レプリカトランジスタが所与の設計値の電流を流すのに要するゲート−ソース間電圧をモニタするモニタ回路10と、モニタ回路10の出力に基づいて上記MOSトランジスタの基板電圧VBBを生成する負電圧ポンプ回路20と、基板電圧VBBが所定値を超えたことに応答して、モニタ回路10のモニタ結果にかかわらず負電圧ポンプ回路20の動作を規定するリミッタ回路30とを備える。

(もっと読む)

半導体装置

【課題】コストの増加を抑制しつつ、高いチューニング精度を維持するとともに、チューニングに要する時間の増加を抑制できる半導体装置を提供する。

【解決手段】レベルシフト回路5を構成する可変抵抗R1およびR2に加えて、BGR回路1のVBGR電圧の出力ノードと可変抵抗R1との間に接続された付加抵抗RUと、可変抵抗R2と基準電圧との間に接続された付加抵抗RDとを有し、付加抵抗RUおよびRDのそれぞれに並列して、Nチャネル型のMOSトランジスタTUおよびTDが接続されている。

(もっと読む)

システム装置およびシステム装置の動作方法

【課題】 半導体メモリのアクセス状況に応じて、半導体メモリのアクセスに伴い消費される電力を最小限にする。

【解決手段】 半導体メモリは、第1電源電圧に応じて動作する内部回路と第2電源電圧に応じて動作するメモリ入出力回路とを有し、クロック信号に同期して動作する。第1コントロール部は、半導体メモリをアクセスするために、メモリ入出力回路に接続され第2電源電圧に応じて動作する制御入出力回路を有し、クロック信号に同期して動作する。電圧生成部は、電圧調整信号に応じて第2電源電圧を変更する。クロック生成部は、クロック調整信号に応じてクロック信号の周波数を変更する。第2コントロール部は、第1コントロール部による半導体メモリのアクセス状況に応じて、半導体メモリの消費電力を最適にするために、電圧調整信号およびクロック調整信号を生成する。

(もっと読む)

1 - 20 / 46

[ Back to top ]