国際特許分類[G01R31/28]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767)

国際特許分類[G01R31/28]の下位に属する分類

限界試験,例.供給電圧を変えることによるもの (114)

非接触試験 (272)

アナログ回路の試験 (200)

アナログデジタル混在回路の試験

デジタル回路の試験 (638)

国際特許分類[G01R31/28]に分類される特許

101 - 110 / 4,543

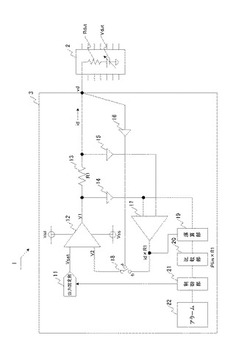

直流電流電圧源および半導体試験装置

【課題】直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【解決手段】本発明の直流電流電圧源3は、出力設定部11により設定された設定電圧Vsetを出力する出力アンプ12と、出力アンプ12が出力する出力電圧V1と出力アンプ12に帰還されて入力される入力電圧V2とを入力して、出力アンプ12の消費電力Pampを演算する演算部19と、演算部19により演算された消費電力Pampが予め設定された設定電力Plimを超過しているか否かを比較する比較部20と、消費電力Pampが設定電力Plimを超過しているときには、出力設定部11の設定値を低下させる制御を行う制御部21と、を備えている。

(もっと読む)

メモリシステム

【課題】

実施形態は、制御部をテスト可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、前記NAND型フラッシュメモリと前記入出力部との間、および前記NAND型フラッシュメモリと前記入力バッファ部との間に設けられた複数のデータバスと、入力される選択信号に基づいて、所望の前記データバスを選択するスイッチと、前記NAND型フラッシュメモリ、前記入出力部、及び前記スイッチを制御して、前記入力バッファ部から前記NAND型フラッシュメモリにデータを書き込むとき、選択された前記データバスを介して、前記NAND型フラッシュメモリと前記入力バッファ部との間を接続し、残りのデータバスを介して、前記NAND型フラッシュメモリと前記入力バッファ部との間を接続しない前記選択信号を前記スイッチに出力する制御部とを含む。

(もっと読む)

最適化されたJTAGインターフェイス

【課題】

集積回路内のJTAGタップドメインにアクセスするのに最適化されたJTAGインターフェイスが使用される。限定はしないが、シリアル通信関連集積回路テスト、エミュレーション、デバッグ、および/またはトレース操作等の多様なシリアル通信操作に対してインターフェイスを使用することができる。

【解決手段】

TDI入力端子、TCK入力端子、TMS入力端子、およびTDO出力端子を有し、TDO出力端子は集積回路の外部アクセス可能なデータ入出力ピンに接続されているIEEE 1149.1タップドメインと、集積回路の外部アクセス可能なデータ入出力ピンに接続されたシリアル入力端子、TDI入力端子に接続された第1のパラレル出力端子、およびTMS入力端子に接続された第2のパラレル出力端子を有するシリアル入力パラレル出力回路とを含む、集積回路。

(もっと読む)

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

半導体装置

【課題】

実施形態は、ベリファイ動作の誤判定を低減可能な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、メモリセルを含むメモリセルアレイと、ビット線と、センスアンプと、制御部とを備え、センスアンプは、外部から入力された第1又は第2テストデータと第1又は第2ページのメモリセルに保持された保持データとを比較するテスト工程で、第1テストデータと第1ブロックの第1ページに対応する保持データとを比較した後に、第1テストデータと第2ブロックの第1ページに対応する保持データとを比較し、第1テストデータとは異なる第2テストデータと第1ブロックの第2ページに対応する保持データとを比較した後に、第2テストデータと第2ブロックの第2ページに対応する保持データとを比較することを特徴とする。

(もっと読む)

半導体集積回路、スキャンフリップフロップ及び半導体集積回路のテスト方法

【課題】稼働中の故障診断の際に内部状態の退避及び復帰を図ることができるとともに、回路規模の増大を防ぐことが可能にする。

【解決手段】本発明に係る半導体集積回路10は、スキャンフリップフロップ210,310と、スキャン制御部100とを備え、スキャンフリップフロップ210は、スキャン制御部100の制御に基づいて、内部状態として保持しているバックアップデータを出力し、のスキャンフリップフロップ310は、スキャン制御部100の制御に基づいて、スキャンフリップフロップ210から出力されたバックアップデータを、スキャンフリップフロップ310内に保持するものである。

(もっと読む)

アナログデジタル変換回路、アナログデジタル変換回路の検査方法、撮像装置、撮像装置を有する撮像システム、撮像装置の検査方法

【課題】複数のメモリ間でのショート故障の有無を検査できる構成を有するADCおよびその検査方法、ADCを有する撮像装置、撮像装置を有する撮像システムを提供する。

【解決手段】複数のメモリと複数の比較器とを含んで構成される回路部を複数有し、アナログ信号をデジタル信号に変換するアナログデジタル変換回路であって、複数の回路部の一部に含まれるメモリと複数の回路部の別の一部に含まれるメモリとで異なるデジタル信号を保持するようにテスト信号を供給するテスト信号供給部と、出力比較部と、転送部を有することを特徴とするアナログデジタル変換回路である。

(もっと読む)

半導体試験装置における電気長測定方法

【課題】ウェハを対象とした半導体試験装置において、簡易にプローブ先端を接地状態として電気長測定を行なえるようにする。

【解決手段】試験対象のウェハと接触するプローブを複数備えた半導体試験装置における、プローブを一端とする信号経路の電気長測定方法であって、電気伝導性領域を有するキャリブレーションウェハの電気伝導性領域を全プローブに接触させ、信号経路の他端から測定信号を入力し、電気伝導性領域との接触部で反射した信号波形を他端側で測定することにより電気長を算出する。

(もっと読む)

集積回路および集積回路の接続不良検出方法

【課題】製品組立後の経年劣化による接続不良を含め、簡単な構成で被実装基板との接続不良を検出する。

【解決手段】集積回路に、同一の電位が与えられる2以上の比較電圧用パッドと、比較電圧用パッドにかかる電圧を比較して、その比較結果に基づいて被実装基板との接続不良の有無を示す信号を出力する比較判別回路とを設け、比較判別回路において、少なくとも2つの比較電圧用パッドにかかる電圧の電位差が所定の値を超えた場合に、接続不良を示す信号を出力させる。

(もっと読む)

半導体集積回路のテスト方法とシステムとプログラム

【課題】ロット全体のテスト時間の短縮を図り、良品を不良と誤判定することを回避する方法、システム、プログラムの提供。

【解決手段】同一構成のLSI(被試験デバイス)のロットをテストするにあたり、一のLSIのファンクションテストを実行テストレート1で行い、前記ファンクションテストの結果がパスの場合、次のLSIのファンクションテストを実行テストレート1で行い、フェイルの場合、実行テストレート2で再び前記一のLSIの再テストを行い、再テストがパスした場合、実行テストレート1を現在値に加算テストレートを加算した値に更新して次のLSIのファンクションテストを前記更新した実行テストレート1で行い、前記一のLSIの実行テストレート1、2によるファンクションテストがいずれもフェイルの場合、前記一のLSIを不良と判定する。

(もっと読む)

101 - 110 / 4,543

[ Back to top ]