国際特許分類[G06F17/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 特定の機能に特に適合したデジタル計算またはデータ処理の装置または方法 (34,028) | 複合した数学演算 (567)

国際特許分類[G06F17/10]の下位に属する分類

方程式を解くためのもの (71)

フーリエ,ウオルシュまたは類似の領域変換 (124)

相関関数の計算 (22)

マトリックスまたはベクトルの計算 (123)

近似法による関数の計算,例.内挿または外挿法,平滑法,最小二乗法 (50)

統計データの算出のためのもの (73)

国際特許分類[G06F17/10]に分類される特許

81 - 90 / 104

マイクロプロセッサにおける効率の良い積和演算を実行するための装置及び方法

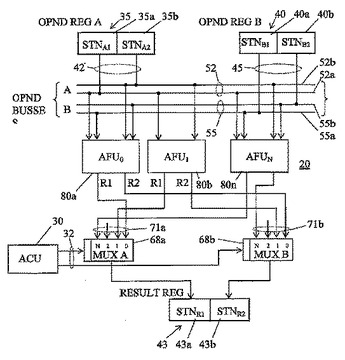

マイクロプロセッサにおける積和演算を実行するための装置であって、前記装置は、加算器及び乗算器及びデータの処理を実行するためのマルチプリアにて演算されたデータを受信するためのオペランド入力レジスタと、マイクロプロセッサへ送信するための結果出力ポートと、結果を格納するためのマルチフレクサと、前記装置へアキュムレータ内部の値を格納するためのアキュムレータキャッシュと、および前記装置の処理を制御するための制御回路と、からなる。  (もっと読む)

(もっと読む)

演算装置および演算方法

【課題】 より正確な浮動小数点を用いた演算を行うこと。

【解決手段】 乗算対象である第1の数と第2の数との積の演算を、二進浮動小数点を用いて行う演算装置であって、前記第1の数、前記第2の数、および、演算によって発生した数を、所定の桁数より下位の桁のビットを切り捨てるかあるいは切り上げることによって所定の桁数内の数として記憶する記憶部と、前記記憶部に記憶された前記第1の数を1のビットの最上位桁と最下位桁が分かれるように2つ以上の数に分離し、前記分離したそれぞれの数と前記第2の数の積の演算を行い、それぞれの当該演算結果を別々に前記記憶部に記憶させる処理部と、を有することを特徴とする。

(もっと読む)

モーダル区間プロセッサ

論理回路は、複数の算術関数ユニット(20)を使用して様々なモーダル区間計算値を算出する。マルチプレクサ(68)は、所望の計算値を記憶レジスタ(43)にゲート制御によって出力する。  (もっと読む)

(もっと読む)

積和演算器

【課題】 本発明は積和演算器に関し、演算データを複数個格納するレジスタのアドレスを自動生成、演算途中のデータの出力、オーバーフローの通知を可能とし、積和演算器の処理効率を向上し、再帰型のフィルタを容易に構成可能とすることを目的とする。

【解決手段】 係数レジスタ100 、データレジスタ110 、乗算器130 、加算器140 および外部装置との間でデータ転送を行なうデータバス120 を有する積和演算器において、データレジスタ110 のアドレスを外部から一々すべて指定することなく、外部からは最初に一度だけ該データレジスタ110 を示すアドレスを入力するだけでデータ格納アドレスを自動生成し、一連のデータを格納するデータ一括自動格納手段180 を有する。また、積和演算途中の中間結果データをデータレジスタ110 に自動的に格納し、再帰的な積和演算を行なう。

(もっと読む)

演算装置および並列演算装置

【課題】論理レベルの最適化ができ、また構成情報の増大を防止でき、集積回路としての面積効率の低下を防止でき、また、演算効率の向上を図れ、しかも低消費電力化を図れる演算装置を提供する。

【解決手段】構成情報に応じて係数入力C0I〜CkIを選択する第1の選択装置11と、構成情報に応じてデータ入力D0I〜DmIを選択する第2の選択装置12と、第1,第2の選択装置の出力信号を入力として、構成情報に応じた論理演算を行うALU14と、第1,第2の選択装置の出力信号を入力として構成情報に応じた演算を行うMAC15と、構成情報に応じてALU14とMAC15の出力信号のいずれかを選択する第4の選択装置16とを設ける。

(もっと読む)

信号推定方法、信号推定装置、信号推定プログラム及びその記録媒体

【課題】 伝達関数の次数を知ることなく観測信号のみから入力信号を正確に推定する。

【解決手段】 1入力2出力伝達系11のセンサ13,14の出力信号x1(n),x2(n)から信号源と各センサ間の伝達関数を推定し(40)、その推定値h^1(z),h^2(z)により第1、第2逆フィルタ係数を計算し(24)、第1、第2逆フィルタ係数を前段フィルタ31,32に設定し、出力信号x1(n),x2(n)をフィルタ31,32を通し、その出力を加算する。両伝達関数に共通の項を、h^1(z),h^2(z)により計算し(36)、この共通項により、後段フィルタ34で加算器33の出力を共通項成分を除去するようにフィルタ処理して、入力信号の推定値を得る。

(もっと読む)

圧縮ガロア域計算システム

圧縮ガロア域計算システムが提供される。該圧縮ガロア域計算システムは、第1及び第2の多項式をガロア域に渡る係数で乗算してそれらの積を得るための乗算器回路と、該積に累乗nの既約多項式を印加するためのガロア域線形変換器回路であって、折りたたまれた部分結果を提供するよう前記積における累乗n及びそれより大きい項に応答する部分結果発生器と、前記折りたたまれた部分結果及び積における累乗nよりも小さい項を圧縮して前記積の累乗nのガロア域変換を得るためのガロア域加算器とを含む前記ガロア域線形変換器回路と、を備える。  (もっと読む)

(もっと読む)

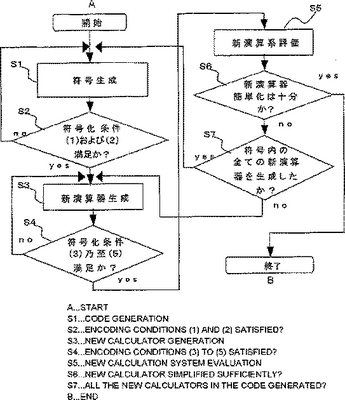

演算処理装置、演算処理装置設計方法および論理回路設計方法

純粋に論理的なアプローチにより、演算回路の素子数および遅延時間を削減した演算装置を実現するため、符号化による演算方式を具体的且つ効率的に論理設計し、符号化演算装置を提供する。演算系の演算器を必要があれば拡張し、基数rの論理関数として扱い、またr=2の時には写像の新たに表現である母関数を用い、符号化条件および論理式簡単化条件の下に新演算系を論理設計するか、または元演算系と新演算系の演算器の入出力関係のトポロジーを一致させることにより符号化演算方式の新演算系を設計する。符号化条件および論理式簡単化条件を満たす演算処理装置は、高速化・低消費電力を実現する。  (もっと読む)

(もっと読む)

信号の非相関化

本発明は、入力された信号の強い非相関化のための方法を提供し、以下のステップを含むことを特徴とする。

a)少なくとも1つの基本準ユニタリ行列を実行する遅延及び回転パラメータを定め、強い非相関化の程度の改善を得るように前記入力信号を出力信号に変換するように、前記入力信号を処理し、

b)前記強い非相関化の程度の改善を評価し、それが著しい場合には、前記出力信号を入力信号として指定し、前記ステップa)及び本ステップb)を繰り返し、

c)前記改善が著しくない場合には、前記出力信号を、広義に非相関化された信号として指定する。  (もっと読む)

(もっと読む)

データプロセッサ、データ処理方法及び演算処理プログラム

【課題】 逆余弦関数acos(x)に対しては1近傍の値を高精度に得る。

【解決手段】 データプロセッサ(1)は、データ処理ユニット(20)を有し、演算制御プログラムを実行するデータ処理ユニットは、前記演算制御プログラムに従って、入力xに対して関数acos(x)の値の計算を、多項式F(x)と定数Cを用いてacos(x)=F(1−x)*sqrt(C*(1−x))で行うとき、F(1−x)の多項式計算をホーナー法で行い、その最後の加算を留保して前記多項式F(x)の定数項の値cstと加算項の値αとを分けてストアし、更に、sqrt(C*(1−x))をニュートン法を用いて被加算項の値sq1と加算項の値εとに分けてストアし、(cst+α)*(sq1+ε)の展開式cst*sq1+α*sq1+cst*ε+α*εの全部又は先頭から一部を用いて、xの入力に対する関数acos(x)の値を求める演算を行う。

(もっと読む)

81 - 90 / 104

[ Back to top ]