国際特許分類[G06T1/60]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | メモリ管理 (517)

国際特許分類[G06T1/60]に分類される特許

121 - 130 / 517

フレームバッファ管理のシステム及び方法

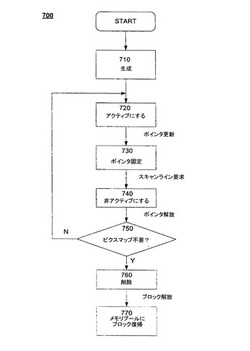

【課題】メモリ資源の最適な利用を実現する。

【解決手段】画像形成装置においてフレームバッファメモリ及びディスプレイリストメモリを有する単独のメモリプールのフレームバッファを管理する方法が開示されている。いくつかの実施形態においては、メモリプールから、少なくとも一つのピクスマップに割り当てられた等しいサイズのブロックを用いた画像に対応する前記ピクスマップを管理する方法は、前記画像のスキャンラインのうち少なくとも一つを求める要求を受け付けるステップと、前記メモリプールに使用可能なメモリブロックがある場合、前記スキャンラインのうち少なくとも一つを求める要求に対して前記メモリプールのブロックのうち少なくとも一つのブロックにポインタを固定するステップと、前記メモリプールに使用可能なメモリブロックがない場合、複数のメモリ解放方法のうち少なくとも一つを適用するステップと、を備える。

(もっと読む)

メモリアクセス制御回路及び画像処理装置

【課題】効率的なメモリアクセス動作を実現できるメモリアクセス制御回路を提供する。

【解決手段】メモリアクセス制御回路は、レジスタを第1の状態に設定して第1の一連のアドレスを送信し、レジスタを第2の状態に設定して第2の一連のアドレスを送信するアドレス送信部と、レジスタを第3の状態に設定して第1の一連のデータを受信して遅延させることなくデータ処理し、レジスタを第4の状態に設定して第2の一連のデータを受信して所定の遅延時間だけ遅延させてからデータ処理するデータ受信部と、アドレス送信部からの第1の一連のアドレスの送信終了に応答してレジスタの状態をバックアップ部に退避させるとともに第2の状態をレジスタに復帰させ、データ受信部による第1の一連のデータのデータ処理終了に応答して、前記所定の遅延時間を利用してレジスタの状態をバックアップ部に退避させるとともに第4の状態をレジスタに復帰させることを特徴とする。

(もっと読む)

画像処理装置及び画像形成装置

【課題】ディスクリプタ情報を使用するDMA転送において、画像処理パラメータを効率的に設定する。

【解決手段】一括転送用画像処理パラメータ記憶手段に設定済、あるいは未設定の画像処理パラメータと、ソース画像の画像処理に必要な画像処理パラメータとの差分を管理するパラメータ差分管理手段と、パラメータ差分管理手段の管理情報に基づいて、画像処理パターンを選択してソース画像処理パラメータ記憶手段に、画像処理パラメータを設定する画像処理パラメータ設定手段と、ソース画像処理パラメータ記憶手段に記憶された画像処理パラメータを、一括転送用画像処理パラメータ記憶手段に書き込む一括転送用画像処理パラメータ書込み手段と、ディスクリプタ情報に基づいて、画像処理部へとDMA転送を行うDMA転送手段と、を備える。

(もっと読む)

画像転送装置および画像転送方法

【課題】表示画面上の複数のコンテンツについて、複数の画像投射装置にそれぞれ所望のコンテンツを投射させること。

【解決手段】画像転送装置は、表示ディスプレイに表示されている複数のウィンドウW1〜W4の表示用画像データを生成し、ウィンドウ毎に確保されたRAM上の記憶領域A1〜A3に格納する。画像転送装置は、ユーザによって入力された指示に従って、各記憶領域A1〜A3と複数のプロジェクタPJ1〜PJ3とをそれぞれ対応付ける。画像転送装置は、各記憶領域A1〜A3に格納されているウィンドウW1〜W4の表示用画像データを関連付けられたプロジェクタPJ1〜PJ3に転送する。

(もっと読む)

画像処理装置

【課題】アドレス計算を必要とせず、命令メモリの面積を削減でき、かつ、レジスタ数を削減することができる画像処理装置を提供する。

【解決手段】画像処理装置1は、画像データを格納するデータメモリ13と、画像データのフレーム中におけるRPの位置を示す2次元アドレスを保持するRPレジスタ23と、フレームの幅及び高さに基づいて、RPレジスタ23に保持される2次元アドレスの制御を行うRP制御部22とを有する。また、画像処理装置1は、RPからの2次元相対位置を2個の即値の組により指定するフィールドを具備する命令コードに基づいて、データメモリ13から読み出し対象画素データを読み出す際に、2次元アドレスと、即値の組と、フレームの幅とに基づいて、読み出し対象画素データが格納されているアドレスを計算するアドレス計算ユニット21a〜21cとを有する。

(もっと読む)

画像処理プロセッサ

【課題】バッファ容量を可及的に削減した画像処理プロセッサを提供する。

【解決手段】デジタル映像信号が入力されてから画像処理が実行されるまでの遅延量を示す情報を有する命令を取得し、該遅延量と外部から入力された画素数のカウンタ値とに基づいて画素位置を算出し、画素位置が有効領域に位置する場合、取得した命令を実行し、画素位置が無効領域に位置する場合、取得した命令を実行しないように構成した。

(もっと読む)

演算回路

【課題】ルックアップテーブルを使用することによる演算処理の高速化を実現しながらも、ルックアップテーブルを記憶するために必要なメモリ容量を節約することのできる演算装置を提供する。

【解決手段】2n桁(n≧0の整数)の入力データに対する所定の演算結果が設定されたルックアップテーブル27と、前記入力データに基づいてルックアップテーブル27をアクセスするアドレス回路28を備えた演算回路26であって、アドレス回路28に、入力データをn桁の上位データと下位データに分割し、夫々を大小比較する比較回路281と、比較回路281による比較結果に基づいて、上位データと下位データを入れ替えてルックアップテーブル27をアクセスするスイッチ回路282を備えている。

(もっと読む)

半導体装置、グラフィクスコントローラ、及び情報処理方法

【課題】メモリアクセス効率を高めたグラフィックス描画装置を提供する。

【解決手段】グラフィックス描画装置は、複数のY座標値にそれぞれ対応する複数のスパンのデータを各々が含む複数個のポリゴン形状のデータが与えられ、複数個のポリゴン形状のスパンのデータのうちで同一のY座標値を有するスパンのデータを纏めて一連のスパンデータとして出力するスパン選択部と、スパン選択部が出力する一連のスパンデータの各スパンに対して各画素のデータを生成する画素データ生成部と、スパン選択部が出力する一連のスパンデータに対応する各画素のデータを格納するメモリアドレスを纏めてアクセスするメモリアクセス部とを含む。

(もっと読む)

画像補間処理装置

【課題】低コスト且つ低消費電力で画像補間処理をすることができる画像補間処理装置を提供する。

【解決手段】

入力画像データの垂直方向において互いに隣接する画素データを単位画素データ群として一時的に順次保持する画素データ保持部と、少なくとも3つの当該単位画素データ群を記憶できる画像記憶メモリと、を含み、当該画素データ保持部に保持されている単位画素データ群を当該画像記憶メモリに順次記書込むと共に当該画像記憶メモリに記憶されている少なくとも2つの単位画素データ群を同時に読み出す画像補間処理装置。

(もっと読む)

フィルタマトリクス生成装置およびこれを用いたフィルタ装置

【課題】 フィルタマトリクス生成装置を構成するマトリクス生成部とラインメモリ部間のリード、ライト動作を減少させ、省電力効果を高める。

【解決手段】 マトリクス生成部9は、メモリ要素ラインが複数段配列される。第1〜第N−1のラインメモリ部11〜15は、ライン毎の画像データを入力し、最下位段からライン移行させながら格納してマトリクスデータを生成する。第1〜第N−1のラインメモリ部11〜15は、ライン毎の画像データをラインバッファ11a〜15aに格納し、画像データの同一値を検出設定し、1ライン分が同一値であれば、この同一値をマトリクス生成部9のラインに格納制御する。第1〜第N−1のラインメモリ部11〜15は同一値を次段の第2〜第N−1ラインメモリ部13〜15に設定する。

(もっと読む)

121 - 130 / 517

[ Back to top ]