国際特許分類[G09G3/30]の内容

物理学 (1,541,580) | 教育;暗号方法;表示;広告;シール (131,780) | 静的手段を用いて可変情報を表示する表示装置の制御のための装置または回路 (71,488) | 陰極線管以外の可視的表示器にのみ関連した,制御装置または回路 (45,667) | マトリックス状に配置された個々の要素の組み合わせによりその集合を構成することによって多数の文字の集合,例.1頁,を表示するためのもの (44,823) | 制御された光源を用いるもの (7,255) | エレクトロルミネッセントパネルを用いるもの (4,686)

国際特許分類[G09G3/30]の下位に属する分類

半導体,例.ダイオード (361)

国際特許分類[G09G3/30]に分類される特許

981 - 990 / 4,325

ディスプレイ装置

【課題】本発明は、デュアル(dual)ディスプレイパネルを有するディスプレイ装置に関する。

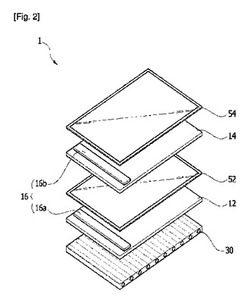

【課題手段】本発明によるディスプレイ装置は、 第1情報をディスプレイする第1ディスプレイパネルと、上記第1ディスプレイパネルと重なる重なり位置と上記第1ディスプレイパネルとの重なりが解除される重なり解除位置との間で往復移動し、第2情報をディスプレイする第2ディスプレイパネルと、上記第1ディスプレイパネル上に配置される第1タッチパネルと、上記第2ディスプレイパネルの上に配置されるか、或いは上記第2ディスプレイパネルの両面に一対で配置される第2タッチパネルと、上記第1および第2ディスプレイパネルの上記重なり位置と上記重なり解除位置の少なくともいずれか1つの位置に応じて、上記第1および第2タッチパネルの少なくともいずれか1つから感知された信号に基づいて上記第1および第2ディスプレイパネルの少なくともいずれか1つに駆動電圧を印加する制御部とを含むことを特徴とする。これにより、デュアルディスプレイパネルのうち少なくともいずれか1つがOLEDパネルとして用いられることにより、スリム化およびコンパクト化を実現することができる。

なお、デュアルディスプレイパネルにそれぞれタッチパネルを備え、各ディスプレイパネルを相互移動することが可能なように設けて、それぞれのディスプレイパネルに異なる情報を表示でき、これにより、製品の使用性を増大させることができる。

(もっと読む)

発光装置および電子機器

【課題】表示部の輝度を変化させる際におけるコントローラの負荷を抑制する。

【解決手段】本発明の発光装置10は、駆動トランジスタTdと、発光素子11と、発光制御トランジスタTsとを含む画素回路Pと、発光期間の時間長を示すデューティ比(発光期間データ)を、調光期間内の各単位期間Fについて記憶するメモリ30と、画素回路Pを駆動する駆動回路20とを含む。駆動回路20に含まれる発光制御回路26は、調光期間内の各単位期間Fにおいて、当該単位期間Fに対応したデューティ比をメモリ30から読み出し、当該デューティ比が示す発光期間の時間長だけハイレベルに維持される発光制御信号GELを生成して画素回路Pへ出力する。

(もっと読む)

表示装置

【課題】酸化物半導体トランジスタを用いる場合に、長寿命化や適切な画素回路動作を実現する。

【解決手段】酸化物半導体材料を用いたトランジスタを採用する画素回路において、駆動トランジスタやサンプリングトランジスタを、2つ以上のトランジスタが直列に接続されたマルチゲート構造(例えばダブルゲート構造)とする。酸化物半導体においてマルチゲート構造を用いることで、シングルゲート構造と同等のチャネル幅、チャネル長の電流供給能力を持たせる際に、酸素抜けが生ずる領域を狭め、チャネル材料からの酸素抜けを低減することができる。また酸化物半導体トランジスタのシングルゲート構造において生ずる恐れのある閾値補正、移動度補正の際の不適切な動作を解消できる。

(もっと読む)

表示装置および駆動制御方法

【課題】消費電力を低減することができるようにする。

【解決手段】ELパネル101の画素アレイ部111には、N×M個の画素121−(1,1)乃至121−(N,M)が行列状に配置されて構成されている。画素121−(N,M)は、サンプリング用トランジスタ31、駆動用トランジスタ32、蓄積容量33、発光素子34、発光素子容量34B、および補助容量35Aを有している。画素21では、補助容量35Aの一方の電極が、前段の画素121−(N,M−1)の電源線DSL−(M−1)と接続されている。本発明は、例えば、有機EL素子を用いた表示装置に適用できる。

(もっと読む)

レベルシフト回路、表示装置および電子機器

【課題】貫通電流を抑えつつ大振幅のレベル変換を実現可能なインバータ型のレベルシフト回路を提供する。

【解決手段】インバータ型のレベルシフト回路10において、初段のCMOSインバータ回路11のnチャネルトランジスタ112のサイズを、pチャネルトランジスタ111のサイズのa倍(例えば、100倍)以上の極端なサイズ差に設定する。このサイズ比により、貫通電流を抑えつつ、例えば0−3V振幅から0−12V振幅にレベル変換する場合のような大振幅のレベル変換を実現する。

(もっと読む)

電気光学装置、及びその駆動方法、並びに電子機器

【課題】 各単位回路に関する移動度補償の実行時間をばらつかせない。

【解決手段】電気光学装置は、駆動電流の大きさに応じた光量で発光する発光素子、発光素子に駆動電流を出力する駆動トランジスター、駆動トランジスター自身に前記駆動電流を流すか否かを司る第1トランジスター、及び、一端が駆動トランジスターのゲートに接続され他端がデータ線に接続されたデータ書込用トランジスター、を含む単位回路を複数備える。前記各種のトランジスターは、それぞれ、走査線に含まれる各配線に供給される制御信号によって制御されるが、移動度補償動作時において、これらのうちの第1トランジスターを導通状態とする際には、その制御信号として、ランプ波形を含む前記第1制御信号(GEL[i])が利用される。

(もっと読む)

EL表示装置及びその駆動方法

【課題】特性表示ムラのない画像表示を実現できるEL表示装置を提供する。

【解決手段】EL素子81に供給する電流を決定する駆動トランジスタ14と、駆動トランジスタ14のゲート電圧を保持するための容量Csとを具備し、容量Csの一方の第1の電極には、駆動トランジスタ14のゲート電極に接続され、容量Csの他方の第2の電極には、第1の電源と第2の電源が交互に接続され、駆動トランジスタ14にソース信号線10からの信号が印加される第1の期間には基準電圧の電源が接続され、駆動トランジスタ14がEL素子81に電流を供給する第2の期間においてELアノード電源が接続される。

(もっと読む)

画素回路の駆動方法、表示装置

【課題】画素毎の駆動トランジスタの閾値電圧変動具合の差を低減し、電流劣化の差による焼き付きの低減を実現する。

【解決手段】非発光期間と発光期間とから成る1サイクルの発光動作期間に、発光素子の発光動作を終了させた後、駆動トランジスタのゲートを所定電位に固定し、駆動トランジスタのドレイン・ソース間に駆動電圧を印加して、駆動トランジスタのゲート・ソース間電圧を初期化する。そして駆動トランジスタのゲート電位の固定を解除し、また駆動トランジスタのドレイン・ソース間への駆動電圧印加を終了させて、ゲート・ソース間電圧の初期化状態を維持する。その後、閾値補正等を行って、発光動作を行う。つまり非発光期間中の閾値補正に至る前の期間は、発光階調にかかわらず、ゲート・ソース間電圧が一定とされているようにする。

(もっと読む)

薄膜発光素子の駆動回路及び駆動方法

【課題】薄膜発光素子の寄生容量及び配線の寄生容量に起因する薄膜発光素子の輝度の低下を抑制する薄膜発光素子の駆動回路及び駆動方法を提供する。

【解決手段】薄膜発光素子101と、薄膜発光素子101に並列に接続された電荷蓄積手段102と、電荷蓄積手段102に供給する電荷量を、電圧によって制御する電荷供給手段103と、薄膜発光素子101のアノード及び電荷蓄積手段102と電荷供給手段103との間に接続され、電荷供給手段103から電荷蓄積手段102への電荷の供給を制御するスイッチング手段104と、薄膜発光素子101に接続され、薄膜発光素子101への電荷の供給を制御する逆バイアス電源105とを有することを特徴とする駆動回路。

(もっと読む)

表示装置、光検出動作の制御方法

【課題】画素外の光検出部による正確な光検出を実現し、焼き付き補正の適正化を図る。

【解決手段】画素回路に対して、光検出部を配置する。光検出部は、画素回路の発光素子からの光を検出する光センサを含み、該光センサによる光検出情報を光検出線に出力する検出信号出力回路が形成されている。そして出力された光検出情報に基づいて画素回路に与える信号値を補正する。ここで、光検出部が光検出動作を行わない期間には、光検出部内の回路の全ノードを同電位(Vcat)とし、光センサやトランジスタの電気特性変動が起こらないようにする。

(もっと読む)

981 - 990 / 4,325

[ Back to top ]