国際特許分類[H01G4/30]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | コンデンサ;電解型のコンデンサ,整流器,検波器,開閉装置,感光装置また感温装置 (21,977) | 固定コンデンサ;その製造方法 (8,165) | 積層型コンデンサ (2,251)

国際特許分類[H01G4/30]に分類される特許

31 - 40 / 2,251

積層セラミック電子部品及びその製造方法

【課題】本発明は、積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明は、複数の誘電体層が積層されたセラミック素体と、上記誘電体層の少なくとも一面に形成され、幅方向にずれて配置された複数の第1及び第2内部電極と、を含み、上記セラミック素体の一側面から上記第1内部電極の幅方向の先端までの距離をAとし、上記セラミック素体の一側面から上記第2内部電極の幅方向の先端までの距離をBとする際、上記AとBとの差異は、上記第1内部電極または第2内部電極の幅の10から14%である、積層セラミック電子部品を提供する。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、複数の誘電体層が積層されたセラミック素体と、上記複数の誘電体層に形成される複数の内部電極と、上記内部電極が形成されない誘電体層のマージン部に形成され、気孔率が10%以下であるマージン部誘電体層と、上記セラミック素体の外表面に形成される外部電極とを含んでよい。

(もっと読む)

積層セラミックコンデンサ

【課題】 高温負荷寿命に優れた積層セラミックコンデンサを提供する。

【解決手段】 誘電体層5はセラミック粒子11の焼結体からなるとともに、内部電極層7は金属とセラミック成分とから構成されており、セラミック粒子11は、コア部Cと、コア部Cの周囲を取り巻くシェル部Sとからなり、シェル部Sには少なくとも希土類元素(RE)が含まれており、セラミック粒子11のうち内部電極層7に接しているセラミック粒子11は、誘電体層5の厚み方向において、内部電極層7に接した側のシェル部Sの厚みt1が内部電極層7に接していない側よりも厚い。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】メッキ液の浸透が抑制されて信頼性に優れた積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明の積層セラミック電子部品は、セラミック本体と、上記セラミック本体の内部に積層配置された内部電極と、上記セラミック本体上に形成された第1外部電極層、上記第1外部電極層上に形成された第2外部電極層、上記第2外部電極層上に形成された第3外部電極層を含む外部電極とを含む。

(もっと読む)

積層セラミック電子部品の製造方法

【課題】本発明は積層セラミック電子部品の製造方法に関する。

【解決手段】本発明はチップ状のセラミック素体を設ける段階と、上記セラミック素体の外側に第1外部電極を形成する段階と、上記第1外部電極上に導電性金属を含む第2外部電極を形成する段階と、上記第2外部電極上に金属を含む半田ペーストを塗布して金属コーティング膜を形成する段階とを含む積層セラミック電子部品の製造方法を提供する。

本発明による積層セラミック電子部品の製造方法は、外部電極上に銅(Cu)またはニッケル(Ni)メッキ層を形成することで、メッキ液浸透または銅(Cu)外部電極の浸出(leaching)不良を防ぎ、信頼性に優れた積層セラミック電子部品を具現することができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、積層セラミック電子部品のセラミック素体の隅角部を介して不純物が内部電極に浸透することを防止できる積層セラミック電子部品及びその製造方法を提供する。

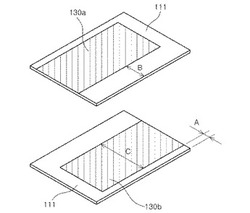

【解決手段】複数の誘電体層が積層されたセラミック素体と、セラミック素体の上下部に位置した誘電体層111上に形成され当該セラミック素体の一面から露出した部分の幅が内部に位置した部分の幅より小さい第1の内部電極133,134と、セラミック素体の中間部に位置した誘電体層111上に形成され、当該セラミック素体の一面から露出した部分の幅が内部に位置した部分の幅と同一の第2の内部電極131,132と、を含む。

(もっと読む)

積層セラミックキャパシタの製造方法

【課題】本発明は、積層セラミックキャパシタの製造方法に関する。

【解決手段】本発明は、内部電極が印刷されたセラミックグリーンシートを積層してセラミック積層体を形成する段階と、上記セラミック積層体に熱圧搾を加える段階と、上記セラミック積層体を切断する段階と、上記セラミック積層体にスラリーを浸透させる段階と、上記セラミック積層体に浸透されたスラリーを乾燥する段階と、を含むことができる。本発明によると、積層セラミックキャパシタの製造工程時に発生するクラック(crack)が除去されて信頼性に優れた積層セラミックキャパシタを製作することができる。

(もっと読む)

静電容量素子、及び共振回路

【課題】静電容量素子において、焼成時に発生する残留応力を利用することで誘電率を向上させ、静電容量を増大する。

【解決手段】容量素子(可変容量素子1)は、誘電体層と、誘電体層を挟んで形成される少なくとも一対の内部電極10とを備える容量素子本体2と、容量素子本体2の側面に形成され、内部電極10に電気的に接続される外部端子3,4とを備える。そして、誘電体層5及び内部電極の線膨張係数の違いに起因して発生する応力が、誘電体層5と誘電体層5を挟む一対の内部電極10とで構成されるコンデンサCの中心に集中するように構成されている。

(もっと読む)

積層電子部品の製造方法およびその方法に用いる積層ユニットの製造方法

【課題】いわゆる多層塗布工法を用いて積層電子部品を製造する際に、シートアタック現象が発生せず、結果として得られる電子部品のショート不良率が少ない積層電子部品の製造方法と、その製造方法に用いられる積層ユニットと、その製造方法を提供することである。

【解決手段】第1グリーンシート10aと、第1グリーンシート10aの上に形成された第1電極パターン12aと、第1電極パターン12aが形成された第1グリーンシート10aの表面に形成された第2グリーンシート10bと、第2グリーンシート10bの上に形成された第2電極パターン12bと、を有する積層ユニットである。第1グリーンシート10aに含まれるバインダ樹脂が、第1ブチラール系樹脂であり、第2グリーンシート10bに含まれるバインダ樹脂が、前記第1ブチラール系樹脂とは異なる第2ブチラール系樹脂である。

(もっと読む)

静電容量素子、及び共振回路

【課題】電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、電気的特性を向上させることを目的とする。また、その静電容量素子を用いることにより、信頼性に優れた共振回路を提供することを目的する。

【解決手段】誘電体層3と、誘電体層3を介して積層され、静電容量をなす電極本体の中心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサにより容量素子本体2を構成する。この容量素子本体2では、該2つ以上のコンデンサが内部電極の積層方向に直列接続される。そして、容量素子本体2の側面に、静電容量をなす電極本体に電気的に接続された外部端子20〜23を形成する。

(もっと読む)

31 - 40 / 2,251

[ Back to top ]