国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

1,231 - 1,240 / 6,199

炭化珪素半導体装置

【課題】工程数を増やすことなく特性バラツキを抑えた炭化珪素半導体装置を製造することが困難であるという問題があった。

【解決手段】本発明にかかる炭化珪素半導体装置は、第1導電型の炭化珪素半導体基板であるN型SiC基板1およびN型SiCエピタキシャル層2と、N型SiCエピタキシャル層2の表面に間欠的に形成された複数の凹み部10と、複数の凹み部10の各底面においてN型SiCエピタキシャル層2に形成された、第2導電型の半導体層であるP型領域5と、N型SiCエピタキシャル層2の表面上に選択的に形成されたショットキー電極6とを備え、複数の凹み部10の深さは、すべて等しい。

(もっと読む)

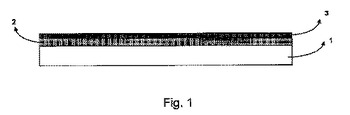

光電子デバイス用多層金属電極

本発明は、基板(1)と、少なくとも1つの極薄金属膜(3)と接触する導電膜(2)からなる層状構造部と、を備え、2つの膜(2,3)が異なる材料からなり、前記導電膜(2)がCu、Au、Ag、Alから選択され、前記極薄金属膜(3)がNi、Cr、Ti、Pt、Ag、Au、Alおよびこれらの混合物から選択される電極に関する。電極は、光電子デバイスに特に有益であり、良好な導電率、透過率および安定性を示す。  (もっと読む)

(もっと読む)

有機デバイスの製造方法

本発明は、有機デバイスの製造方法に関し、下記のステップを含む。(i)電気コンタクト構造(4)および絶縁部(3)を備えた表面を有する基板(1)を用意するステップ。(ii)第1仮保護層(9)を、前記電気コンタクト構造(4)の幾つかまたは全ての上に設けるステップ。(iii)第1表面改質層(6)を絶縁部(3)の上に設けること、及び/又は、第3表面改質層(10)を、ステップ(ii)で保護されていない前記電気コンタクト構造(4)の上に設けるステップ。(iv)第1仮保護層(9)を除去するステップ。(v)第2表面改質層(5)を、ステップ(ii)で保護された電気コンタクト構造の上に設けるステップ。(vi)前記第1表面改質層(6)を、ステップ(iii)で設けていなければ、絶縁部(3)の上に設けるステップ。(vii)有機半導体層(7)を、前記第1表面改質層(6)の少なくとも一部の上に、および前記第2表面改質層(5)の上に、そして、もし存在すれば、前記第3表面改質層(10)の上に設けて、これにより前記有機デバイスを得るステップ。  (もっと読む)

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

曲線状のゲート酸化物プロファイルを有するスプリットゲート半導体素子

スプリットゲート半導体素子は、第1の電極領域及び第2の電極領域を有するトレンチゲートを含む。前記第1の電極領域及び前記第2の電極領域は、ゲート酸化物層及び隣接誘電層によって相互に分離される。前記ゲート酸化物層と前記誘電層との間の境界は曲線状となっており、これにより、前記ゲート酸化物層が前記トレンチの側壁と出合う場所である鋭角部が回避される。 (もっと読む)

ITOスパッタリングターゲットおよびその製造方法

【解決手段】走査型電子顕微鏡を用いて倍率1000倍で観察して得られた組織画像の中から任意に20μm×20μmの領域を30個選択し、波長分散型電子線マイクロアナライザーにて各領域におけるInおよびSnの質量組成(質量%)を分析し、Sn/(In+Sn)比を求め、この比から換算して得られた30個のSnO2組成の平均である平均

組成xと、前記30個のSnO2組成の標準偏差σとが、2≦x/σ≦6の関係を満足す

ることを特徴とするITOスパッタリングターゲット。

【効果】本発明のITOスパッタリングターゲットは、圧縮強さが大きく、高パワーを負荷してスパッタリングを行っても割れが発生することが少なく、アーキングおよびノジュールの発生も抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】Ruバリア上にダイレクトにめっきするプロセスにおいて、ボイドフリーの埋め込みを実現する半導体装置の製造方法を提供する。

【解決手段】半導体装置100の製造方法は、半導体基板上の絶縁膜101に凹部102を形成する工程(a)と、凹部102の側壁及び底部を覆うようにバリアメタル膜103を形成する工程(b)と、第1の電界めっき処理により、バリアメタル膜103の表面に沿ってコンフォーマルな第1の導電膜104を形成する工程(c)と、工程(c)の後、第2の電界めっき処理により、凹部内に第2の導電膜105を形成する工程(d)とを有する

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】n型SiC領域とp型SiC領域との両方と接触可能であり、かつ酸化による接触抵抗の増加を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、炭化珪素からなるn−SiC層12を準備する工程と、n−SiC層12の主表面上にソースコンタクト電極16を形成する工程とを備えるMOSFET1の製造方法である。ソースコンタクト電極16を形成する工程は、ソースコンタクト電極16となるべき導電体層をn−SiC層12の主表面上に形成する工程と、導電体層をソースコンタクト電極16とするため熱処理する工程とを含む。熱処理する工程の後、ソースコンタクト電極16の表面を酸素含有雰囲気に曝露するときのソースコンタクト電極16の温度を100℃以下にする。ソースコンタクト電極16を形成する工程の後、表面電極パッド27を形成する工程の前に、上記ソースコンタクト電極16の一方の主面上に形成された高抵抗層を除去する工程を含むことがより好ましい。

(もっと読む)

1,231 - 1,240 / 6,199

[ Back to top ]