国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

1,131 - 1,140 / 6,199

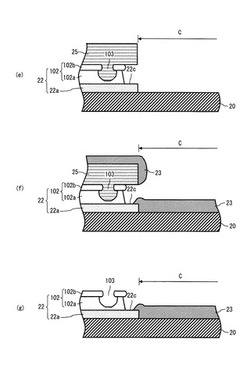

パターン形成方法、及び半導体装置の製造方法

【課題】下地の性能を犠牲にすることなく、リフトオフ層が下地から剥離することを防止できるパターン形成方法、及び半導体装置の製造方法を提供すること。

【解決手段】本発明にかかるパターン形成方法は、基板上にカバー絶縁膜22を形成し、第1のレジストパターン104をマスクとして、金属膜パターン形成領域を取り囲むようカバー絶縁膜22に凹部103を形成する工程と、凹部103内に入り込むよう、カバー絶縁膜22上にリフトオフ層となる第2のレジストパターン25を形成する工程と、第2のレジストパターン25をマスクとして、金属膜パターン形成領域のカバー絶縁膜22に開口部を形成する工程と、第2のレジストパターン25の上から基板表面に金属膜を成膜し、第2のレジストパターン25とともに第2のレジストパターン25上の金属膜を除去して金属膜パターンを形成する工程とを備えるものである。

(もっと読む)

半導体発光素子の製造方法および半導体積層基板

【課題】1枚の基板から得られる複数の半導体発光素子の構造のばらつきを抑制することのできる半導体発光素子の製造方法および半導体積層基板を提供する。

【解決手段】サファイアウエハWAの一方の面に、逐次露光方式を用いて凸部および平面を有する凸部形成領域SAと、位置決め用のマークMを有するマーク形成領域MAとを形成する。その後、サファイアウエハWAの一方の面にIII族窒化物半導体層を積層した半導体積層基板を作成し、マークMの形成位置の読み取り結果に基づいて、逐次露光方式を用いて複数の半導体発光素子に対応した電極構造を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供し得る半導体装置の製造方法を提供することにある。

【解決手段】第2の応力膜44に対する第2の絶縁膜48の選択比が第1の値である第1の条件でエッチングを行うことにより、第1のコンタクトホール60eを少なくとも第2の応力膜の途中まで開口し、第2のコンタクトホールを少なくとも第2の絶縁膜の途中まで開口するエッチング工程と、第2の応力膜に対する第2の絶縁膜の選択比が第1の値より大きい第2の値である第2の条件でエッチングを行うことにより、第1のコンタクトホールにより第2の応力膜44を貫き、第2のコンタクトホールにより第2の絶縁膜及び第1の絶縁膜40を貫くエッチング工程と、更なるエッチングを行い、第1のコンタクトホールをゲート配線20まで到達させ、第2のコンタクトホールをトランジスタのソース/ドレインまで到達させる第3のエッチング工程とを有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

ショットキーダイオードと製造方法と製造装置

【課題】不純物高濃度層2と不純物低濃度層4が積層されており、不純物低濃度層4内に欠陥6a,6b等が形成されている半導体基板5から、リーク電流が流れにくいショットキーダイオード15を製造する。

【解決手段】 不純物低濃度層4に欠陥6a,6bが存在する部位にのみ、絶縁層8a,8bを形成し、その上にショットキー電極12を形成する。欠陥6a,6bを除去しないことから簡単な製造工程を採用できる。絶縁層8a,8bで絶縁することから、欠陥6a,6bがあってもリーク電流が流れない。特性のすぐれたショットキーダイオード15を安価に製造することが可能となる。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

成膜装置、成膜方法及び記憶媒体

【課題】真空容器内にて反応ガスによりチタンナイトライド膜を形成するにあたり、当該チタンナイトライド膜を速やかに成膜すると共に、表面形状が平滑なチタンナイトライド膜を得ること。

【解決手段】チタンナイトライド膜の成膜処理を行う時に、回転テーブル2と各ガスノズル31、32、41、42とを100rpm以上で相対的に回転させることによって、反応ガスの供給サイクル(反応生成物の成膜サイクル)を高速で行うことができるので、薄膜を速やかに形成することができ、またサイクル間の時間が極めて短いので、基板の表面に生成した反応生成物の結晶化による粒子径の粗大化が進行する前に次の反応生成物の層を上層側に積層して平滑な表面を得ることができる。

(もっと読む)

マスクの製造方法、及び半導体装置の製造方法

【課題】開孔径が均一で開孔径の制御が容易な、微細化に適した開孔パターンを有するマスクを製造する。

【解決手段】第1及び第2のマスク層内に開孔を設ける。この後、第1のマスク層内の開孔の径よりも第2のマスク層内の開孔の径を、Xの量だけ大きくする。この後、第2のマスク層内の開孔内にマスク材料を形成することによって第2のマスク層内の開孔内に、Xの径の空洞部を形成する。この空洞部を開孔として有する第2のマスク層及びマスク材料を、マスクとして形成する。

(もっと読む)

Cu膜の製造方法

【課題】Cuのセルフイオンスパッタ法を適用する場合において、プラズマ状態を安定させて長時間にわたって自己維持放電を持続させることを可能にしたCuスパッタリングターゲットが求められている。

【解決手段】高純度Cuからなるスパッタリングターゲットを用い、Cuのセルフイオンスパッタ法によりCu膜を製造するCu膜の製造方法であって、前記高純度CuはAgおよびAuから選ばれる少なくとも1種の元素を含有し、かつ前記AgおよびAuの合計含有量が0.005〜500ppmの範囲であり、前記AgおよびAuから選ばれる少なくとも1種の元素の含有量のバラツキがターゲット全体として±30%以内である。

(もっと読む)

1,131 - 1,140 / 6,199

[ Back to top ]