国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

1,151 - 1,160 / 6,199

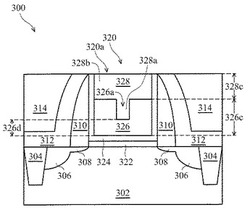

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合に、更に低コンタクト抵抗を確保することができる表示装置用Al合金膜を提供する。

【解決手段】本発明のAl合金膜は、表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Ni:0.2〜1.0原子%、Cu:0.2〜0.8原子%およびTiを0.05〜0.5原子%含有するものであるところに特徴を有する。

(もっと読む)

半導体を含む金属材料の形成方法

【課題】シリコンを含有する半導体領域及びゲルマニウムを含有する半導体領域を含む基板から、ニッケルシリサイド及びニッケルジャーマナイドの共集積化を行うに際し、金属系材料の間で短絡の危険なしに、実装が単純かつ容易な金属系材料の形成方法を提供する。

【解決手段】第1半導体材料から作られた領域と、誘電体材料から作られたパターンによって分離されたゲルマニウムを含む第2半導体材料から作られた領域と、を含む基板を準備し、金属層を堆積し(F2)、第1熱処理(F3)を行うことを含む。金属層は、第1半導体材料と、ゲルマニウムを含む第2半導体材料と、反応して、それぞれ、第1金属系材料と、ゲルマニウムを含有する第2金属系材料と、を形成する。第1熱処理(F3)は、0.01%〜5%の酸素量を含む雰囲気中で行われる。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

配線構造の製造方法及び配線構造

【課題】本発明は、簡素な工程で配線構造を形成することができ、簡素な構成で自由度の高い配線の取り出しが可能な配線構造の製造方法及び配線構造を提供することを目的とする。

【解決手段】接合界面に電荷蓄積が発生する異種材料を積層して積層体を形成し、該積層体の接合界面に2次元電子ガス層を形成する2次元電子ガス層形成工程と、

該2次元電子ガス層を選択的に加熱して該2次元電子ガス層に非導電性領域を選択的に形成し、非加熱の導電性領域とで所定の配線構造を形成する選択的加熱工程と、を含むことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

スパッタリングターゲット及びその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体素子の製造方法

【課題】簡単な工程設備を用いて短い工程時間内に半導体素子のビアを形成できる半導体素子の製造方法を提供すること。

【解決手段】基板101に絶縁膜107と拡散防止膜109で内壁を被覆したビアホール105を形成する。荷電された金属粒子113を、電気力又は磁気力を利用して移動させて、このホールを金属粒子で充填する。ビアホールの下部から上方へ充填されるので、内部に空隙が発生することを抑制できる。従来技術による銅電気メッキ方式と比較すると、非常に短時間内に大きくて深いビアホールを金属粒子で充填できるため、シリコン貫通ビア(TSV)の工程コスト、及び工程時間を短縮することが出来る。また、従来技術の樹脂成分が多く含まれているメタルペーストを用いる乾式充填方式と比較すると、荷電された金属粒子を用いることで、より密なTSV金属配線を形成できる。

(もっと読む)

グラフェン構造体、グラフェン構造体の製造方法、及び電子デバイス

【課題】グラフェンを高精度でパターニングすることができ、これにより、グラフェンを用いた電子デバイス要素及び電子デバイスの精細加工が可能であり、製造コストを格段に低減することが可能なグラフェン構造体及びその製造方法等を提供する。

【解決手段】基板上にレジスト膜を精度よくパターニングし、そのレジスト膜の開口内に親水化膜を形成した後、GOが親水性を有することを利用して、親水化膜の部分にのみ、GOを選択的に化学的に結合させて固定化し、更にそのGOを還元して親水化膜の部分にのみグラフェンが選択的に固定化されたグラフェン構造体を得る。このように、グラフェン構造体は、基板上にグラフェンが設けられてなり、且つ、基板における親水処理の部位とグラフェン、及び/又は、基板における疎水処理の部位以外の部位とグラフェンとの間に、親水処理による結合が形成されたものである。

(もっと読む)

1,151 - 1,160 / 6,199

[ Back to top ]