国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

1,191 - 1,200 / 6,199

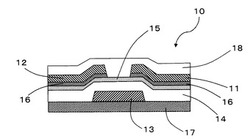

酸化物半導体を用いた薄膜トランジスタおよびその製造方法

【課題】オフ特性およびキャリア移動度に優れた、高品質の、酸化物半導体を用いた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、ドレイン電極と、ゲート電極と、ゲート絶縁膜と、酸化物半導体からなる活性層とを備えてなる。そして、活性層とソース電極の間および活性層とドレイン電極の間には、炭素製のバッファ層が設けられてなる。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

非対称スペーサをゲートとして備えるLDMOSトランジスタ

【課題】本発明は、横方向拡散金属酸化物半導体(LDMOS)トランジスタと、これを製造する方法を提供する。

【解決手段】LDMOSトランジスタはp型基板上に形成されたn型エピタキシャル層と、LDMOSトランジスタのゲートとして機能する非対称導体スペーサとを備える。LDMOSトランジスタはまた、非対称導体スペーサの両側のソース領域及びドレイン領域と、イオン注入を非対称導体スペーサに行うことで形成されたチャネル領域とを備える。非対称導体スペーサの高さはソース領域からドレイン領域に向かって増加する。チャネル領域は、基本的に完全に非対称導体スペーサの下に存在し、従来技術のLDMOSトランジスタのチャネル領域の長さよりも短い長さを有する。本発明のLDMOSトランジスタはまた、当該トランジスタの活性領域を囲むフィールド酸化物層と、非対称導体スペーサをn型エピタキシャル層から絶縁する薄い誘電体層とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】製造工程を簡略化しつつソース電極及びドレイン電極の導電性を向上させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、基板101上にゲート電極103を形成する工程と、ゲート電極103上にゲート絶縁層104を形成する工程と、ゲート絶縁層104上にアモルファスシリコン層105を形成する工程と、アモルファスシリコン層105上にアルミニウム層111を形成し、アルミニウム層111上にモリブデンタングステン層112を形成し、アルミニウム層111及びモリブデンタングステン層112を少なくとも含む積層体から構成されるソース電極109及びドレイン電極110を形成する工程と、ソース電極109及びドレイン電極110をマスクとしアモルファスシリコン層105にレーザを照射することでアモルファスシリコン層105の一部を結晶化させチャネル領域を形成する工程とを含む。

(もっと読む)

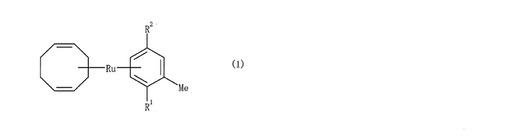

化学気相成長用原料及びルテニウム化合物

【課題】熱安定性を向上させた(1,5−シクロオクタジエン)(η6−アレーン)ルテニウム化合物を含有してなる化学気相成長用原料を提供すること。また、室温域で液体の(1,5−シクロオクタジエン)(η6−アレーン)ルテニウム化合物を含有してなる化学気相成長用原料を提供すること。

【解決手段】下記一般式(1)で表される(1,5−シクロオクタジエン)(η6−アレーン)ルテニウム化合物を化学気相成長用原料として用いる。

(式中、R1は、水素原子又はメチル基を表し、R2は、R1が水素原子の場合は、メチル基又はエチル基を表し、R1がメチル基の場合は、メチル基を表す。)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】pチャネルトランジスタ及びnチャネルトランジスタの閾値電圧を共に低減できるCMISトランジスタを有する半導体装置を提供する。

【解決手段】pチャネルトランジスタは、半導体基板100における第1の領域上に形成された第1のゲート構造150Aと、第1のゲート構造150Aの側壁上に形成された第1のスペーサ構造とを有する。nチャネルトランジスタは、半導体基板100における第2の領域上に形成された第2のゲート構造150Bと、第2のゲート構造150Bの側壁上に形成された第2のスペーサ構造とを有する。第1のスペーサ構造における第1のゲート構造150Aの側壁との接触部分の含有酸素濃度は、第2のスペーサ構造における第2のゲート構造150Bの側壁との接触部分の含有酸素濃度よりも高い。

(もっと読む)

電力変換モジュール及びそれを用いた電力変換装置あるいはモータ駆動装置あるいは空気調和機

【課題】インバータ等に適用される半導体デバイスは、寄生ダイオードにより誘導負荷からの還流電流を通流する場合、ダイオードの順方向電圧による損失が大きくなることが懸念され、また双方向デバイスを適用した場合には、2つのゲート端子を駆動する必要があり、制御の複雑化、かつ高コストになるという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、第一ソース端子4、第二ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、第一ゲート端子2あるいは第二ゲート端子3の何れか一方を常時オン状態となるように制御し、還流電流を流す経路を確保しつつ、ダイオード損失を低減し、かつ2つのゲート信号数を減らし、簡易な回路構成、かつ低コストに電源変換回路を実現することができる。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

1,191 - 1,200 / 6,199

[ Back to top ]