国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

1,271 - 1,280 / 6,199

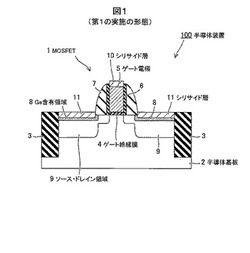

半導体装置およびその製造方法

【課題】より高い耐熱性を有するシリサイド層を備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上にゲート絶縁膜4を介してゲート電極5を形成する工程と、半導体基板2上のゲート電極5の両側に、Ge含有領域8を形成する工程と、半導体基板2およびGe含有領域8のゲート電極5の両側の領域中に、ソース・ドレイン領域9を形成する工程と、Ge含有領域8上に、濃度5原子%以上のPdを含む金属シリサイドからなるシリサイド層11を形成する工程と、シリサイド層11を形成した後、半導体基板2に650〜750℃の熱処理を施す工程と、を含む。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタを用いた表示装置及び薄膜トランジスタの製造方法

【課題】工程数の増大を引き起こさずに、遮光層で囲まれた薄膜トランジスタと同等以上の遮光能力を有する薄膜トランジスタおよびそれを用いた表示装置を提供する。

【解決手段】第1のゲート電極2と、第1のゲート電極2を覆う第1のゲート絶縁層3と、第1のゲート絶縁層3の上の半導体層6と、半導体層6の上の第2のゲート絶縁層7と、第2のゲート絶縁層7の上の第2のゲート電極8と、半導体層6に電気的に接続されたドレイン電極5及びソース電極4を有する薄膜トランジスタにおいて、半導体層6がZn、Ga、In、Snのうち少なくとも1種以上を含む非晶質酸化物半導体であり、第1のゲート電極2が下方から半導体層6への光の入射を遮り、第2のゲート電極8が上方から半導体層6への光の入射を遮り、第2のゲート電極8は第1のゲート絶縁層3及び第2のゲート絶縁層7を貫通して第1のゲート電極2と電気的に接続され、少なくとも一方の側方から半導体層6に入射する光を遮る。

(もっと読む)

電極形成方法および電極形成装置

【課題】基板上に電極を形成する方法および装置において、低コストで、しかも優れた生産性で、幅の異なる電極を形成することのできる技術を提供する。

【解決手段】光硬化性樹脂を含む塗布液と吐出する吐出ノズル部と、吐出された塗布液に光照射して硬化させる光照射部とを2組設け、それぞれの照射条件を異ならせる。第1ヘッド部5に設けた吐出ノズル部52と光照射部53との間隔が、第2ヘッド部7に設けた吐出ノズル部72と光照射部73との間隔よりも小さい。このため、第1ヘッド部5では、塗布液が基板Wに塗布されてから光照射されるまでの時間が短く、幅が狭くて高さのある電極が形成される。一方、第2ヘッド部7では、塗布液が基板Wに塗布されてから光照射されるまでの時間が長いので塗布液が広がり、より幅広の電極が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド領域と非シリサイド領域が混在する半導体装置において、シリサイド領域の狭ゲート電極間にシリサイドプロテクション膜残りによるシリサイド形成不良を防止し、非シリサイド領域において確実にシリサイド化反応を防止する製造方法を提供する。

【解決手段】同一の半導体基板のシリサイド領域Aと非シリサイド領域Bを備える半導体装置の製造方法は、半導体基板101上の全面にゲート電極103を覆うように堆積した第1のシリコン酸化膜104をエッチングして、ゲート電極103の側面に断面I字状のオフセットサイドウォール104aをシリサイド領域Aに形成し、シリサイドプロテクション膜104bを非シリサイド領域Bに形成する。続いて、内側サイドウォール106、外側サイドウォール107、及び不純物拡散層108を形成した後、シリサイド領域Aのゲート電極103及び不純物拡散層108上に金属シリサイド層110を形成する。

(もっと読む)

スパッタリングターゲット、透明導電性酸化物、およびスパッタリングターゲットの製造方法

【課題】スパッタリング法により透明導電性酸化物を成膜する際のノジュールの発生を抑制し、安定にスパッタリングを行うことのできるターゲット、このようなターゲットからなる透明導電性酸化物、およびこのようなターゲットの製造方法を提供する。

【解決手段】In/(In+Zn)で表わされる原子比が、0.75〜0.97の範囲であるとともに、In2O3 (ZnO)m(ただし、mは2〜20の整数である。)で表される六方晶層状化合物を含有し、かつ、該六方晶層状化合物の結晶粒径が5μm以下の値であるスパッタリングターゲットから成膜してなる透明導電性酸化物。

(もっと読む)

半導体装置とその製造方法

【課題】 電極と半導体基板の間の順方向特性を改善する技術を提供する。

【解決手段】 半導体装置100は、表面の少なくとも一部に複数の突出部6aが形成されている突出部領域6を有する半導体基板14と、複数の突出部6aの側面6dに形成されている電流方向異方性材料4と、突出部領域6上に形成されている電極2を備える。電流方向異方性材料4は平面方向のキャリア移動度が高いので、電極2と半導体基板14の間の順方向特性を改善することができる。

(もっと読む)

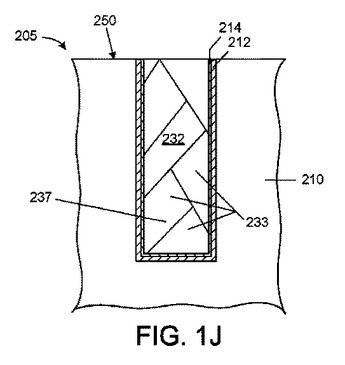

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】薄膜中への不純物の取り込みを抑制し、膜質を向上させる。

【解決手段】基板を処理する処理室内にハロゲン含有ガスを供給するハロゲン含有ガス供給工程と、処理室内にハロゲン含有ガスとは異なる原料ガスを供給する原料ガス供給工程と、処理室内に電子ビームを供給して基板近傍で原料ガスの活性種を生成する原料ガス活性種生成工程と、を有し、原料ガスの活性種とハロゲン含有ガスとを反応させて基板上に薄膜を形成する薄膜形成工程と、処理室内に水素含有ガスを供給する水素含有ガス工程と、処理室内に電子ビームを供給して基板近傍で水素含有ガスの活性種を生成する水素活性種生成工程と、を有し、水素含有ガスの活性種と、基板上に形成した薄膜中のハロゲン元素と、を反応させて基板上に形成した薄膜を改質する薄膜改質工程と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

1,271 - 1,280 / 6,199

[ Back to top ]