国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

331 - 340 / 6,199

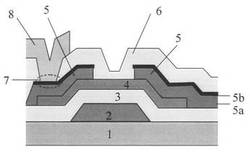

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】工程数が少なく生産性を向上する窒化物半導体発光素子の製造方法を提供する。

【解決手段】まず、パッド電極層形成工程S11で、窒化物半導体発光素子構造上に、n側パッド電極およびp側パッド電極となるパッド電極層を形成し、レジストパターン形成工程S12で、パッド電極層上に、n側パッド電極およびp側パッド電極を形成する領域を被覆するレジストパターンを形成する。次に、パッド電極層エッチング工程S13で、このレジストパターンをマスクとして、パッド電極層をエッチングしてn側パッド電極およびp側パッド電極を形成する。続いて、このレジストパターンを除去せずに、保護層形成工程S14で、窒化物半導体発光素子構造の表面およびレジストパターン上に絶縁性の保護層を形成した後に、レジストパターン除去工程S15で、レジストパターンを除去する。

(もっと読む)

半導体装置

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置を提供することを目的

の一とする。

【解決手段】13族元素および酸素を含む第1の絶縁膜と、第1の絶縁膜と一部が接する

酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と

、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜とゲート電極の間の、酸化物

半導体膜と一部が接する第2の絶縁膜と、を有する半導体装置である。また、13族元素

および酸素を含む第1の絶縁膜には、化学量論的組成比より酸素が多い領域が含まれる構

成とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】ゲート絶縁層と、ゲート絶縁層の一方の面に接する第1のゲート電極と、ゲート絶縁層の他方の面に接し、第1のゲート電極と重畳する領域に設けられた酸化物半導体層と、酸化物半導体層と接するソース電極、ドレイン電極、及び酸化物絶縁層と、の積層構造を有し、酸化物半導体層の窒素濃度は2×1019atoms/cm3以下であり、ソース電極及びドレイン電極は、タングステン、白金及びモリブデンのいずれか一又は複数を含む半導体装置を提供する。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

331 - 340 / 6,199

[ Back to top ]